基于电感源极退化技术的高线性混频器设计*

张雷鸣,刘 博,张金灿

(河南科技大学 电气工程学院,河南 洛阳 471023)

基于电感源极退化技术的高线性混频器设计*

张雷鸣,刘博,张金灿

(河南科技大学 电气工程学院,河南 洛阳 471023)

基于电感源极退化技术设计了一款新颖的高线性度正反馈跨导放大器,并且将该跨导放大器应用于折叠结构式混频器当中。通过抵消反相器和辅助放大器之间的三阶跨导分量,改善了其线性度。电路采用TSMC 0.13 μm CMOS工艺进行设计与仿真,完成了版图设计与流片。与传统结构相比,该混频器的输入三阶交调点IIP3高达8.6 dBm,噪声系数为10.9 dB,增益高达14 dB,并且取得了更优的归一化FOM指标。

线性度;跨导放大器;混频器;电感源极退化技术

0 引言

随着工艺技术的发展,CMOS器件的尺寸以及功耗越来越小。为了便于携带,要求用于移动设备中的射频集成电路具有较低的功耗。然而,由于线性度和功耗两者之间的相互制约,高线性度设计逐渐成为目前CMOS射频集成电路领域研究的重点和热点[1-4]。

一般而言,由于混频器的输入信号功率远大于低噪声放大器的输入信号功率,因此射频接收机的线性度主要受限于混频器,并使混频器的线性度成为其较为重要的考量指标。目前,关于改进混频器线性度的技术已经有了较多的研究成果。文献[5]通过在晶体管本征栅源电容并联电容,降低了三阶交调分量IMD3的幅度。虽然该技术改进了三阶交调点IIP3,但是额外的电容限制了电路的工作频率。文献[6]通过在开关级引入LC滤波电路,并利用滤波器降低了在本振频率处开关级晶体管寄生电容的影响,实现了开关级线性度的提高,但改善非常有限。

本文采用一种全新的线性度提高技术,通过在跨导放大器级处引入电感源极退化方式的正反馈补偿技术,提高整个混频器电路的线性度。同时,通过引入电流注入技术[7-10],改善电路的噪声和增益性能。该混频器采用TSMC 0.13 μm CMOS工艺设计,运用ADS2009U软件对其进行仿真验证,并进行了版图设计。仿真结果表明,该混频器在不影响其他指标的前提下,极大地提高了其线性度IIP3指标,使其达到8.6 dBm的高线性度。通过合理优化整体参数,噪声系数仅为 10.9 dB,增益高达14 dB,在同类混频器设计中,性能指标较优。

1 线性度提高技术

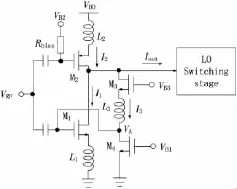

由于有源混频器的线性度主要取决于跨导级的线性度,因此本文在跨导级引入线性提高技术。图1给出了本文所采用的跨导级电路图,它由M1和M2组成的CMOS反相器、共栅晶体管M3、电流源M4和退化电感L1~L3组成。共栅晶体管 M3作为辅助放大器,用于抵消作为主放大器的CMOS反相器所产生的三阶交调分量IMD3。源极退化电感 L1和L2用于输入阻抗的匹配[5],退化电感L3用于控制正反馈补偿中的三阶跨导分量。该电路通过主从放大器产生大小相等、相位相反的IMD3分量,并在其相加时抵消,从而改善了混频器的线性度。

图1 电感源极退化技术的跨导级

如图1所示,输出电流 Iout的大小如下所示:

其中,I1、I2和 I3分别是晶体管 M1、M2和 M3的漏极电流。由于跨导级是电路非线性特性产生的主要因素,将 I1、I2和I3用泰勒级数展开式表达如下:

其中,gm1n、gm2n和 gm3n分别是放大器 M1、M2和 M3的n阶跨导分量。

当直流电压 VGS和交流信号 Vgs加到 MOSFET的输入端时,N型MOSFET的总漏极电流iD为:

其中:

μn是器件的电子迁移率,COX是栅极单位面积电容量,VTHN是N型MOSFET的开启电压。式(5)的第一项代表偏置电流,第二项和第三项代表交流信号电流,第三项产生非线性失真。输入信号Vgs越大,MOSFET所产生的非线性失真越明显。

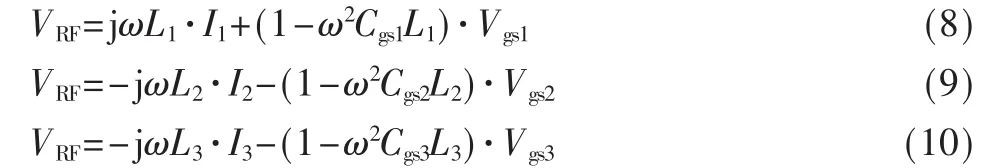

为了分析每一个电感源极退化放大器所产生的非线性效应,图2给出了包含有退化电感的CMOS模型的电路图。其中图2(a)为共源结构的 NMOS,图2(b)为共源结构的PMOS,图2(c)为共栅结构的NMOS。为了简化分析,该模型忽略了对线性度影响较小MOS晶体管二阶效应,如沟道长度调制效应、体效应,以及其他的寄生电容效应。由图2可知,漏电流(I1、I2和 I3)和输入电压(VRF)之间的关系表达式如下所示:

图2 包含有退化电感的CMOS器件模型

其中,Vgs1、Vgs2和 Vgs3分别是 MOS器件 M1、M2和 M3的栅源间电压。

将式(2)~式(4)和式(7)~式(10)代入到式(1)中可得到[11]:

本文所采用的跨导级的输出电流包含有基波频率的二阶和三阶交调分量,较高阶次的交调分量已经在计算过程中忽略。相应跨导级的输入三阶交调点IIP3可被表示为:

其中,一阶跨导gm1是跨导级的基本增益。IMD3主要取决于三阶跨导,而三阶跨导由退化电感和工艺相关参数(k1、k2和 k3)决定。为了便于分析与计算,仅将式(11)中每个跨导的前三项代入式(12)中,可得:

式(13)中一阶跨导 gm1的前两项和第三项分别代表了主从放大器的基本跨导系数。式(13)表明:为了使混频器具有基本增益,必须保证前两项要大于第三项,而且,需要合理地设计退化电感的大小以抵消该跨导级的三阶跨导项 gm3,退化电感的取值应如下式所示[11]:

上式中电感L1和L2必须采用较小的数值,主要有三个方面的原因:(1)由于 k1和 k2是决定跨导级基本增益的主要因素,因此工艺相关参数 k1和 k2应相对大于k3;(2)较大的 L1和 L2使得式(13)的分母增加,恶化了跨导级的IIP3,且较大的L1和L2增加了电路芯片的面积,提高了设计成本;(3)L3的电感值基于式(14)进行选取,且鉴于 L1、L2和L3也对电路的输入阻抗造成影响,因而在取值的过程中也要兼顾电路的输入阻抗,使其匹配到50 Ω。所以通过合理优化设计参数,本文所采用的跨导级电路可有效减小三阶交调分量,得到较高的 IIP3值。

2 工作原理与性能分析

图3所示为本文所设计的混频器电路图,该混频器基于折叠拓扑结构,其主要由四部分组成:跨导级(M1~M3)、开关级(M4~M5)、负载级(RL)和电流注入级(M6~M7)。通过引入电流注入结构,改善了混频器的增益和噪声特性。

图3 混频器电路原理图

此混频器采用 TSMC 0.13 μm CMOS工艺设计,运用ADS2009U软件对其进行仿真,并完成了版图设计。如上所述,在保证输入阻抗匹配的前提下,尽量选择较小的L1和L2的电感值,而且L3电感值的选取要满足式(14)所示的条件,以抵消该跨导级的三阶跨导项 gm3,进而改善电路的线性度。

混频器工作电压为 1.2 V,射频输入频率 2.45 GHz,功率-30 dBm;本振频率 2.35 GHz,功率 0 dBm,工作电流为7.2 mA。输入三阶交调点的IIP3仿真结果图如图4所示。在本振功率为0 dBm时,其为8.6 dBm,线性度指标较优。图5和图6分别给出了噪声系数NF和转换增益随着本振功率变化的仿真结果,在本振功率为 0 dBm时,噪声系数为10.9 dB,增益为14 dB。

图4 输入三阶交调点IIP3仿真结果

图5 噪声系数仿真结果

图6 转换增益的仿真结果

图7为该混频器电路的版图,版图尺寸为0.71 mm× 0.62 mm。表1给出了本文所设计的高线性度混频器与以往文献所设计的混频器的比较结果。为了便于比较,给出了采用式(15)所示的归一化FOM指标[12]。由该表可见,本文所设计的混频器的综合性能指标最优,FOM达到16.06 dB。

图7 混频器版图

式中,G为增益,NF为噪声系数,P为电路所消耗的功耗。

表1 混频器性能对比结果

3 结论

本文通过理论分析,为抵消三阶跨导分量,得到更高的线性度提供了设计方向。该跨导放大器最终应用于折叠结构式混频器当中,以改善混频器的线性度,并且通过引入电流注入技术改善电路的增益和噪声。仿真结果表明,该混频器达到IIP3=8.6 dBm的较高线性度,增益高达14 dB,噪声系数仅为10.9 dB。通过与其他相关研究成果相比较可知,本文所设计的混频器归一化FOM指标最优,达到16.06 dB。

通过采用本文提供基于电感源极退化技术的高线性跨导放大器设计方法,并利用 TSMC 0.13 μm CMOS工艺完成了某型号UWB射频通讯芯片中的混频器单元设计与仿真。目前,该混频器电路芯片已下线,并利用多项目晶圆合作MPW项目进行了流片。

[1]LI B,SUN L,KO C T,et al.A high-linearity capacitanceto-digital converter suppressing charge errors from bottomplate switches[J].IEEE Transactions on Circuits and Systems-I:Regular Paper,2014,61(7):1928-1941.

[2]HE S,SAAVEDRA C E.Design of a low voltage and lowdistortion mixer through volterra-series analysis[J].IEEE Transactions on Microwave Theory and Technology,2013,61 (1):177-184.

[3]谷江,毛陆虹,门春雷,等.一种电流注入式零中频正交混频器[J].固体电子学研究与进展,2012,32(3):281-285.

[4]MOLLAALIPOUR M,MIAR N H.An improved high linearity active CMOS mixer:design and volterra series analysis[J]. IEEE Transactions on Circuits and Systems-I:Regular Papers,2013,60(8):2092-2103.

[5]YANG M S,LEE S G.Linearity improvement technique for the common-source transconductance stage[C].IEEE Midwest Int.Circuits Syst.Conf.,Cairo,Egypt,Dec.2003.

[6]MOLLAALIPOUR M,NAIMI H M.An improved high linearity active CMOS mixer:design and volterra series analysis[J].IEEE Transactions on Circuits and Systems-I:Regular Papers,2013,60(8):2092-2103.

[7]YEH C I,FENG W S,HSU C Y.0.9-10.6 GHz UWB mixer using current bleeding for multi-band application[J]. Electronics Letters,2014,50(3):186-187.

[8]HO S S,SAAVEDRA C E.A CMOS broadband low-noise mixer with noise cancellation[J].IEEE Transactions on Microwave Theory and Technology,2010,58(5):1126-1132.

[9]LEE T H.The design of CMOS radio frequency integrated circuits[M].Cambridge Uuiversity Press,2001.

[10]MOLLAALIPOUR M,MIAR N H.An improved high linearity active CMOS mixer:design and volterra Series Analysis[J].IEEE Transactions on Circuits and Systems-I:Regular Papers,2013,60(8):2092-2103.

[11]KIM M G,YUN T Y.Analysis and design of feedforward linearity-improved mixer using inductive source degeneration[J].IEEE Transactions on Microwave Theory and Technology,2014,62(2):323-331.

[12]VIDOJKOVIC V,VANDERTANG J,LEEUWENBURGH A,et al.A low-voltage folded-switching mixer in 0.18-μm CMOS[J].IEEE Journal of Solid-State Circuits,2005,40 (6):1259-1264.

[13]SHI L X,CHEN C,WU J H,et al.A 1.5-V current mirror double-balanced mixer with 10-dBm IIP3 and 9.5-dB conversion gain[J].IEEE Transactions on Circuits and Systems-II:Express Briefs,2012,59(4):204-208.

[14]HE S,SAAVEDRA C E.An ultra-low-voltage and lowpower×2 subharmonic downconverter mixer[J].IEEE Transactions on Microwave Theory and Technology,2012,60 (2):311-317.

Design of high linearity mixer using inductive source degeneration

Zhang Leiming,Liu Bo,Zhang Jincan

(Electrical Engineering College,Henan University of Science and Technology,Luoyang 471023,China)

This paper presents a novel linearity-improvement feed-forward amplifier whose transconductance stage use the inductive source-degeneration technology.The proposed technique is applied to a CMOS RF mixer based on a folded-type topology.Linearity improvement is achieved by cancelling the third-order transconductance terms between the inverter and auxiliary amplifiers.Simulated results show that the proposed mixer achieves a third-order input intercept point of 8.6 dBm,a noise figure of 10.9 dB,a conversion gain of 14 dB,and has the highest figure-of-merit among other linearity improved mixers that have been previously reported.

linearity;transconductance amplifier;mixer;inductive source-degeneration

TN773

A

10.16157/j.issn.0258-7998.2016.02.008

国家自然科学基金项目(611101167);2014年河南省教育厅基础与前沿技术研究项目(14B510004);河南省高等学校重点科研项目(15A510001)

(2015-07-23)

张雷鸣(1980-),通信作者,男,硕士,讲师,主要研究方向:混合信号集成电路、器件模型以及制造工艺等,E-mail:zlmdemail@163.com。

张金灿(1985-),男,博士,讲师,主要研究方向:混合信号集成电路设计、超高频大功率化合物半导体器件与集成技术。

刘博(1982-),男,博士,讲师,主要研究方向:混合信号集成电路、工艺波动相关特性与成因。

中文引用格式:张雷鸣,刘博,张金灿.基于电感源极退化技术的高线性混频器设计[J].电子技术应用,2016,42(2):32-35.

英文引用格式:Zhang Leiming,Liu Bo,Zhang Jincan.Design of high linearity mixer using inductive source degeneration[J]. Application of Electronic Technique,2016,42(2):32-35.