基于CPLD的隧道灯控制电路设计

周家萍 谭福奎 李荣翠

(1兴义民族师范学院, 贵州 兴义 562400; 2贵州大学, 贵州 贵阳 550000)

基于CPLD的隧道灯控制电路设计

周家萍1谭福奎1李荣翠2

(1兴义民族师范学院, 贵州 兴义 562400; 2贵州大学, 贵州 贵阳 550000)

随着社会的发展,交通越来越便利,对于多山的贵州地区,想要实现交通的便利,隧道是必不可少的工程,而其中隧道灯的节能控制就是人们不可忽视的问题。在实际生活中隧道灯的节能控制的方法有很多,这里采用的是CPLD来实现这一功能。利用CPLD设计的电路可对隧道照明区域进行分段控制,做到“车近灯亮,车过灯灭”,消除“黑洞效应”和“白洞效应”,为驾驶员提供良好的驾驶环境,提高行驶安全性。同时,“车近灯亮,车过灯灭”的工作方式改变了现有隧道灯24h常亮的工作方式,节约大量电能。

隧道灯的控制;CPLD;电路设计

随着经济的高速发展,随着西部大开发战略的实施,我国高速公路在山区修建越来越多,由于山区地形、地质、水文条件复杂,造成了构造物众多,桥梁隧道总长占路线长度的比例大,有的山区高速公路,桥隧比例高达70%~80%。因此桥梁和隧道成为了实现高速公路建设的关键,也使公路隧道照明成为了一项重要的内容。高速公路在山区修建越来越多,造成隧道数量的增多,而隧道照明只有在照明亮度达到要求时才能保证行驶安全。因此,隧道用电就成为高速公路运营管理部门的一笔沉重的负担。目前我国高速公路隧道照明系统普遍采用全天运行的长明灯模式,能够实现照明自动控制的非常有限,这种传统的隧道照明系统存在着大量电能浪费问题。

本文利用CPLD设计的电路可对隧道照明区域进行分段控制,做到“车近灯亮,车过灯灭”,消除“黑洞效应”和“白洞效应”(在汽车进入隧道时,由于光照变化较大,驾驶员会一时适应不了,感觉洞口很黑,无法辨清道路状况而产生“黑洞效应”,这会使得司机容易对速度和距离的判断产生偏差,从而带来严重的安全隐患;相反,当车从隧道驶出时,由于隧道内外光差,外部较亮,也会使驾驶员不适应,而分辨不清路况产生“白洞效应”),为驾驶员提供良好的驾驶环境,提高行驶安全性。同时,“车近灯亮,车过灯灭”的工作方式改变了现有隧道灯24h常亮的工作方式,节约大量电能。

一、照明系统硬件设计

1.电路实现目标要求

当有车辆接近隧道时,传感器传递信号,第一组灯立即点亮,第二组灯延迟十秒后点亮,第三组第四组等依次类推,共有二十组灯,每组1000W的功率。第一组灯点亮后若再无车辆经过,三分钟后自动熄灭,第一组熄灭后第二组延迟十秒熄灭,其他组依次类推。若在三分钟内再次有车辆经过,第一组灯继续点亮并重新计时三分钟,其他组依次延迟十秒后与第一组一致。照明电路系统在设计过程中,用按键K1表示车辆接近隧道时传感器所产生信号,led灯代替隧道灯。

2.硬件系统设计

根据题目要求并经过仔细分析,考虑到硬件软件的因素,大致可将系统分为:物体感应模块,时钟模块,按键控制模块,中央控制模块,显示模块。如图1-1所示。

图1-1 系统整体框图

3.各模块的硬件电路设计

(1)物体感应模块设计

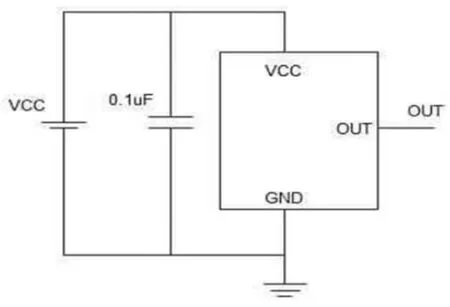

本文用按键来代替是否有车辆经过所产生的信号,在实际应用中检测是否有车辆经过的传感器类型有很多种并且技术已经相当成熟。MRS101是一款集成了隧道磁阻(TMR)传感器和CMOS技术,为高灵敏度、高速、低功耗、高精度应用而开发的双极磁开关。MRS101采用高精度推挽式半桥TMR磁传感器和CMOS集成电路,包括TMR电压发生器、比较器、施密特触发器和CMOS输出电路,能将变化的磁场信号转化为数字电压信号输出。MRS101通过内部电压稳压器来提供温度补偿电源,并允许宽的工作电压范围。MRS101以低电压工作、1微安级的供电电流、高响应频率、宽的工作温度范围、优越的抗外磁干扰特性称为众多低功耗、高性能应用的理想选择。如下图1-2所示。

图1-2 功能框图

输出和磁场的关系见下表1-1

表1-1 输出和磁场的关系

平行于TMR传感器敏感方向的磁场超过工作点门限BOP时,MRS101输出低电平。当平行于TMR传感器敏感方向的磁场低于释放点BRP时,MRS101输出高电平。磁场工作点和释放点的差值就是传感器的回差BH。为了降低外部噪声,可在传感器电源和地之间增加一个滤波电容(靠近传感器)。如应用电路图所示,典型值为0.1uF。电路图见图1-3。

图1-3 电路图

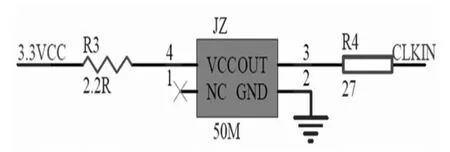

(2)时钟模块设计

时钟模块选用的时钟源是晶振为50MHz的有源晶体。可对灯的亮灭与延迟提供精确的时间控制。原理图见下图1-4所示。

图1-4 时钟源原理图

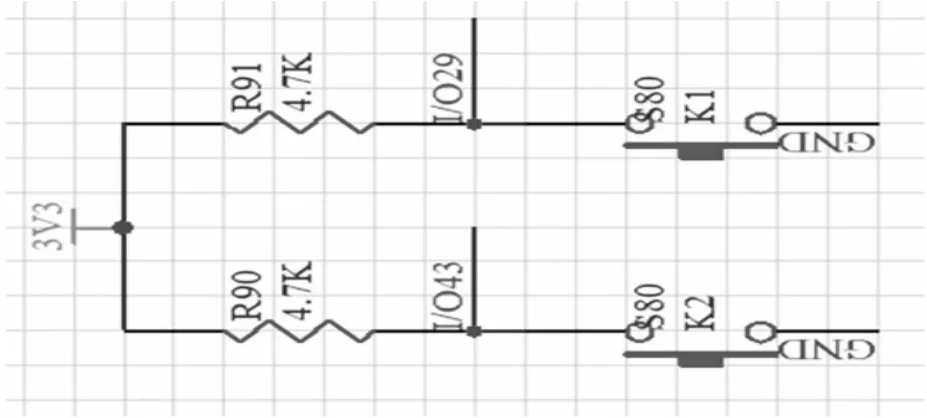

(3)按键控制模块设计

本文用到两个按键K1与K2,按键K1被按下时,代表有车接近隧道,产生低电平,松开后代表无车辆接近,产生高电平,低电平是触发信号。按键K2为复位信号,按下按键,所有灯均灭,重新开始等待K1信号。松开后可循环上述过程。电路原理图如下图1-5。

图1-5 按键电路原理图

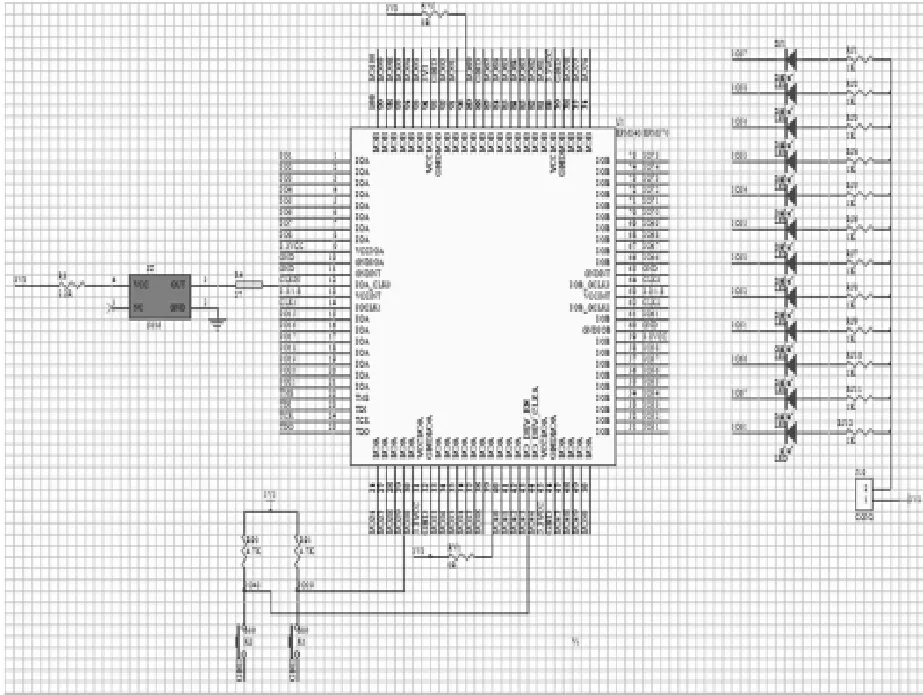

(4)中央控制模块设计

本文是基于CPLD中的EPM240T100C5N芯片来控制全局,此芯片引脚丰富功能强大,并相比与其他FPGA经济实惠,但因逻辑单元过小,只有240个逻辑单元,所以只能实现两个灯的功能。经过仿真后,又在Cyclone II的EP2C35F672C6ES芯片上实现了8个LED的控制,并确认了此功能的实现,模拟了隧道灯的控制。

CPLD(Complex Programmable LogicDevice)复杂可编程逻辑器件,是从PAL和GAL器件发展出来的器件,相对而言规模大,结构复杂,属于大规模集成电路范围。是一种用户根据各自需要而自行构造逻辑功能的数字集成电路。其基本设计方法是借助集成开发软件平台,用原理图、硬件描述语言等方法,生成相应的目标文件,通过下载电缆(在系统编程)将代码传送到目标芯片中,实习设计的数字系统。

CPLD与FPGA的比较优势如下:

①CPLD更适合完成各种算法和组合逻辑,FPGA更适合完成时序逻辑。

②CPLD的连续式布线结构决定了它的时序延迟是均匀的和可测的,而FPGA 的分段式布线结构决定了其延迟的不可预测性。

③CPLD比FPGA使用起来更方便。CPLD的编程采用E2PROM或FASTFLASH技术,无需外部存储器芯片,使用简单。而FPGA的编程信息需存放在外部存储器上,使用方法复杂。

④CPLD的速度比FPGA快,并且具有较大的时间可预测性。这是由于FPGA是门级编程,并且CLB之间采用分布式互联,而CPLD是逻辑块级编程,并且其逻辑块之间的互联是集总式的。

⑤在编程方式上,CPLD主要是基于E2PROM或FASTFLASH存储器编程,编程次数可达1万次,优点是系统断电时编程信息也不丢失。FPGA大部分是基于SRAM编程,编程程序会在系统断电时丢失,每次上电时,需从器件外部将编程数据重新写入SRAM中。

⑥CPLD保密性好,FPGA保密性差。

本文的主芯片采用ALTERA?MAXII系列的EPM240T100C5N(相当于8650门CPLD,容量是以前的EPM7128的两倍,并且可以烧写至少10万次以上)。MAX?II器件采用了全新的CPLD体系结构,在所有CPLD系列中单位I/O成本最低,功耗最低。MAXII运用了低功耗的工艺技术,和前一代MAX器件相比,成本降低了一半,功率降至十分之一,容量增加了四倍,性能增加了两倍。主板采用双电源供电:USB供电和稳压电源供电,只要二者有一个接通,试验板便可获得5V和3.3V的工作电压。(实际操作中,只需给核心板或主板上一个电源接口供电即可)。发光管电路,十二只LED发光管,可以用于各种闪烁或交通灯指示用途的编程。有6个独立按键电路可供使用。

(5)显示模块设计

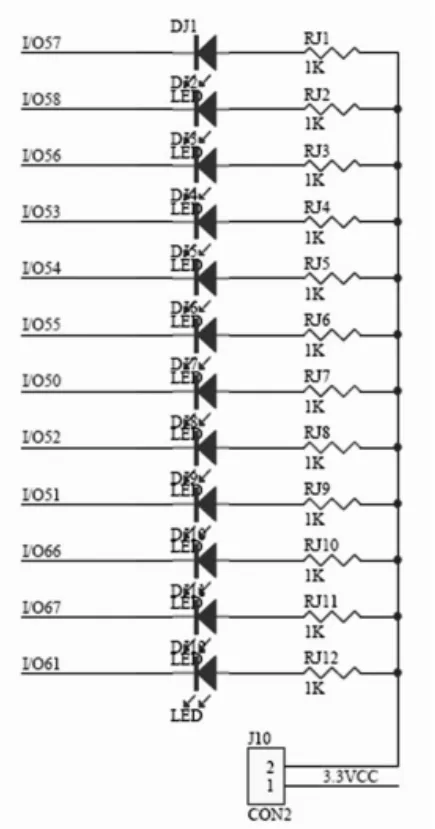

本文用LED代替隧道灯来模拟灯的亮灭与延迟,电路原理图如图1-6。

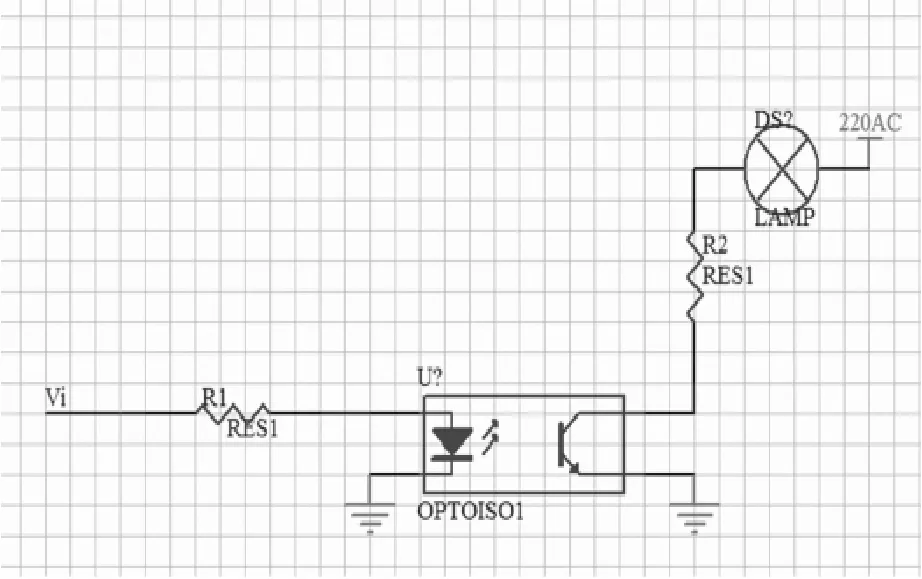

在实际应用中,可利用弱电控制强电,用3.3V的输出电压与继电器或光耦放大器相连,继电器或光耦放大器的另一端是220V控制的隧道灯。例如光耦放大器,当有3.3V电压时,光电二极管导通,发光使三极管导通,隧道灯点亮。原理图如图1-7。

图1-6 led电路原理图

图1-7 光耦放大器原理图

4.硬件系统原理图

本文硬件系统的总体原理图见下图1-8。

图1-8 电路原理总图

在实际应用中将led的每一个接口与一个光耦放大器Vi相接即完成实际的连接。

二、软件设计与调试

1.软件系统设计

本软件系统共包括主程序部分,led灯控制亮灭时间部分,灯与灯之间延迟时间部分。通过EPM240芯片与内部晶振50MHz时钟,在Verilog语言编程的基础上进行设计,分成两个模块,并对两个模块进行调用,可以达到理论上20组灯的控制。

(1)led灯时间控制程序设计

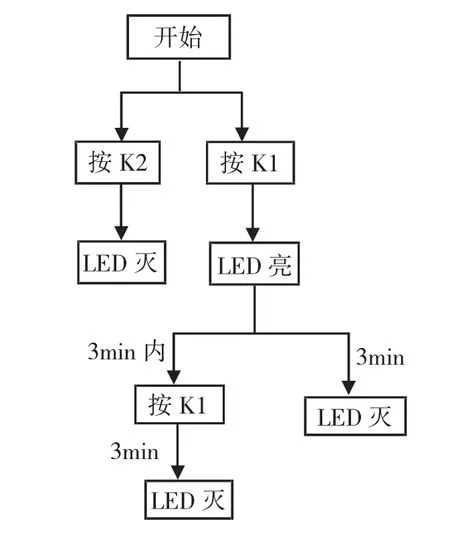

本文中每组灯均与第一组亮的时间相同,只是依次延迟十秒,故第一组灯为核心并设计出第一组灯的控制流程图。在这段程序中,无论何时只要按下K2键,灯就会立刻全部灭,流程图如图2-1。

图2-1 LED控制流程图

每组灯自身情况初始灭,有信号亮三分钟,无信号,三分钟之后灭,若三分钟之内有信号则继续亮三分钟。

(2)延迟时间程序设计

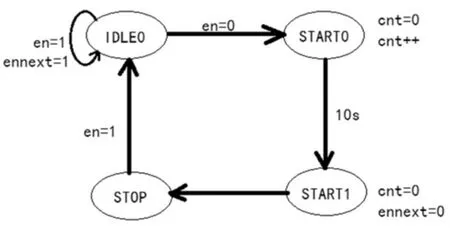

本段程序是灯与灯之间延迟十秒的程序,每一组灯充当下一组灯的控制信号。状态转换图如图2-2。

图2-2 延迟状态转换图

(3)主模块程序设计

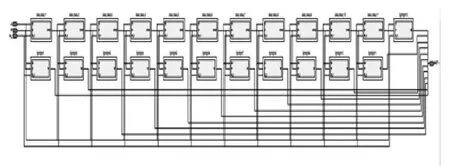

将各功能连接好后见下图2-3。

图2-3 RTL视图

由于EPM240芯片对应的板子只有十二只LED灯,故在这里只做了十二个的设计,若在实际中需要二十组或更多,只需连接芯片其余可用引脚,并添加主程序内容即可,方便易行。

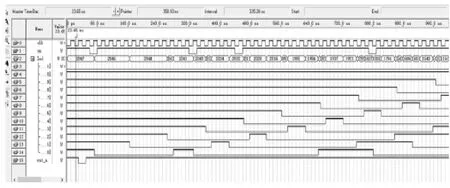

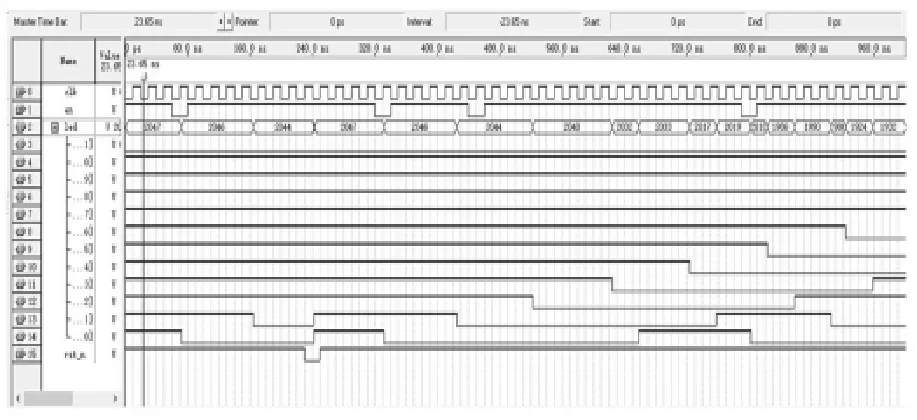

(4)仿真结果

仿真过程中,4个时钟周期代替10s,10个时钟周期代替3min,12个led,仿真时间范围从0ns到1us。

图2-4 仿真结果

当产生复位信号时,所有信号清零,所有灯均灭。

图2-5 产生复位信号的仿真结果

2.整体系统的软件调试

CPLD与FPGA系列电路板常用的编程软件是quatus ii,本文使用的是quatus ii9.0,该软件能对Verilog语言与VHDL语言进行语言编译。同时能够在编写过程中调试程序的错误并且支持模块化设计,缩短了开发周期减少了开发难度。本文利用Verilog语言进行编程调试并进行RTL电路的观测,此软件自带仿真工具可进行基本的仿真功能,减少了硬件调试中的风险和难度。

本文介绍的以CPLD为核心的隧道灯控制电路系统,根据电路实际的设计目标要求设计实现了对隧道灯的智能分段控制,并通过仿真进行了验证,实现了隧道灯“车近灯亮,车过灯灭”的节能目标。

[1]夏宇闻.Verilog数字系统设计教程(第二版)[M]北京航天航空大学出版社,2008.

[2]周兴华CPLD入门与实践[M].中国电力出版社,2011.

[3]Mark Zwolinski著System Verilog数字系统设计[M],.电子工业出版社,2011.

[4]阎石,王红,数字电子技术基础[M],高等教育出版社,2012.

责任编辑:王文宝

Tunnel lamp control circuit design based on CPLD

ZHOU jia-ping1TAN fu-kui1Li rong-cui2

(Xingyi Normal University for Nationalities,Xingyi,Guizhou 562400,China;GuizhouUniversity,Guiyang,Guizhou550000,China)

With the development of society,more convenient for mountainous areas in Guizhou,to achieve ease of transport,tunnels are essential engineering and energy saving control of tunnel lighting is the problem not to be ignored.Tunnel lights in real life there are many ways of energy-saving control,the CPLD is used to implement this functionality.Using CPLD to design circuits the control of tunnel lighting zones,so that"Near car lights,car lights off too"to eliminate the"black hole effect“and the”white hole effect",providing drivers with good driving environment,improve driving safety.Meanwhile,“Near car lights,car lights off too”way of working changes the existing tunnel lamp 24h always works,saves a lot of power.

Tunnel light controlling,CPLD,circuit design

1009—0673(2016)03—0120—05

TM352

A

2016—04—15

黔西南州科技计划项目(2014—7):“高速公路隧道节能照明控制系统LED灯具控制器研究”的阶段性成果。

周家萍,(1976— ),女,贵州兴仁人,兴义民族师范学院物理与工程技术学院副教授,工学硕士,主要从事电子技术方面教学及研究。