高速组网无线数传链路设计及FPGA实现

陈 韵,刘 建,杨 健,张云飞

(中国航天科工集团8511研究所,江苏 南京 210007)

·工程应用·

高速组网无线数传链路设计及FPGA实现

陈韵,刘建,杨健,张云飞

(中国航天科工集团8511研究所,江苏 南京 210007)

为了解决雷达及电子对抗系统组网协同工作的问题,设计一种基于QPSK调制解调的高速无线数传链路,并对其进行仿真及FPGA硬件实现。利用QPSK调制信号功率集中、带外泄漏少、载波抑制的优点,将其设计成为组网系统的底层通信链路。该无线数传链路中频频率150MHz,传输信息速率为10Mbps,为了适应各子平台(站)相对运动的通信环境,在外加10kHz载波频偏的条件下进行蒙特卡洛仿真,在5dB信噪比条件下误码率达到10e-5的量级,接近理论值。

无线通信;组网通信;QPSK调制解调;FPGA

0 引言

目前雷达和电子对抗技术朝着系统化网络化的方向发展,电子对抗系统子系统或各平台之间数据交换的业务需求越来越大,需要实时快速的情报交换以确定更加合适的侦察干扰策略[1]。这就对无线通信链路提出了较高的要求,应使其具备实时性、可靠性与安全性的特点,并可应用多平台系统时间同步技术,实时实现各平台的时间校正,使系统具有统一的工作时间节拍。因此,高速无线通信数传链路的研制具有重要意义和广阔的应用前景。

现有高速无线数传基带调制解调技术分为多种,如AM、FM、扩频技术、OFDM技术[2-5]等。但是这些技术的应用要求固定的调制流程和通信协议,通信制式注重特定的通信环境,对于多节点协同组网工作方面的特殊需求并未加以设计,导致通信制式的调制解调芯片并不能完全适用[6]。而软件无线电技术[7]则具有适用于通信技术信号频率与带宽的特点。本文正是利用软件无线电的设计思想,采用大规模现场可编辑阵列(FPGA)设计实现基于正交相移键控(QPSK)调制解调的高速无线数传链路,较好地满足了雷达侦察干扰电子技术网络化发展的趋势。

1 QPSK调制解调原理

1.1总体设计

所谓调制就是指用调制信号的变化规律去改变载波的某些参量,从而把调制信号的频谱搬到信道允许传输的频段范围内。QPSK相移键控是指采用相位变化来调整载波信号的相位,从而来传递信息,具有频谱分量集中、带外泄露较小和载波频率受到抑制的优点。QPSK调制方式成熟,应用广泛,集合以上优点,被选为组网侦察干扰系统无线链路调制解调方式。

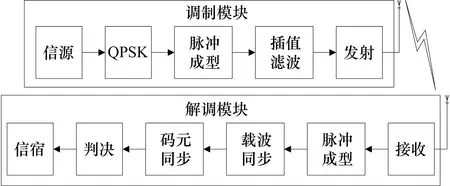

总体通信链路设计如图1所示。由信源端产生10Mbps的比特流信号,经过QPSK调制之后变成5Msps的码元符号,通过对其进行脉冲成型处理,再进行插值滤波,形成基带信号。对基带信号进行上变频送入微波模块,形成发射信号。接收端对接收信号进行下变频,得到中频采样数据,对采样信号进行脉冲成型匹配滤波之后,送入到载波同步模块,跟踪信号载波,去除频偏及多普勒效应,并将得到的基带信号送入码元同步模块进行定时抽样,并进行判决得到信息比特流送入到信宿中。

图1 QPSK通信系统框图

1.2调制解调原理

QPSK是利用载波4个不同的相位来表征数字信息的一种调制方式。具体调制信号可以表示为:

(1)

式中,Es代表信号在一个码元间隔内的能量,Ts为一个码元周期,ωc为载波角频率,φi为4种可能取值的相位。

QPSK信号只是用来携带基带信号的数字信息,而且经过成型滤波器得到适合于信道的传输波形。成型滤波器不仅可以平滑波形,提高频带利用率,而且可以消除码间干扰。一般成型滤波器函数通常采用平方根升余弦滚降特性滤波器。这样,经过调制的QPSK信号可以表示为:

(2)

(3)

当载波信号到达接收端之后,需要对其进行解扩解调,从而恢复出信源信息。具体解扩解调所需步骤如下:

1)数字下变频模块完成将AD带通采样数据与NCO产生的两路正余弦序列相乘,将接收的中频信号的频偏搬移到零频,输出I/Q两路同相和正交分量,然后通过低通滤波器将高频分量滤除。

2)匹配滤波器的传输特性为平方根余弦滚降特性,且滚降因子与成型滤波器相同。匹配滤波器与调制端的成型滤波器构成最佳基带传输系统,这样能使码元能量集中,对减小码间干扰和定时提取非常有利。

3)载波同步模块从匹配滤波器输出的基带信号中,提取剩余载波频差,通过调整NCO来完成剩余载波频差的消除。

4)位同步模块是从载波同步环路内插重采样的两路数据提取出I/Q两路位同步时钟,并利用该时钟对I/Q两路数据进行内插重采样判决输出。

2 组网网络协议设计

多节点协同组网通信平台需要考虑的一个问题就是多用户分配的问题,在实际应用中常使用组网工作的方式。组网式信息对抗系统拓扑结构如图2所示,网络由1个主控计算机、1个主干扰机和多个从干扰机组成。每个干扰机设置两个独立的RS-485通信信道A和B,信道A用于与主控计算机通信,信道B用于与干扰机网络通信。干扰机网络为多点连接的RS-485网络。

图2 组网通信网络实验拓扑图

2.1关键节点模式

组网式干扰以主干扰机为核心,为防止主干扰机被摧毁后整个干扰网络失效,主干扰机为动态分配模式,即每隔固定的时间间隔进行一次网络同步,对网络时间进行同步、确定主干扰机角色和加入新的从干扰机。存在确定主机情况下,步骤描述如下:

1)每固定的时间间隔,主干扰机发出一次网络时间同步通信报文;

2)各从干扰机收到网络时间同步通信报文后,根据硬件ID在各自分配的时间片内进行应答,某时间片内无对应的从干扰机应答则认为从干扰缺失;

3)主干扰机根据应答结果建立有效干扰机列表,进行侦察和干扰资源分配。

2.2竞争节点模式

在无法确定关键节点或者关键节点被摧毁的情况下,多个从侦察干扰机通过竞争确定主机的步骤如下:

1)从干扰机开机后开始计时,超过固定的时间间隔后仍未收到网络时间同步通信报文,则从干扰机自定义为主机,网络时间即为本机时间;

2)从干扰机自定义为主机后需要立即发送网络时间同步通信报文,以在网络中确立主机地位。

3 算法仿真及FPGA实现

3.1算法仿真

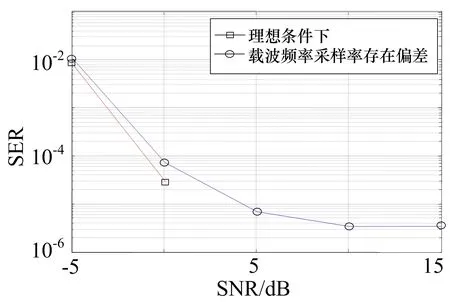

为了验证本文所设计的无线数传链路的性能,采用Matlab仿真软件对对本文设计通信链路进行蒙特卡洛仿真。衡量通信系统性能的参数有多种,如输入信号动态范围、载波捕获门限、载波捕获带宽和解调误码率性能。而解调误码性能最能够反映出通信系统的性能,通过在解调端对信号注入不同程度的噪声,获得不同的信噪比之后,来测试不同信噪比下的误码性能。仿真条件为输入信息速率为10Mbps,中频载波为150MHz,采样率为200MHz,为了进一步仿真出收发两端相对运动而产生的多普勒频偏和收发两端时钟的频率漂移现象,在接收端附加了10kHz频偏。输入信噪比为-5~15dB条件下,无载波频偏和有载波频偏的误码率对比如图3所示。可以看出,当信噪比为5dB时,无频偏的数传链路已不存在误码,而频偏为10kHz的误码率也达到10e-5的量级,接近理论值水平。

图3 误码率曲线图

3.2FPGA实现

FPGA即现场可编辑逻辑门阵列,因其实现简单、开发灵活方便,而受到广泛的应用,如今FPGA已经成为数字信号处理的主流硬件,也是软件无线电的标准硬件平台。FPGA内部整合了大量的逻辑单元、时钟管理和DSP,使得其功能十分强大,已经摆脱最初只能进行逻辑控制方面应用,而开始在信号处理与计算方面获得较大应用。Matlab旗下系统工具simulink中包含Xilinx基本模块库,能够完美实现对Xilinx所有FPGA芯片进行仿真与实现支持。本文使用Xilinx公司的K7系列的FPGA,采用simulink实现整体的无线数传链路设计。

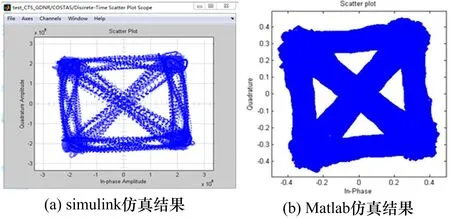

在信噪比为15dB条件下,当载波频偏发生偏移10kHz时,经过载波同步之后的QPSK解调后的simulink和Matlab仿真星座图对比如图4所示。可以看出simulink系统模块设计与Matlab仿真基本相同,实现了设计功能。相同条件下的载波同步后的基带波形如图5所示。可以看出,经过载波同步,能够补偿外部多普勒频偏的影响,可以正确恢复出基带调制波形。在信噪比为15dB条件下码元同步的simulink和Matlab仿真星座图对比图6所示。可以看出simulink系统模块设计与Matlab仿真基本相同,实现了设计功能。相同条件下的码元同步后的基带波形如图7所示。从中系统能够正常地将码元极性进行区分,为后续的码元判决提供良好的条件。

图4 载波频偏10kHz条件下星座图(SNR=15dB)

图5 频偏10kHz载波同步结果

图6 码元同步星座图(SNR=15dB)

图7 码元同步基带波形及定时误差

4 结束语

本文在雷达侦察干扰平台系统化网络化的前提下,设计一种高速无线数传链路,作为分立系统的底层链路。该链路系统基于软件无线电系统设计思想,采用FPGA进行硬件实现,具有实现简单、设计灵活的优点。该链路系统基带调制解调方式采用成熟的QPSK体制,设计中频频率150MHz,信息传输速率10Mbps,较好地满足了侦察干扰平台之间组网数据传输的要求。本文通过Matlab仿真和simulink进行硬件实现,验证了系统的性能指标,达到了系统设计要求,为各平台(站)组网工作奠定了基础。■

[1]何献武,朱洪伟,唐小明,等.雷达通用数据链发展概述[J].舰船电子工程,2010,30(9):36-38.

[2]博战捷,董辉.AM信号到DSB信号的连续过度与同步检波[J].吉林大学学报(信息科学版),2005, 23(3):237-240.

[3]胡海峰,胡茑庆,秦国君.基于改进经验AM-FM解调的复杂信号瞬时特征分析方法[J].国防科技大学学报, 2011, 33(2):119-124.

[4]程乃平,仍宇飞,吕金飞.高动态扩频信号的载波跟踪技术研究[J].电子学报,2003, 31(12):2147-2150.

[5]黄敏,李兵兵.基于整体最小二乘的联合信道估计及OFDM信号检测算法[J].电子与信息学报, 2014, 36(6):1448-1453.

[6]吴炜,左航,余艳梅,等.一种高速DQPSK的设计与实现[J].成都大学学报(自然科学版), 2003, 22(3):8-13.

[7]刘会红,林春霞.基于带通采样QPSK高速解调器的技术分析[J].无线电通信技术,2011, 37(1):59-61.

Design of high speed wireless networking communication and FPGA implementation

Chen Yun, Liu Jian, Yang Jian, Zhang Yunfei

(No.8511 Research Institute of CASIC,Nanjing 210007, Jiangsu,China)

For the problem of cooperative combat networking of radar and ECM system,a new wireless data communication based on QPSK modulation method is introduced.And simulation and hardware implementation with FPGA of this method is introduced.The QPSK modulation is designed to link layer of cooperative combat networking because of the power concentration,carrier suppression and without out band leakage.The medium frequency of wireless data link is 150MHz,and transmission data rate is 10Mbps.To adapt to the relative movement communication environment,the Monte Carlo method is used in the condition of 10kHz Doppler frequency shift and SNR is 5dB.In this condition, the Ber is up to 10e-5 and it is closed to theoretical value.

wireless communication; networking communication; QPSK modulation; FPGA

2015-05-16;2015-06-27修回。

陈韵(1985-),男,助理工程师,硕士,从事导弹制导仿真工作。

TN971

A