三维铝封装结构设计及互连可靠性研究

罗 燕,任卫朋,周 义,王立春

三维铝封装结构设计及互连可靠性研究

罗 燕,任卫朋,周 义,王立春

(上海航天电子技术研究所,上海 200240)

针对三维封装热应力失配引发的互连可靠性问题,提出了基于铝基板侧边互连的三维封装方法。应用ANSYS软件建立了COB(Chip on Board,板上芯片)堆叠灌封模型,分析了单层COB及多层COB的应力分布并进行优化,并通过实验进行验证。结果表明,在COB层间增设围坝结构可有效抑制翘曲,经过25~125℃温循,加设围坝的四层COB灌封结构最大变形量为0.081 mm,最大等效应力为175 MPa,低于硅芯片的断裂强度,层间无开裂,经温循实验后固存读写功能正常。

铝基板;三维封装;COB堆叠;层间围坝;应力分布;侧边互连

随着封装互连技术的不断发展以及人们对集成概念的不断创新,三维封装集成逐渐广泛应用,但仍面临着热应力失配引发的互连可靠性、散热、成本等多种问题[1-3]。三维封装主要包括埋置、有源基板和堆叠三种类型[4]。由于三维堆叠封装方法工艺相对简单,成本相对较低,在三维封装领域受到广泛的关注与应用。最常见的三维堆叠封装方法是将裸芯片贴装于薄膜载体上,材质为陶瓷或环氧玻璃,上面有导体布线,内部互连焊点,两侧有外部互连焊点,再把多个薄膜载体叠装互连。由于载体、互连焊点及芯片均为异质材料,如果热膨胀系数CTE失配,易使焊点失效,影响封装结构可靠性[5]。而芯片间互连的最新方法硅通孔(Through-Silicon-Via)技术,虽然封装密度高,但热量集中,需考虑其可靠性,同时设计复杂性大,成本高昂[6]。

本文基于铝基板提出了一种新的三维封装方法,通过选择性铝阳极氧化技术对铝基板进行内埋布线加工,将裸芯片贴装于铝基板上形成COB,再把多个COB进行堆叠,通过侧边互连线的方法实现三维封装。该方法简单可靠,而且具有绿色低成本制造的特点。

1 三维铝封装结构设计

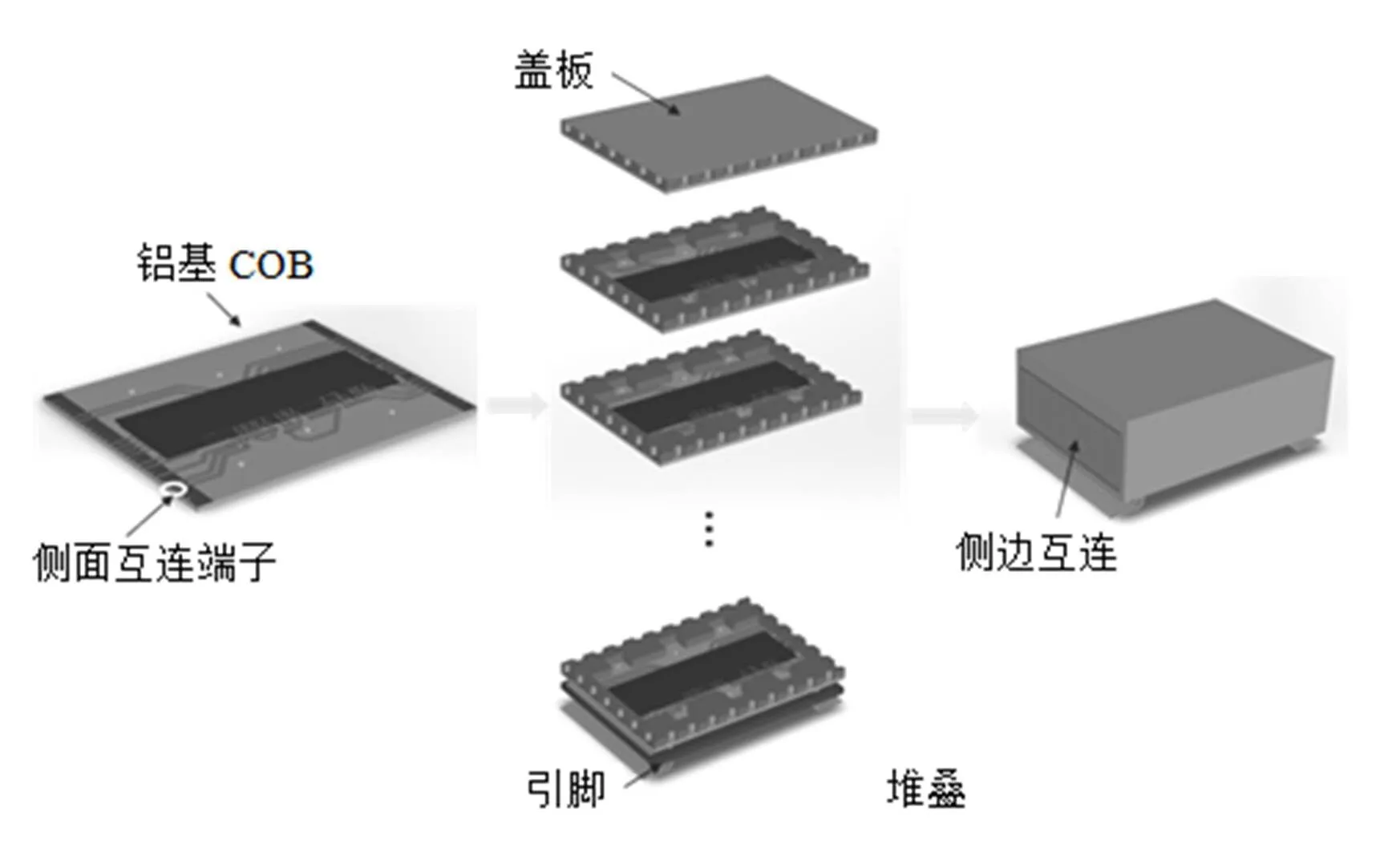

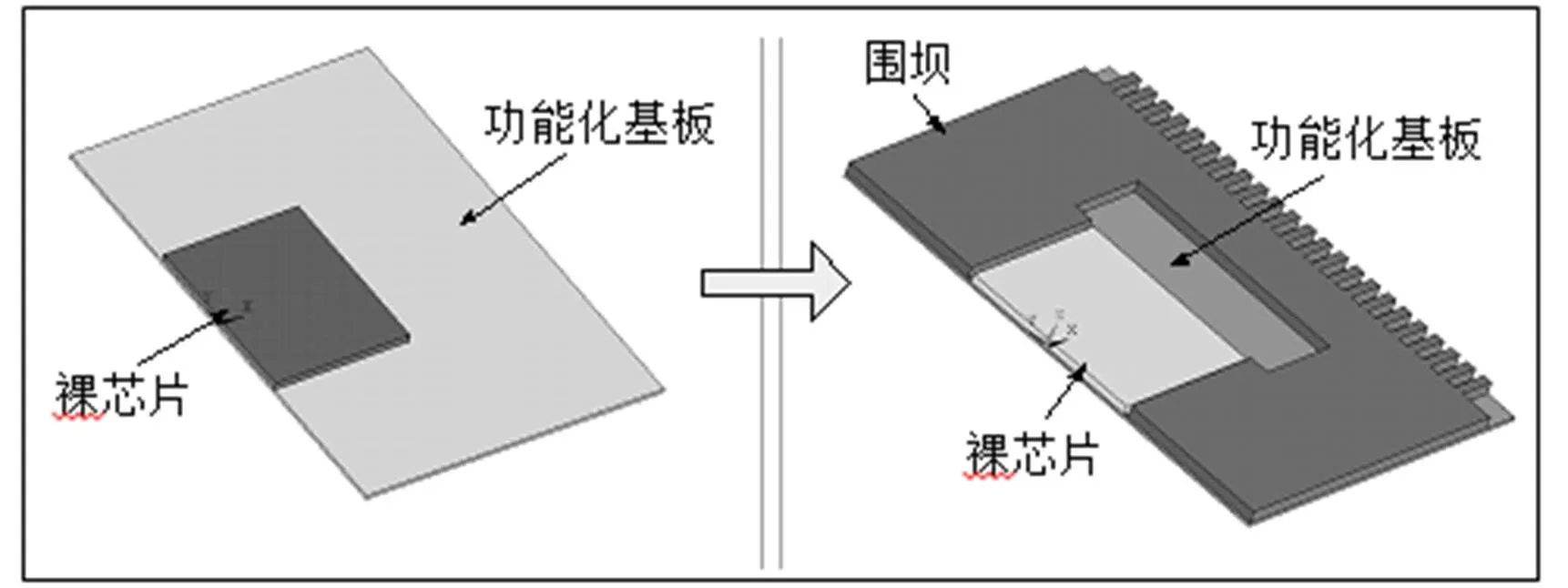

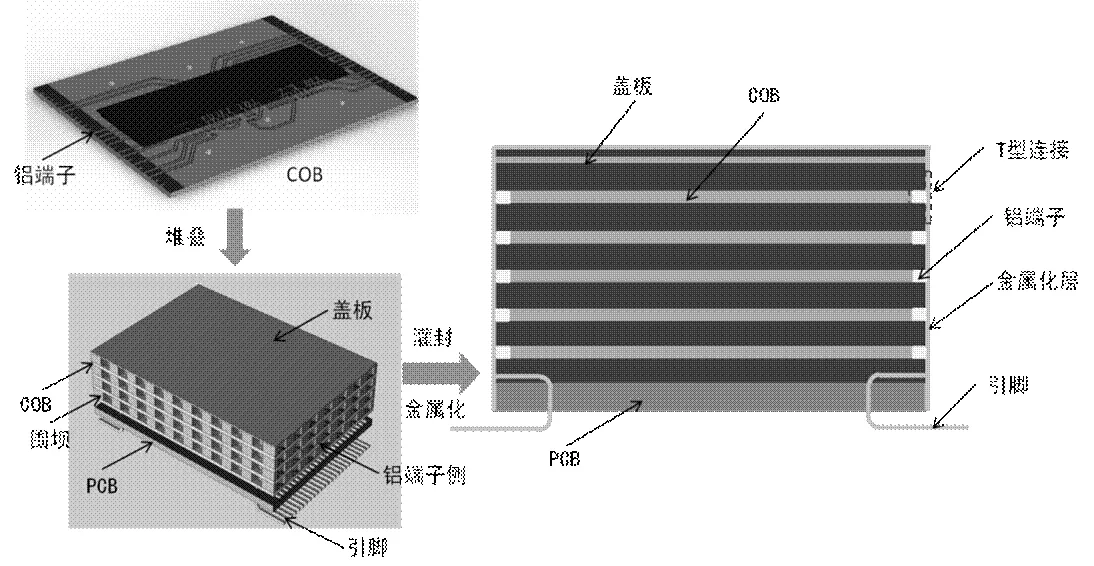

三维铝封装结构如图1所示,单层基板使用铝基板,通过选择性阳极氧化的方法进行铝基板布线,然后将芯片以堆叠的方式贴装于铝基板上,芯片与基板通过引线键合互连,形成三维结构的COB。方向上COB采用SLCC(Stackable Leadless Chip Carrier)结构[7],由四块铝基COB和一块含可伐(4J34)引脚的PCB底座及盖板堆叠而成,根据功能的需要堆叠层数可扩展增加。叠层结构通过环氧树脂胶灌封,叠层之间的电气互连采用侧面垂直互连方式,在外层进行金属化,然后通过激光烧蚀对侧边进行重新布线。

图1 三维铝封装

铝基COB采用了对热应力有释放和缓冲作用的多孔型氧化铝基板,铝基板内埋铝导体由选择性铝阳极氧化技术生成[8],铝导体一端提供与存储器芯片互连端子,另一端提供侧面互连端子,侧边互连端子通过侧边互连布线实现方向的电性能连接。由于基板、芯片及灌封料为异质材料,易发生热失配,需对此三维结构的应力进行模拟分析,从而对堆叠结构进行优化。

2 有限元模型的建立

结合材料的性能参数与结构形状,通过ANSYS数值模拟对封装体内的应力场分布和翘曲形变量进行精确计算,为封装体的可靠性设计提供定量依据。在进行数值模拟前应先建立有限元模型。

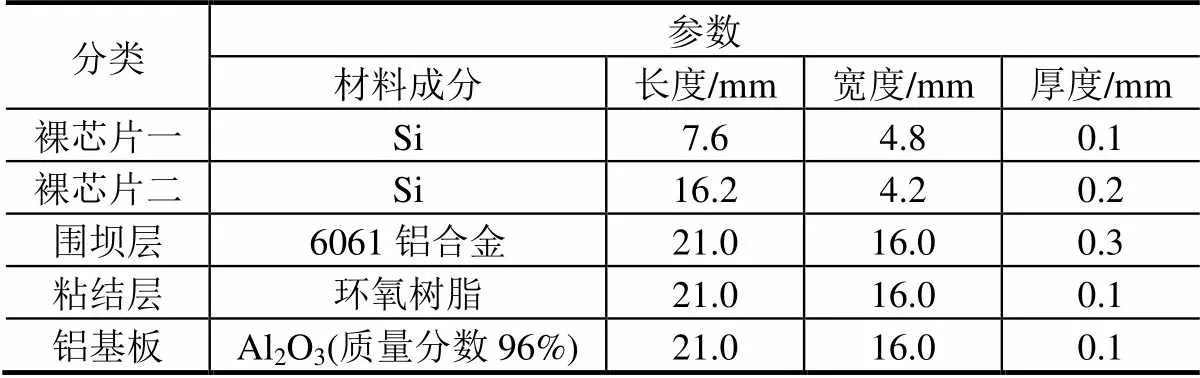

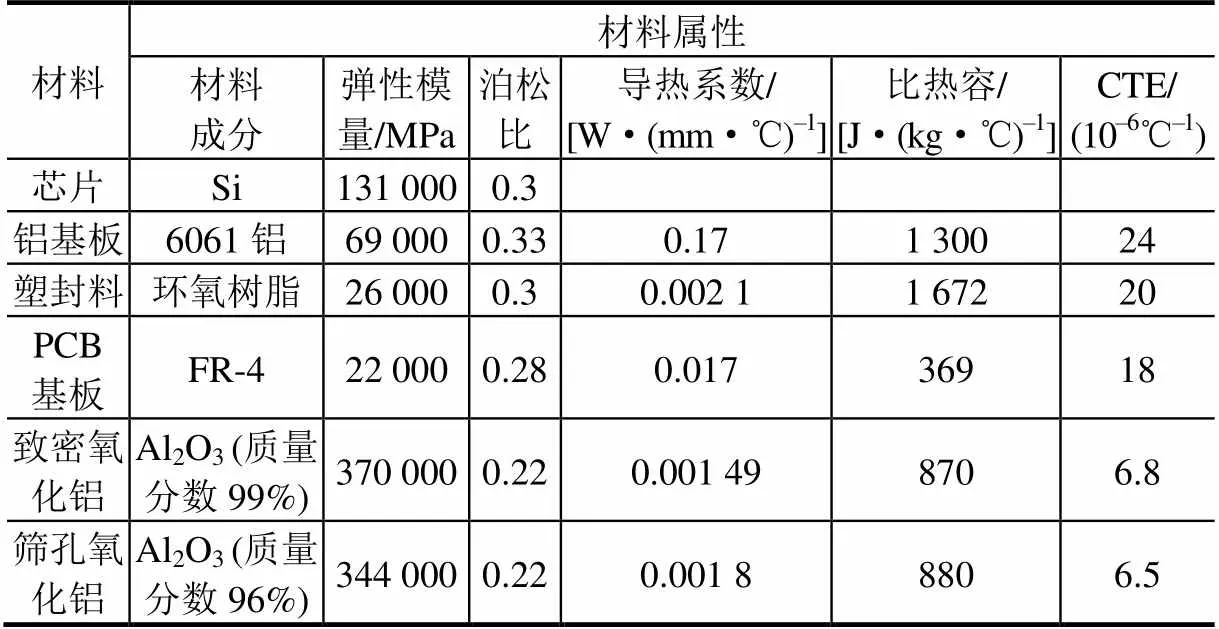

对单层COB结构、阵列COB结构、芯片堆叠及芯片下置结构建立模型,模型结构较复杂,采用自动网格建立法来建立,各层结构参数如表1所示。

表1 各层结构参数

为提高数值模拟的分析效率,建立的模型基于以下假设:

1) 除硅芯片参数为非线性,且其参数随温度变化较大外,其余材料均为线性均匀材料。

2) 引线键合所用金线尺寸相对封装体来说极小,其对整体应力分布影响很小,建模时忽略金线结构。

3) 假设室温25℃为初始状态,忽略此温度下封装体内极小的残余应力的影响。

4) 假设材料间的接合为完全结合,材料为均匀材料。

5) 在固化过程中结构整体温度相同,由于固化时器件整体放入温箱内,且器件体积较小,热传导较快,因此封装体整体温度基本与外界温度相同。

6) 对于对称结构取其1/2对称的模型,边界施加对称约束即可。分析模型所考虑的结构包含:芯片,基板,FR-4,填胶。

在固存模组的三维堆叠封装中,封装体是由多种不同材料组成,包括PCB基板、环氧树脂胶、硅芯片、铝氧化基板等,封装体中各材料的热学、力学参数对于封装体的整体稳定性十分重要,在有限元分析中也需要材料的热力学参数来作分析计算。通过查阅材料手册及产品手册,各组件所用的材料参数如表2所示。

表2 材料参数

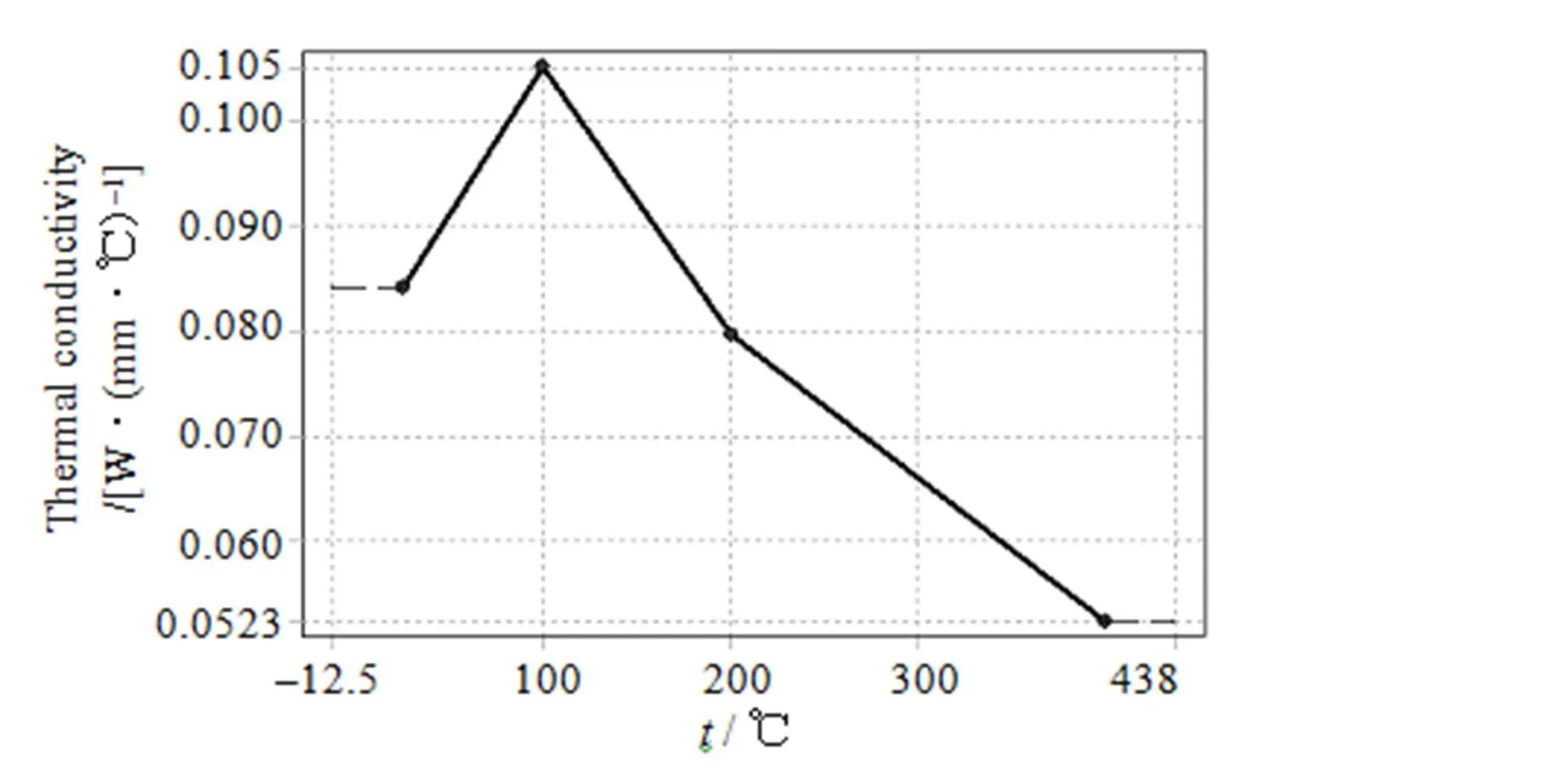

其中硅芯片的CTE、热传导系数、比热容参数会随温度而改变,具体参数如图2所示。

(a) 密度曲线

(b) CTE曲线

(c) 热导率曲线

(d) 比热容曲线

图2 硅芯片材料参数

Fig.2 Material parameters of the silicon chip

单元类型的选取直接影响着数值模拟的结果,是有限元分析精度的关键因素之一,因此对于单元属性的合理选择和控制是获得合理分析结果的前提。实体结构SOLID186单元适用于热-应力场耦合分析仿真,该单元具有二次位移函数,因此为线应变等参单元,符合要求。

3 计算结果及讨论

3.1 层间围坝结构优化分析

热应力引起的翘曲问题是三维堆叠封装区别于其他封装体的主要特征之一,目前解决热失配应力的方法主要有以下两种:一是通过选用参数性能匹配的材料,改进封装工艺;另一种方法即在热应力分析的基础上,对封装的结构进行合理的设计,减小应力集中现象,对应力集中区通过结构设计进行补偿,通过使用铝基板及铝丝打线实现材料的优化匹配,材料的优化还可以通过研发新的材料,但是此方法短期内难以实现。对封装结构进行合理设计不仅研发周期短,而且可以有效减小应力集中,减少应力引起的翘曲形变,从而加强器件的稳定性。

在对固态存储器样品模组进行三维堆叠封装时,裸芯片通过引线键合工艺连接到铝氧化基板上,通过铝基板布线将各层裸芯片根据电学要求互连起来,最后各层结构堆叠灌封,完成器件的制备。在实际制作工艺中,由于铝氧化基板的强度较弱,灌封时在温度循环下极易产生翘曲变形。

在单层COB结构中,下层铝氧化基板的主要成分为氧化铝,其CTE为(6~7)×10–6/℃,芯片为硅基裸芯片,其CTE为(2~3)×10–6/℃,而COB结构中上层材料为环氧树脂塑封胶,其CTE为(20~25)×10–6/℃,可见上下层结构的CTE是十分不匹配的。塑封胶的玻璃转化温度g为125 ℃,在25~125 ℃的温度循环中,CTE失配是上下层产生热应力失配,应变不同步,从而产生翘曲变形。翘曲会引起芯片机械性破坏、断层、裂纹等一系列可靠性问题。

为了提高基板的力学性能,降低叠层的翘曲,设计时在层间设置围坝结构,为减少异种材料间的热应力,围坝使用与铝基板同样的材料铝合金。增设围坝建立的数学模型如图3所示,为了提高环氧树脂胶在层间的结合力防止分层,围坝的外层使用锯齿状结构。

(a) 无围坝结构 (b) 有围坝结构

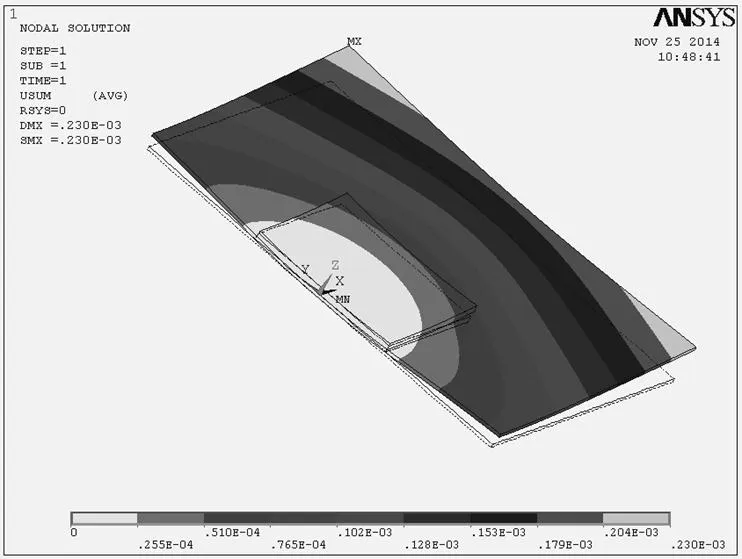

以室温为平衡状态,在25~125 ℃温循中模拟所得COB结构最大等效应力与翘曲形变量如表3所示,应力分布如图4所示。

表3 围坝对COB影响分析表

(a) 无围坝结构

(b) 有围坝结构

图4 铝氧化基板翘曲变形图

Fig.4 The warping of alumina substrate

由表3可知,围坝结构对于降低COB的翘曲变形量以及减小结构中的应力点有明显效果。在室温25 ℃至灌封胶玻璃转化温度125 ℃的温度循环中,由于围坝结构增加了基板的强度,翘曲变形量由0.184 mm降至0.134 mm,封装体内最大等效应力由336 MPa降至160.5 MPa,提高了器件的可靠性。

图5为通过TELTEC公司的Akrometrix热变形外貌检测仪对COB结构进行热变形翘曲测量的结果,测量结果显示优化后结构翘曲量为0.142 mm,与仿真结果相符合。

(a) Akrometrix测试腔

(b) 测试结果

图5 COB翘曲测量

Fig.5 Warping experiments of COB

3.2 铝基COB三维堆叠应力分析

通过单层COB应力模拟分析可知,加入围坝结构可有效抑制基板的翘曲变形,但单层COB可自由形变,不受约束,相比之下三维堆叠结构存在层与层间的约束,芯片受到的应力增大。为验证铝基COB三维堆叠结构的合理性,对双层及四层铝基COB堆叠结构在温度循环下的结构应力进行模拟分析。

双层及四层堆叠结构为有围坝铝基COB结构根据所需层数堆叠,然后整体真空灌封、固化,应力模拟结果如图6所示。由图可知,由于三维结构的约束,层间存在应力约束,芯片中心处应力较小,以这个最小值位置为中心,离这个中心越远热应力就越大,应力最大值出现在顶层芯片的边缘尖角处。这是因为水平方向芯片离模块的各个边界距离都差不多,各个方向受到的热应力均衡,因此芯片上的最大热应力出现在四个边角上。

(a) 双层堆叠

(b) 四层堆叠

图6 COB叠层应力场

Fig.6 Stress distribution of COB layers

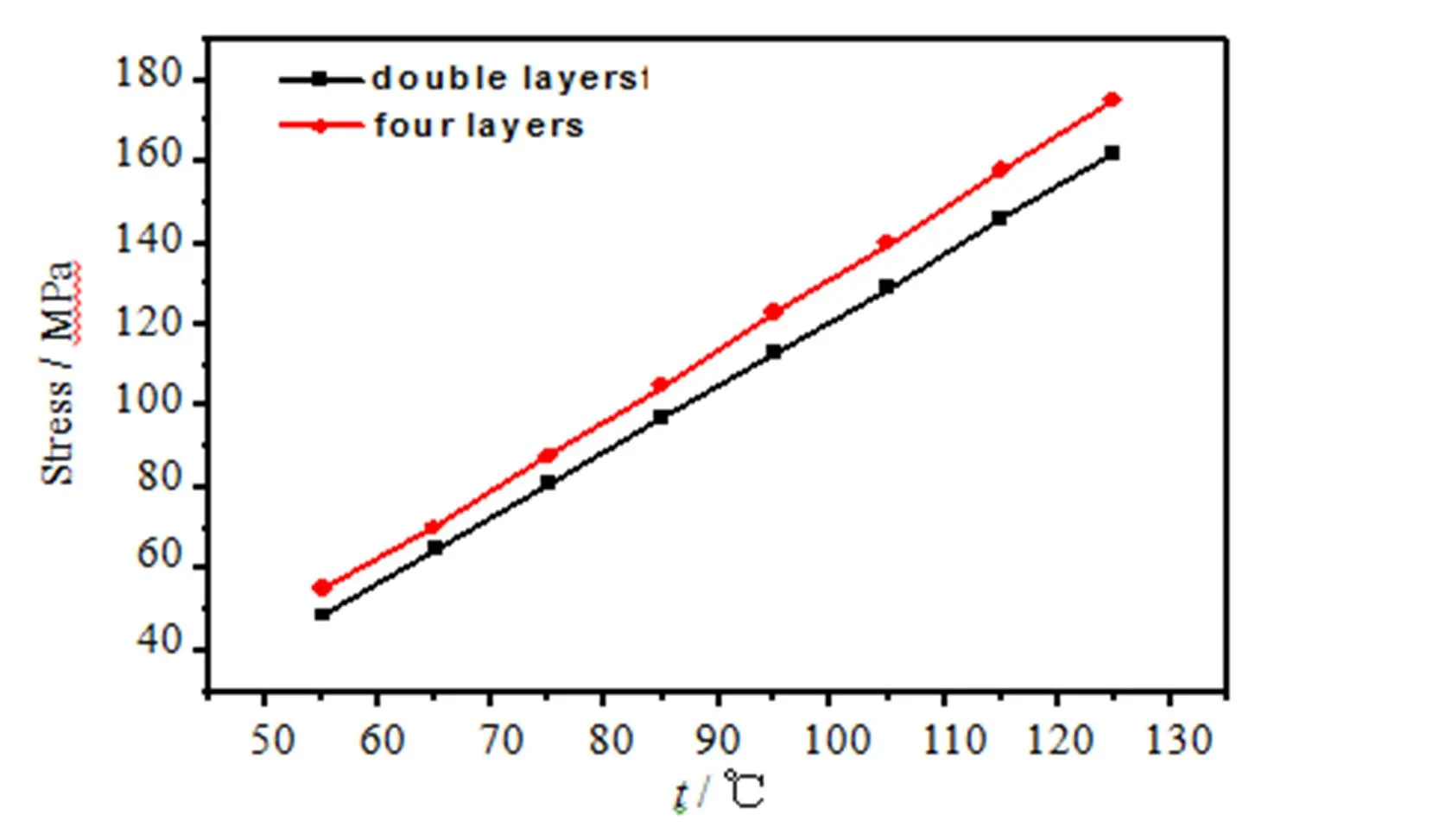

若芯片边角热应力过大,可能造成芯片过应力毁损,模拟得出不同温度下芯片边角最大应力值如图7所示。由图可知,芯片边角热应力随着温度的提高而增加,且随着堆叠层数的增加,最大热应力增加。这是因为在堆叠结构中,芯片除了受基板的约束,还受到上下层COB及灌封胶的约束,因此热应力增加。相应的,通过高精度对准堆叠,层与层之间实现互补制约,进一步减小结构的翘曲变形。四层堆叠结构在25~125 ℃温循中最大变形量由两层的0.107 mm降至0.081 mm,最大等效应力由162 MPa升至175 MPa,但仍低于硅芯片的断裂强度。由于多层堆叠结构具有最小的翘曲形变,固存模组的封装结构即采用含围坝的多层COB堆叠结构形式。

图7 不同温度下COB叠层最大应力值

3.3 三维封装T型互连结构可靠性分析

侧边布线采用T型连接的形式实现不同层之间的互连,如图8所示,通过金属化层实现层间电信号的连接,使用激光雕刻的方式对侧边进行布线。T型连接方式能够有效利用封装空间,灵活地实现层间的布线连接,与基板的引脚实现可靠的结合。但是同时,T型连接方式也存在缺点,由于不同层封装结构间CTE的失配,封装容易发生翘曲变形,从而在连接处产生应力,当应力超过接合强度时就会发生开裂,使器件失效。三维铝封装固态存储器立方体的侧面共分布有250个连接端子,其中200个为铝连接端子。有必要对T型连接处的应力场分布及其影响因素进行模拟分析。

图8 T型连接示意图

连接铝导带如图9(a)所示,侧面互连铝端子呈梯形结构。铝端子上底为Al/环氧树脂界面,两腰及下底为Al/Al2O3界面。侧面梯形结构是在草酸溶液中选择性氧化而成。对于Al/环氧树脂界面,由于两种材质CTE相近(分别为24×10–6/℃和22×10–6/℃),其交界面热失配应力较小,通过有限元仿真如图9(b)所示,可得其应力仅为15.1 MPa,不易产生裂缝和错位。铝导带表面与环氧树脂结合力也较牢固,因此该界面稳定可靠。

(a) 梯形结构互连铝端子剖面图

(b) “ T”型连接应力有限元仿真

图9 铝端子及应力仿真图

Fig.9 The cross-section and stress simulation of aluminum conduction band

对于Al/Al2O3界面,两种材质的CTE差异较大(分别为24×10–6/℃和(11~12)×10–6/℃),其交界处CTE失配热应力较大,有限元仿真可得其应力值为139 MPa。但由于Al/Al2O3界面除了Al/Al2O3之间的化学键合力外,还存在Keller-Hunter-Robinson结构[9],产生足够强的粘合力以抵抗应力引起的变形,使该界面难以产生滑移或错位,为后续金属化提供稳定的界面。

在铝导带端子表面化学镀Ni,再电镀Ni/Au,经过激光雕刻后形成的T型连接结构。侧面经Ni金属化后,形成了Al/Ni异质金属连接,与易产生Kirkendall孔洞缺陷[10]的Au/Al异质金属连接相比,Al/Ni连接是一种可靠的异质金属连接[11]。

3.4 试验验证

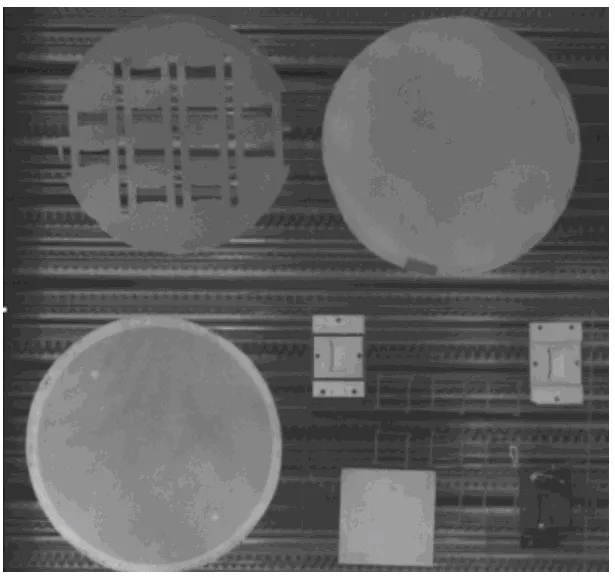

由模拟分析可知,通过铝基COB与围坝的交错堆叠结构可获得稳定可靠的三维封装结构,侧边互连可靠。根据模拟所得三维铝封装的优化结构进行试验,首先利用选择性穿透阳极氧化工艺将铝圆片氧化成内埋铝通柱/布线互连结构的铝基板,经测试导体间的绝缘电阻均大于1011Ω,满足GJB548B/2005方法1003绝缘电阻的要求;在铝基板上贴装芯片,采用铝引线键合,实现芯片与铝基板互连,制作出铝基COB基板;使用热真空灌封的方式将多块铝基COB基板堆叠灌封制作出三维灌封立方体;再对三维灌封立方体进行表面金属化处理形成Ni/Cu/Ni/Au膜层,最后使用紫外激光以0.592 W的功率直写电路图形,实现侧面垂直互连,制得固存样品。该三维铝封装存储器外形尺寸为13.6 mm×19.0 mm×8 mm,共有50根引脚,如图10所示。

图10 三维铝封装固存

将制作所得的固存通过制样观察T型互连截面如图11所示,可见铝基板无明显弯曲,铝基板与灌封体无分层等缺陷,且铝端子与侧面金属化层连接良好,无断裂现象。进行读写测试,包括读ID、读坏块、IO线测试、全空间写入0×55并读出检验测试、全空间写入0×AA并读出检验测试、全空间依次写入0×0,0×01,0×02,…,0×FF等累加值并读出检验测试,测试全部通过,说明芯片工作良好,三维铝封装结构及侧边电性能互连可实现固存的三维封装。依据GJB—548B—2005方法1010.1温度循环试验的要求,在–55~+125 ℃的温度下循环50次,再次进行读写测试,全部通过,说明T型互连结构可靠。

图11 T型连接

4 结论

应用ANSYS有限元方法对多层COB堆叠及侧边T型互连结构的应力分布进行模拟,并进行试验验证,结果表明:

(1)在室温25 ℃至灌封胶玻璃转化温度125 ℃的温度循环中,围坝结构可增加基板强度,翘曲变形量由0.184 mm降至0.134 mm,封装体内最大等效应力由336 MPa降至160.5 MPa,提高了器件的可靠性;

(2)四层堆叠结构在25~125 ℃温循中最大变形量由两层的0.107 mm降至0.081 mm,最大等效应力由162 MPa升至175 MPa,应力最大值在芯片顶角;

(3)模拟所得T型结构中Al/环氧树脂界面、Al/Al2O3界面及Al/Ni/Au界面稳定可靠,观察样品截面铝基板与灌封体无分层等缺陷,且铝端子与侧面金属化层连接良好,经–55~+125 ℃温循后读写功能正常,T型互连结构可靠。

[1] NAVAS K, SEUNG W, AKELLA G K, et al. Development of 3-D stack package using silicon interposer for high-power application [J]. IEEE Trans Adv Pack, 2008, 31(1): 44-50.

[2] XIE H Q, LI J, SONG J, et al. A 3D package design with cavity substrate and stacked die [C]//Proceedings of 14th International Conference on Electronic Packaging Technology. NY, USA: IEEE, 2013: 64-67.

[3] 夏艳. 3D集成的发展现状与趋势 [J]. 中国集成电路, 2011, 146: 23-28.

[4] ZHENG J Y, ZHANG Z S, CHEN Y G, et al. 3D stacked package technology and its application prospects [C]// Proceedings of International Conference on New Trends in Information and Service Science. NY, USA: IEEE, 2009: 528-533.

[5] 蒋进. 三维电子封装微凸点的电沉积制备及低温固态互连技术研究 [D]. 上海: 上海交通大学, 2010.

[6] 邓小军, 曹正州. 应用于三维封装中的硅通孔技术 [J]. 电子与封装, 2012, 12(9): 18-23.

[7] SAKUMA K, ANDRY P S, DANG B, et al. 3D chip stacking technology with low-volume lead-free interconnections [C]//Proceedings of 57th Electronic Components and Technology Conference. NY, USA: IEEE, 2007: 627-632.

[8] 刘凯, 王盈莹, 王立春. 铝阳极氧化技术制作三维铝封装基板 [J]. 电子元件与材料, 2015, 34(5): 19-22.

[9] KELLER F, HUNTER M S, ROBINSON D L. Structural features of anodic oxide films on aluminum [J]. J Electrochem Soc, 1965, 100: 55-56.

[10] 邹建, 吴丰顺, 王波, 等. 电子封装微焊点中的柯肯达尔孔洞问题 [J]. 电子工艺技术, 2010, 31(1): 1-5.

[11] 纪成光, 陈立宇, 袁继旺, 等. 化学镍钯金表面处理工艺研究 [J]. 电子工艺技术, 2011, 32(2): 90-94.

Structure design and connection reliability of 3D aluminum package

LUO Yan, REN Weipeng, ZHOU Yi, WANG Lichun

(Shanghai Aerospace Electronic Technology Institute, Shanghai 200240, China)

Focusing on the issues of connection reliability caused by thermal stress mismatch in 3D package, a method of edges connection based on alumina substrate was proposed. The stack and pouring model for COB(Chip on Board) was established with ANSYS software. The stress distribution of single layer COB and multiple layers COB was studied and the packaging structure was optimized, and the practical test was conducted. The results show that interlayer dam can suppress the warping effectively. The maximum deformation of four layers COB structure with interlayer dam is 0.081 mm after 25-125 ℃ temperature cycle. The maximum equivalent stress is 175 MPa which is within the breaking strength limitation of silicon chip. There is no cracks between layers of the structure and the read-write performance of the solid-state memory is normal after temperature cycle.

alumina substrate; 3D package; COB stack; interlayer dam; stress distribution; edges connection

10.14106/j.cnki.1001-2028.2016.10.016

TM205

A

1001-2028(2016)10-0072-06

2016-07-22

王立春

国家科技重大专项项目(课题级)资助(No. 2014ZX02501016)

罗燕(1987-),女,湖北黄石人,工程师,从事微电子封装技术研究,E-mail: luoyan1120@qq.com;

王立春(1967-),男,安徽定远人,研究员,从事微电子封装技术研究,E-mail: wanglichun0482@163.com。

网络出版时间:2016-09-29 10:11:03

网络出版地址:http://www.cnki.net/kcms/detail/51.1241.TN.20160929.1011.016.html

(编辑:陈渝生)