CMOS工艺中等离子体损伤WAT方法研究

陈培仓,徐政,李俊(中国电子科技集团公司第58研究所,江苏无锡214035)

CMOS工艺中等离子体损伤WAT方法研究

陈培仓,徐政,李俊

(中国电子科技集团公司第58研究所,江苏无锡214035)

WAT(Wafer Accept Test)即硅圆片接收测试,就是在半导体硅片完成所有的制程工艺后,对硅圆片上的各种测试结构进行电性测试,它是反映产品质量的一种手段,是产品入库前对wafer进行的最后一道质量检验.随着半导体技术的发展,等离子体工艺已广泛应用于集成电路制造中,离子注入、干法刻蚀、干法去胶、UV辐射、薄膜淀积等都可能会引入等离子体损伤,而常规的WAT结构无法监测,可能导致器件的早期失效.设计了新的针对离子损伤的WAT检测结构,主要是缩小了栅端面积,在相同天线比的情况下天线所占面积呈几何级下降,使得评价结构放置在划片区变得可能.

CMOS;WAT;等离子体;损伤;半导体工艺

1 引言

随着半导体技术的发展,等离子体工艺已广泛应用于集成电路制造中,比如等离子体刻蚀、等离子体增强式化学气相淀积、离子注入等.它具有方向性好、反应快、温度低、均匀性好等优点.但是它也同时带来了电荷损伤,随着栅氧化层厚度的不断降低,这种损伤会越来越影响到MOS器件的可靠性,因为它可以影响氧化层中的固定电荷密度、界面态密度、平带电压、漏电流等参数[1~3].

尽管已有大量关于等离子体损伤方面的研究报道,讨论了主要的损伤机制以及可能发生的工艺步骤,目前对于等离子体损伤的圆片级监控却研究较少,业界主要使用WCM(Wafer Charging Monitors)公司的CHARM-2圆片来检查工艺过程产生的等离子体损伤[4].本课题旨在研究等离子体的WAT监控方法,吸取前人的经验,设计合理的监控结构,将等离子体损伤放到常规的圆片级监控结构里,提出评价方法,填补此监控的空白.

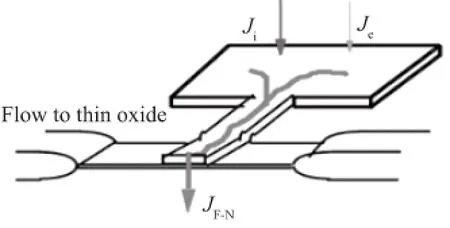

2 等离子体损伤的天线效应

如图1所示,如果栅氧区较小,而栅极面积较大,大面积栅极收集到的离子将流向小面积的栅氧区,为了保持电荷平衡,由衬底注入栅极的隧道电流也需要随之增加,增加的倍数是栅极与栅氧面积之比,放大了损伤效应,这种现象称为"天线效应"[5].

带天线器件结构的大面积离子收集区(多晶或金属)一般位于厚的场氧之上,因此只需要考虑薄栅氧上的隧道电流效应.大面积的收集区称为天线,带天线器件的隧道电流放大倍数等于厚场氧上的收集区面积与栅氧区面积之比,称为天线比.

举个例子,假定天线比为1000∶1,离子流为1mA/cm2,则天线收集到的离子流为1 mA/cm2X1000=1 A/cm2.为了保持电荷平衡,隧道电流的密度将相应地从1 mA/cm2升高为1 A/cm2,不仅如此,栅氧化层上的电势差也随之增加.如果10 MV/cm的场强可以产生1 mA/cm2的隧道电流,那么产生1 A/cm2的隧道电流则需要13 mV/cm的电场强度,这样一来,氧化层上的电压降就不再是10 V而变成了13 V.对于栅氧化层的击穿,不仅取决于流经栅氧化层的总电荷量,电场强度也起着重要的作用.天线结构不仅可以放大隧道电流,也会放大场强应力,因此,天线结构可以放大损伤,使损伤加重.

图1 天线效应示意图

对于栅注入的情况,隧道电流和离子电流之和等于等离子体中总的电子电流.因为电流很大,即使没有天线的放大效应,只要栅氧化层中的场强能产生隧道电流,就会引入严重的等离子体损伤.

3 实验方法设计和实验方案

经过对等离子体损伤机理进行深入的研究以后,我们知道天线结构可以直观有效地放大损伤的严重程度,而在正常的电路设计中栅端一般都需要开孔经多晶或金属互连线引出做功能输入端,就相当于在薄弱的栅氧化层上引入了天线结构,所以在正常流片及WAT监测时所进行的单管器件电性测试和数据分析无法反映电路中实际的等离子体损伤情况,目前比较主流的对等离子体损伤的评估一般都是采用全片式测试模块排布的专用测试片,在离子设备出现故障、产品出现损伤性异常或者定周期进行专用测试片进线工艺,经各道离子工艺以后采集大量的数据进行等离子体损伤的评估,来反应工艺中的损伤情况.但是可以看到这种评估方法的不及时性和滞后性,因此对WAT版图进行优化设计,在保证天线比的基础上缩小天线面积,使其能被配置在60 μmX60 μm的划片槽内,实现实时的圆片级等离子体损伤监测和分析.

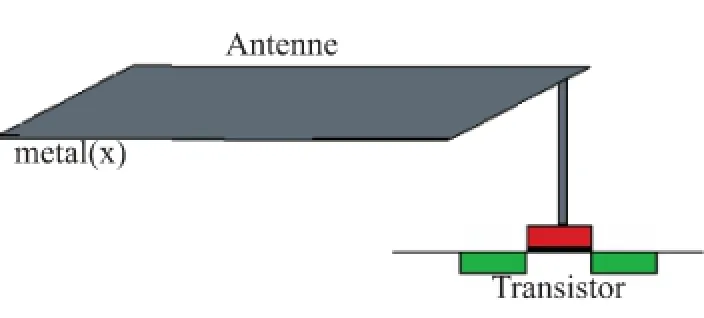

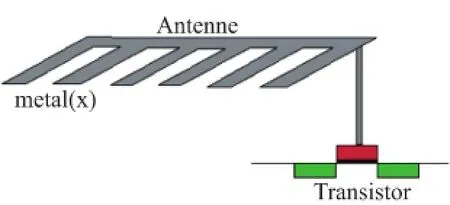

天线从结构上可分为平板结构和梳状结构两种,与电容结构相似,如图2所示为平板天线结构,图3所示为梳状天线结构.综合我们的工艺过程,在刻蚀、淀积、注入等等离子体工艺时,梳状的天线结构更容易受到损伤,因为梳状天线增加了侧面面积,因此在天线结构选择上我们将选择梳状结构进行工艺实验.

图2 平板天线结构

图3 梳状天线结构

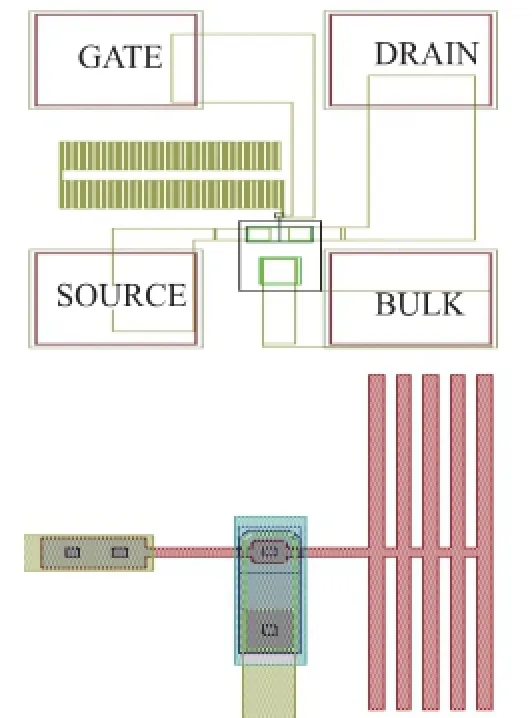

考虑目前我们典型0.8 μm的工艺生产线,若在常规监测用单管(W/L=20/0.8 μm)上外挂10 K天线的话,则天线面积达到160 000 μm2;以梳状结构配置在60 μmX60 μm划片槽里的话,则天线长度超过6 mm,而实际光刻机曝光范围是1.2 mmX1.2 mm以下,划片槽还要放置很多的对位、游标、套刻等标记以及一些常规的监测模块,所以无法忍受这种大面积的天线配置.考虑到等离子体的充电损伤主要是通过天线收集离子电荷然后经由薄栅氧化层放电从而导致损伤的原理,对带天线的MOS器件进行优化.首先在版图上略去Source和Drain端,只保留Gate和Bulk,另外将Gate面积从20 μmX0.8 μm缩小为0.8 μmX0.8 μm的单孔结构,可有效地将天线面积缩小25倍,使得将其配置在划片槽变得可行,常规带金属天线结构MOS管和优化后的评价结构如图4所示.

为了验证优化结构的有效性,设计了比较容易引入损伤的多晶工艺、N+源漏工艺、P+源漏工艺、接触孔工艺和金属工艺天线评价结构,在天线设计时采用梳状结构,并且同时配置了1 K和10 K两种天线比结构以评估损伤影响.另外在工艺过程中,对栅氧化层的厚度进行了拉偏,分别安排了12.5nm、15nm和20nm厚度实验,以评估等离子体损伤对不同栅氧化层厚度的影响.

图4 带金属天线结构的MOSFET和优化结构

4 实验数据采集和结果分析

4.1数据采集方法

按照ASTM F616-86(Standard Method for Measuring MOSFET Drain Leakage Current),ASTM F617-86(Standard Method for Measuring MOSFET LinearThresholdVoltage),JEDECJEP132,ASTM F616-86,617-86&1096-87(Standard Method for Measuring MOSFET Drain OFF Current)测试标准方法拟采集影响器件特性的关键参数ileak,并参考JESD28-A标准,采用Y(t)=[P(A)-P(0)]/P(0)X100%<100%(P (A)为带天线结构器件参数,P(0)为无天线结构器件参数)作为器件参数的评价标准,分析不同天线比天线结构对器件损伤程度的影响情况.

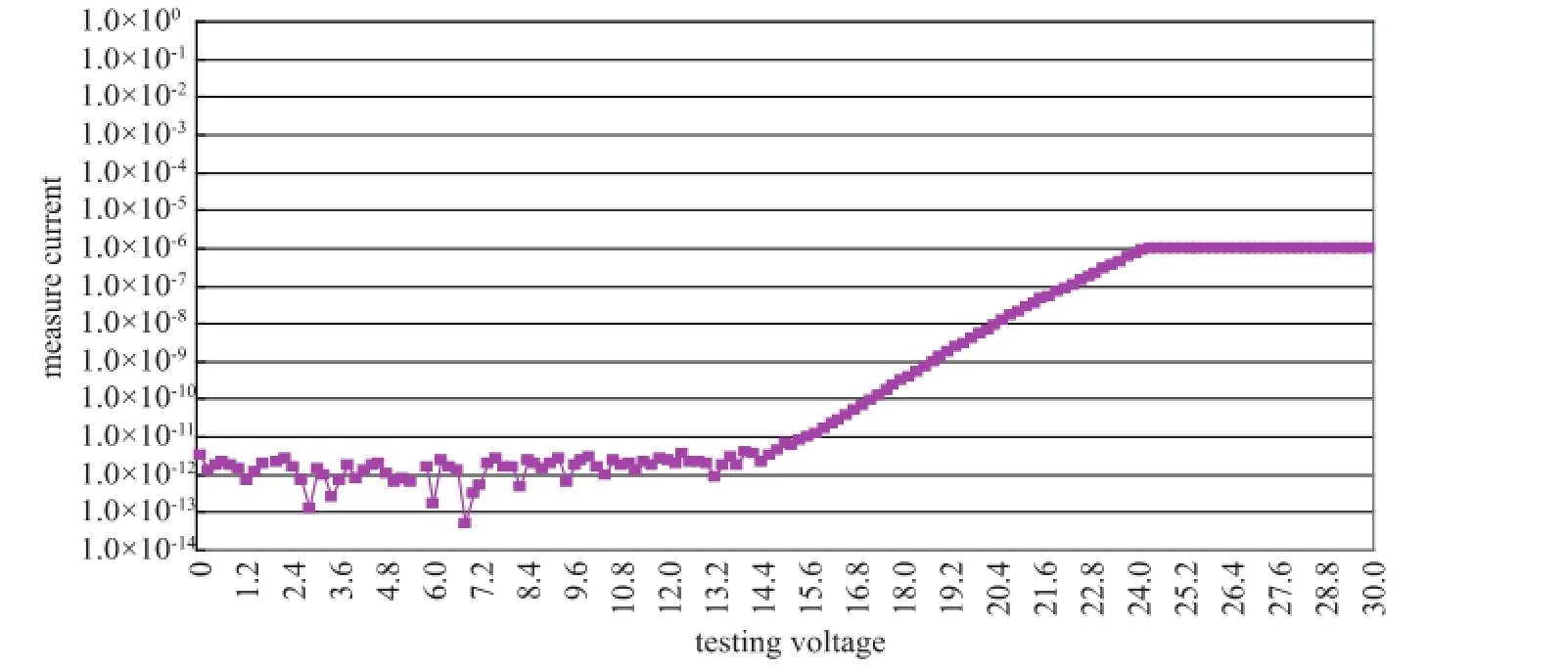

在进行数据采集的时候,考虑到栅氧化层的I-V特性(如图5所示)并不是线性的,当栅氧化层测试电压低于14.4 V时(电场强度低于7.2 mV/cm),无隧道电流产生,测试到的只是氧化层漏电流,且结果波动较大,难以分析,只有在发生毁坏性损伤或其他异常时才会在低电压下产生大电流.我们知道只有在氧化层所受电场强度接近10mV/cm时才会产生隧道电流[6],结合如图5所示的实际击穿特性曲线,20 nm栅氧化层厚度测试电压选择20 V,同理15 nm和12.5 nm厚度的栅氧化层测试电压分别选择15 V和12.5 V.

图5 20 nm栅氧电容击穿特性曲线

图6 无天线结构结果

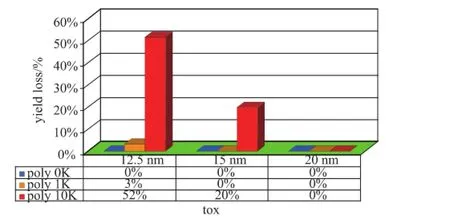

图7 多晶层次引入天线结果

4.2实验结果

无天线结构电流结果显示栅电流大小只与栅氧化层的厚度有相关性,可作为引入天线结构工序的评价基准电流.

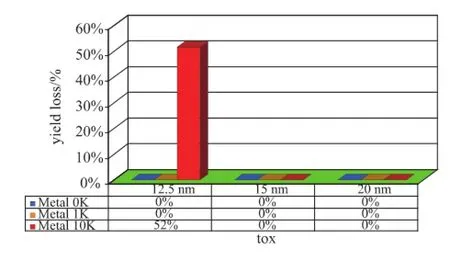

在多晶层次引入天线结构后,随着天线比的增加,等离子体损伤明显加剧,且当栅氧比较薄时,受到的损伤会变严重.当天线比为10K、栅氧厚度为12.5nm时,失效很严重,yield loss高达52%.当栅氧达到典型0.8 μm工艺厚度20 nm时候,即使引入10 K的多晶天线,也未发现有失效点.多晶天线结果说明了优化版图设计结构能监测到工艺的损伤情况,对于我们的典型0.8 μm工艺平台,如果要向下延伸到0.6 μm工艺,即当栅氧厚度要做到12.5 nm时,则要考虑损伤的引入,需要同时考虑多晶工艺设备的优化或替换.

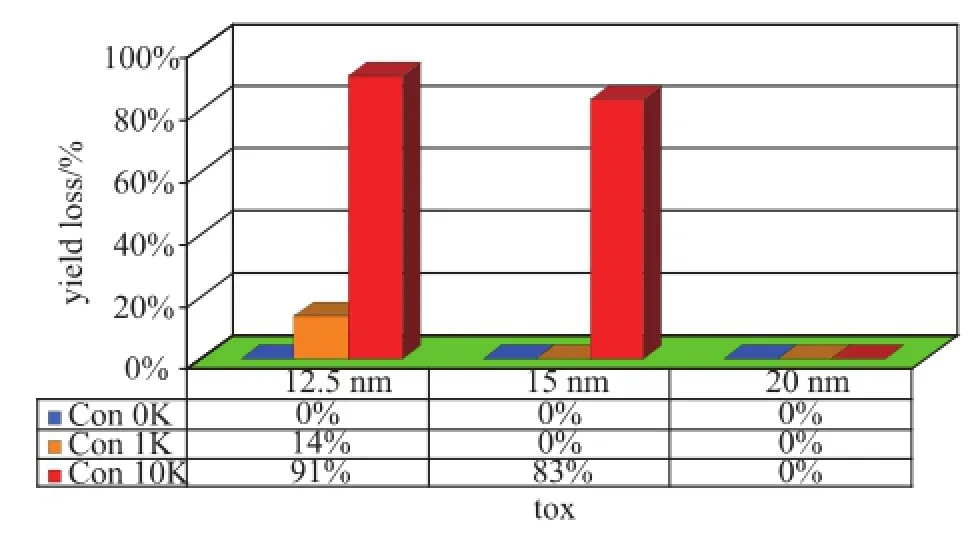

图8 孔层次引入天线结果

孔天线设计的时候,在天线多晶上开接触孔,引入孔腐蚀的等离子体充电电荷,得到孔腐蚀的充电损伤.结果表明随着天线比增加,充电损伤加剧,即使在我们典型的0.8 μm工艺栅氧厚度15 nm时,如果外挂上10K的天线以后也可能引入很严重的损伤,yield loss高达83%,需要引起重视,进行设计规则的优化,规避损伤风险.

在孔层次天线中我们可以很明显地看到,在薄栅氧的时候,大天线的情况下损伤特别严重,基本满圆片超标.因为此结果不仅引入了孔层次的损伤,而且引入了多晶层次的损伤,因为孔在开在外挂的多晶天线上的,那么总的损伤就是多晶加上孔两个层的损伤引入之和,所以孔天线引入的损伤大于多晶天线损伤,这是符合理论预期的.

图9 金属层次引入天线结果

从金属天线比较结果来看,大部分情况下都没有损伤引入,但是当栅氧为12.5 nm、天线比为10K时,出现52%的yield loss,主要呈中心区域性异常分布,可能是由于金属刻蚀腔体中央高电势差所致.

图10 N+SD层次引入天线结果

图11 P+SD层次引入天线结果

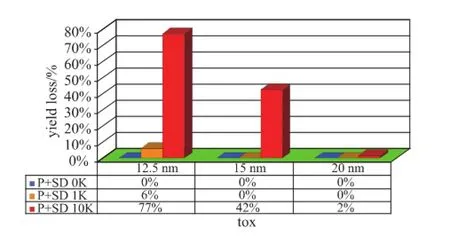

N+源漏天线是在栅多晶天线上引入了N+源漏的高能量注入损伤.从结果来看,损伤受外挂天线影响比较大,1K天线结构、12.5 nm栅氧厚度也只有17%的yield loss;但是如果将天线增加到10K、12.5 nm栅氧厚度,yield loss增加到95%,15 nm栅氧厚度yield loss也增加到了45%.

与N+源漏天线引入方法相似,P+源漏天线是在栅多晶天线上引入了P+源漏的高能量注入损伤,从结果来看,基本同N+源漏天线损伤情况相似,不同的是当15 nm栅氧厚度、10K天线时损伤分布不同,P+源漏注入损伤主要分布在圆片的边缘,可能是边缘电势差较大导致的.

5 结论

从实验结果来看,随着天线比的增加,损伤程度明显加重,这给我们在制定设计规则的时候多了一个数据参考.另外对器件特性比较敏感的多晶、源漏和孔层次,相对于金属来说等离子体损伤较重;氧化层的厚度不同损伤程度也不同,比较薄的氧化层受到损伤后质量下降明显,比较厚的20 nm栅氧在外挂10K的天线后基本都无损伤失效点,但从理论上来说如果氧化层继续变薄到3 nm以下,基本不用再考虑充电损伤问题,因为对于3 nm厚度的氧化层而言,电荷积累是直接隧穿越过氧化层势垒,不会在氧化层中形成电荷缺陷.

本次实验结果反映了优化测试结构的有效性,可以监控离子体工艺损伤情况,由于设计结构的简单和兼容性,可以配置在大部分产品的晶片划片区,对工艺中的等离子体损伤进行实时的监控,而不是像业界通用的CHARM-2评估测试圆片那样定期评估.当然从定量分析上看,无法像CHARM-2圆片那样可以得到更具体的数据,甚至可判断积累的电荷电性.

[1]GABRIEL C T,McVITTIE J P.How plasma etching damages thin gate oxide[J].Solid State Tech,1992,35(6)∶81-87.

[2]FANG S,McVITTIE J P.Thin-oxide damage from gate charging during plasma processing[J].IEEE Elec Dev Letts, 1992,13(5)∶288-290.

[3]W Lukaszek.WAFER CHARGING DAMAGE IN IC PROCESS EQUIPMENT[C].ECS International Semiconductor Technology Conference,Shanghai,China,2001,5. 27-30.

[4]W Lukaszek,M J Rendon,D E Dyer.Device Effects and Charging Damage∶Correlations Between SPIDER-MEM and CHARM○R-2[DB/OL].1994 4th International Symposium on Plasma Process-Induced Damage,Monterey,CA, 1999.

[5]徐政,等.等离子体损伤测量方法研究[J].电子器件, 2011,(1):1-4.

[6]马良,张继.等离子工艺损伤[J].电子与封装,2006,6(4): 26-28.

Studies on Testing Plasma Damages in WAT in CMOS Technology

CHEN Peicang,XU Zheng,LI Jun

(China Electronics Technology Group Corporation No.58 Research Institute,Wuxi 214035,China)

WAT tests wafers after accomplish all semiconductor technologies to monitor the quality of products and serves as the last quality testing before delivery.Along with the development of semiconductor technology,plasma technologies have been widely applied in IC manufacturing.Ion implantation,dry etch and UV radiation may bring plasma damages that cannot be found using normal WAT and cause early failure.The article designs a new WAT structure to monitor plasma damages by reducing GATE oxide area,which dramatically reduces antenna area and enables evaluation placement.

CMOS;WAT;plasma;damage;semiconductor process

TN307

A

1681-1070(2016)06-0031-05

2016-3-28

陈培仓(1981-),男,江苏连云港人,2005年毕业于西安电子科技大学微电子学专业,工程师,现在中国电子科技集团公司第五十八研究所主要从事产品研发工作.