FPGA芯片时钟架构分析

张艳飞,谢长生,匡晨光(.中国电子科技集团公司第58研究所,江苏无锡4035; .无锡中微亿芯有限公司,江苏无锡407)

FPGA芯片时钟架构分析

张艳飞1,谢长生2,匡晨光2

(1.中国电子科技集团公司第58研究所,江苏无锡214035; 2.无锡中微亿芯有限公司,江苏无锡214072)

FPGA设计中时钟信号的设计与处理是保证系统稳定工作的重要组成部分,随着FPGA器件规模的不断增大,集成度不断提高,多时钟域管理、时钟延迟、时钟信号完整性和相位偏移等已成为影响FPGA设计的关键因素.结合微电子电路相关知识,针对Xilinx公司的Virtex4系列芯片,详细分析其时钟架构及时钟资源的特性.针对FPGA时钟设计的典型应用情况,从芯片角度给出了时钟设计与使用的一些技巧和建议.

现场可编程门阵列;时钟架构;时钟管理

1 引言

随着FPGA(Field Programmable Gate Array)器件规模的不断增大,集成度不断提高,在高密度FPGA中时钟信号的分布质量越来越重要[1],多时钟域管理、时钟延迟、时钟信号完整性和相位偏移等已成为影响FPGA设计的关键因素[2].因此在设计中使用高性能的集成时钟管理模块、高性能的时钟树结构很有必要.本文结合微电子电路相关知识,针对Xilinx公司的Virtex4系列芯片,详细分析其时钟架构及资源的特性,从芯片角度给出了时钟设计与使用的相关技巧和建议.

2 FPGA芯片时钟结构

FPGA中的时钟系统是由时钟输入/输出模块、集成时钟管理模块、时钟树组成的.它完成了FPGA中时钟的输入、输出、传输、时钟使能/禁止、时钟切换、分频/倍频、相位调节等用户所需要的时钟功能,为FPGA中各个模块如DSP、BRAM等提供工作时钟.时钟输入/输出模块完成外部时钟的输入以及将内容时钟送往FPGA外部,时钟管理模块(DCM和PLL)用来调整全局时钟的频率和相位,时钟树将时钟分布到芯片上所有时钟负载处.高性能的时钟管理模块和时钟树、时钟输入/输出模块也保证了系统工作所需要的时钟性能指标和稳定性.

3 Virtex4时钟资源

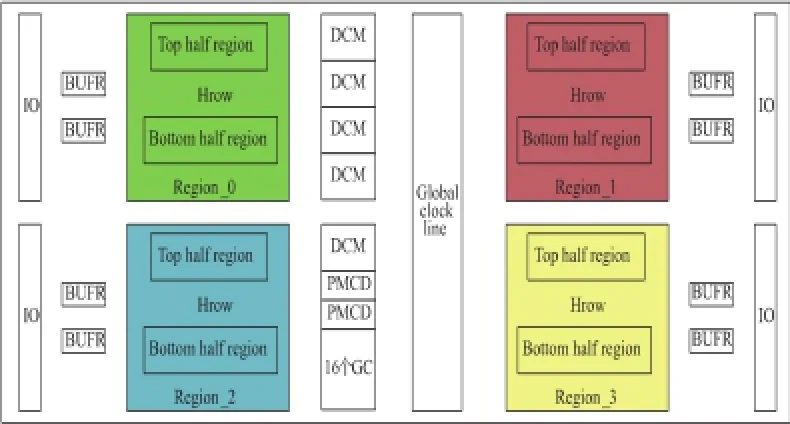

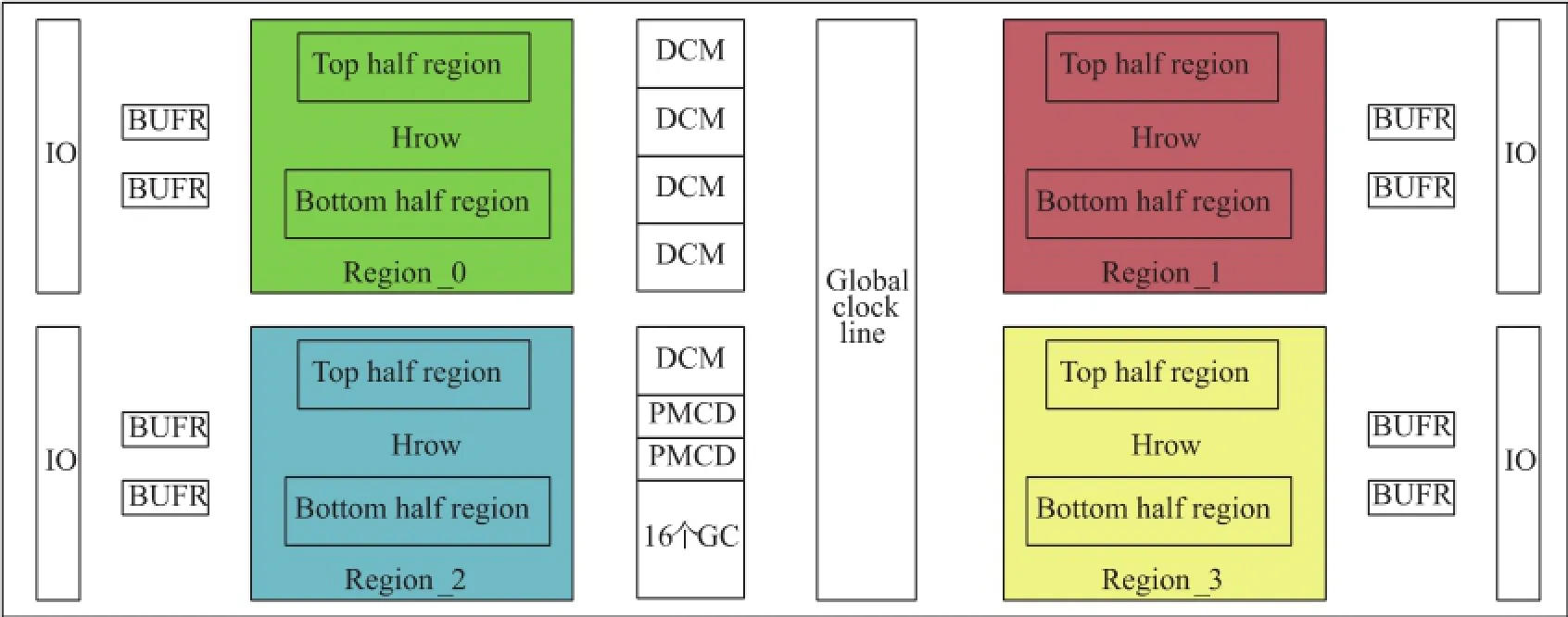

Virtex4芯片的时钟分为全局时钟资源和区域时钟资源,其资源组成如图1所示.

全局时钟是一种专用互连网络,是专为覆盖FPGA中各种资源的所有时钟输入设计的.这些网络的设计旨在降低歪斜、占空比失真和功耗并提高抖动容限.全局时钟资源主要集中在芯片中间列,中间列分布着BUFG(Global Clock Buffer)、GC(Global Clocking Port)、DCM(Digital Clock Managers)、PMCD (Phase-Matched Clock Dividers)等全局时钟资源.

区域时钟资源是在IOB(Input/Output Block)、GC周围分布有BUFIO(I/O Clock Buffer)、BUFR (Regional Clock Buffer)等时钟资源.区域时钟每个时钟区域有2个BUFIO、2个BUFR和4个CCIO(Clock Capable I/O)输入管脚.区域时钟可以驱动相邻区域中的区域时钟树.通过对区域时钟缓冲器BUFR编程可对时钟频率以1到8的任意整数进行分频(另包括一个不分频直通通道),这一功能与IOB中的可编程串行器/解串器配合,使源同步系统无需使用附加逻辑资源即可跨越不同时钟域[3].

图1 Virtex4芯片时钟资源组成

为了方便时钟控制,每个Virtex4器件分成若干个时钟区域(clock region).区域数因器件大小而异,从最小器件的8个区域到最大器件的24个区域[3],图2中灰色部分为不同的时钟区域,在时钟区域内还包含有DCM、BUFR等时钟资源.

图2 Virtex4芯片时钟资源布局

4 时钟架构中的典型用例分析

在FPGA设计中,为了成功地操作,可靠的时钟是非常关键的.设计不良的时钟在极限的温度、电压或制造工艺的偏差情况下将导致错误的行为.FPGA全局时钟路径需要专用的时钟缓冲和驱动,具有最小偏移和最大扇出能力.FPGA设计时,最好的时钟方案是由专用的全局时钟输入引脚驱动的单个主时钟,去控制设计项目中的每一个触发器.只要可能就应尽量在设计项目中采用全局时钟,因为对于一个设计项目来说,全局时钟是最简单和最可预测的时钟.以下两个时钟用例是FPGA设计中通常使用的时钟情况.

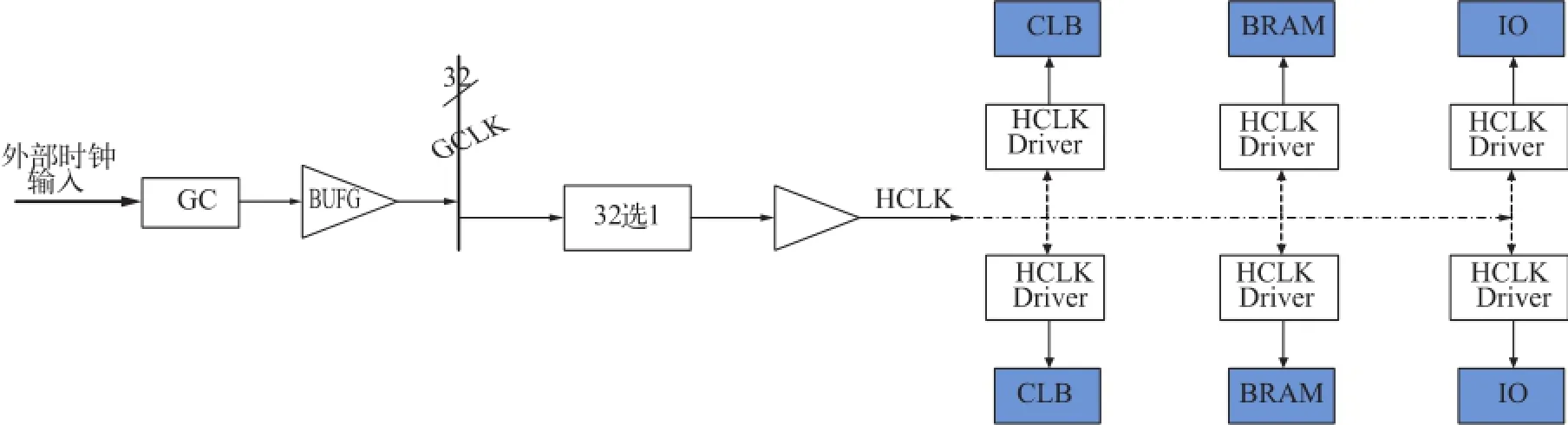

4.1GC到CLB等模块的时钟布线

FPGA设计中经常使用的案例是外部时钟从全局时钟输入PIN到达芯片内部的逻辑资源.在Virtex4器件中,以到达芯片右侧资源为例,如图3时钟从全局时钟管脚GC输入,通过BUFG到达GCLK全局时钟网络,其中BUFG驱动32根全局时钟网络,该时钟网络纵贯芯片上下部.通过32选1的选择器将时钟转换为HCLK,根据设计需要进入CLB、BRAM、IO等资源模块,其中HCLK横向为差分传输,进入CLB等模块前转换为单端时钟信号.对于一个设计良好的时钟路径,电阻性的时钟线在驱动它自身电容、走线电容和时钟负载电容的RC延迟往往能够达到1 ns左右,如果时钟随意走线,那么可能在接近和远离时钟源处的时钟产生1 ns的时钟歪斜,它往往和系统时钟周期相比拟,因此时钟分布系统必须仔细设计,以使时钟输入和各个时钟负载之间的飞行时间相等,如图3所示的鱼骨型时钟结构.

图3 GC到CLB等时钟走线

4.2CCIO到CLB等模块的时钟走线

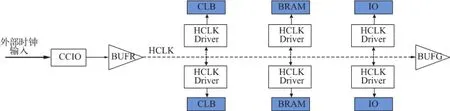

为了更好地满足数据在芯片之间的传输,采用源同步设计方案时,需使用FPGA芯片中的IO时钟系统.源同步时钟系统实现上如图4所示,时钟从CCIO引脚输入,通过BUFR到达HCLK长线,其后的时钟网络也是采用鱼骨型时钟结构,通过HCLK_Driver模块驱动输出到CLB、BRAM、IOB等模块.整个路径上时钟延迟约1.5 ns,时钟路径SKEW约0.4 ns,可以满足400 MHz时钟传输需求.

图4 CCIO到CLB等时钟走线

5 总结

FPGA设计中时钟信号的设计与处理是保证系统稳定工作的重要组成部分,一些复杂设计中需要很多时钟资源,Virtex4系列时钟资源包含全局时钟和区域时钟,全局时钟包括GC、DCM、PMCD等资源.全局时钟网络要靠BUFG驱动,将时钟信号放在时钟树上,保证到整个芯片的任意一个触发器是电延时等长的,可以减小时钟偏差.区域时钟包括CCIO、BUFR等资源,区域时钟网络靠BUFR驱动,只在本时钟区域和相邻时钟区域中使用,实现源同步.

[1]张振.FPGA内数字时钟管理模块的研究[D].西安:西安电子科技大学,2014.1-65.

[2]封彦彪,刘兴春.基于Xilinx FPGA的时钟管理设计与实现[J].电子测量技术,2010,33(10)∶52-55.

[3]Virtex-4 FPGA User Guide[EB/OL].http∶//www.xilinx.com.

Clock Architecture Analysis of FPGA Chip

ZHANG Yanfei1,XIE Changsheng2,KUANG Chenguang2

(1.China Electronics Technology Group Corporation No.58 Research Institute,Wuxi 214035,China; 2.East Technologies Inc.,Wuxi 214072,China)

In the FPGA design,the design and processing of the clock signal is an important part of the stability of the system.With the increasing size and integration level of FPGA devices,multi-clock domain management,clock delay, clock signal integrity and phase offset have become the key factors affecting FPGA design.The article presents a detailed analysis of the clock architecture and resource characteristics of the Virtex4 series chip of Xilinx Company.By referring the typical application of FPGA clock design,some tips and suggestions on clock design and usages are given.

FPGA;clock architecture;clock management

TN402

A

1681-1070(2016)06-0028-03

2016-1-26

张艳飞(1981-),女,黑龙江佳木斯人,现就职于中国电子科技集团公司第58研究所,研究方向为FPGA芯片设计.