基于UltraFlex的多时钟域电路测试方法

严华鑫(中国电子科技集团公司第58研究所,江苏无锡214035)

基于UltraFlex的多时钟域电路测试方法

严华鑫

(中国电子科技集团公司第58研究所,江苏无锡214035)

介绍了一种在UltraFlex系统上进行多时钟域电路测试的方法,利用了UltraFlex系统自身硬件设计的特点和VBT,解决系统在多时钟电路频率比较高的情况下最小公倍数频率超过测试系统规格的问题.此方法通用,可进行不规则多时钟ASIC的测试,降低了设计和测试人员测试算法设计的难度,提高了设计和测试开发速度.

多时钟域;测试方法;Ultraflex

1 引言

大规模集成电路---如专用集成电路(ASICs)和片上系统(SOCs)---出于功能或者性能上的考虑,经常采用多时钟的设计风格;尤其在电信应用领域,经常需要多个数据通路,多个微控制器和电源管理[1].微处理器(MCU)系统一般有两个时钟域,其中处理器使用较快的系统时钟,以获得较高的性能;外围逻辑使用较慢的时钟外围,以降低功耗.在多时钟设计中,一个时钟域产生的信号经常会被其他的时钟域使用,这就形成了不同时钟域之间的交叉.例如,在微控制系统中,处理器的写信号和数据是在系统时钟域产生的,而外围时钟域的寄存器用处理器的写信号作为使能信号来加载数据,这样形成了从系统时钟域到外围时钟域信号的交叉;同样的,当处理器读外围逻辑寄存器时,寄存器的值通过总线送给处理器,又形成了从外围时钟域到系统时钟信号的交叉[2].

系统中的时钟数量以及它们之间的数据迁移成为设计时必须考虑的重要因素,因为这会直接影响系统的功能、验证与测试.时钟域是指由同一时钟控制的一组时序单元,该时钟必须来自同一颗时钟树.如果有两个触发器使用的时钟来自同一时钟树的不同分支,那么它们依然在同一时钟域,指示我们仔细分析它们之间的时钟偏斜.如果一个触发器使用的时钟直接来自时钟树A,而另一个触发器使用的是A经过了组合逻辑的时钟,那么它们不在同一时钟域;如果一定要把它们放在同一时钟域考虑,那么必须仔细分析时钟偏斜[3].对于传统的自动测试化系统而言,多时脉测试是项严格挑战,传统系统每次只能测试一种时脉.

整机单位需求一款ASIC电路,此电路一部分输入输出管脚工作在频率A=80 MHz,另一部分输入输出管脚工作在B=90 MHz.对于一般性系统而言,如果频率A是频率B的偶数倍即A=NXB(N=2,4…),则无需进行不同时钟偏斜的分析.为降低系统设计难度,只需依照系统最高的工作频率进行码行的仿真采样即可,无需特别处理.若频率A=NXB(N=3,5,7…)或者频率A不对B产生倍数关系,若想完全分析清楚时钟边沿的偏斜,则需要仿真时对频率A和频率B进行最小公倍数再两倍倍频,以期待完全能够将时钟边沿的偏斜全部覆盖,即测试码将工作在720 MHz,这样一个高频率无疑极大地增加了测试板的设计难度和对测试系统的要求,高速PCB和测试channel board价格极其昂贵.

2 多时域电路软硬件基于FLEX的实现

2.1测试系统FLEX介绍

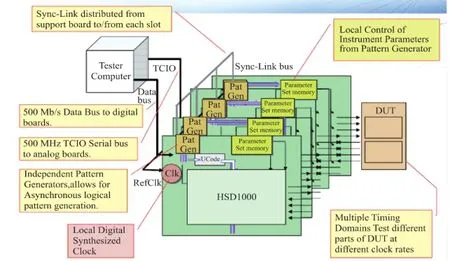

对于绝大多数测试系统而言,一次测试一种时脉是由测试系统本身的结构决定的.测试系统产生一个主时钟信号,各板卡全部工作在此相同的工作频率下.对以泰瑞达公司生产的UltraFlex采用了不同系统结构设计,即不同的数字信号板采用了独立的波形发生器,每块HSD1000具有独立的PatGen,可以产生不同的Refclk(如图1),这样的结构无疑会提高测试系统的成本,但是相对于提高测试系统的频率来讲,这些成本的提高无疑又具有了极高的性价比,这样的系统结构设计提供了多时钟信号测试的可能性.

图1 Ultraflex HSD1000架构

2.2硬件设计

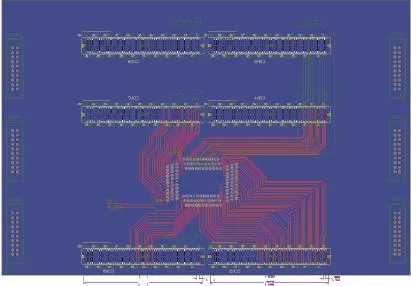

一般测试连接板设计时,如果pin脚资源足够,只需要将所需测试的DUT管脚连接到测试系统相应的系统资源上,但是对于此多频率的DUT测试板,需要在功能设计时已经确定工作在不同频率的DUT管脚分别连接到测试系统内不同的UltraPin800或者HSD1000上面,工作在不同频率的管脚彼此物理上完全归属于不同的Channel borad子集,依据定制ASIC的特点,基于FLEX mother board的结构,关键设计要点是将同样工作频率的pin子集分别连接到属于不同块的UltraPin800或者HSD1000上,后续能够配合软件代码实现时域的编程,最终设计PCB布局(如图2).

2.3软件编程

测试分析需要利用仿真向量和测试系统软件联合对DUT的功能进行比对式验证.仿真时需要在进行了功能的仿真之后,再对工作在不同频率的测试管脚进行自身相应的工作频率采样.因此最终所产生的测试向量图形的长度是不一致的,但是要求二者采样的绝对时间一致.

定义多时钟PinMap Sheet需要在全部PinMap定义完成之后,将对应的不同时钟域的管脚信号分别定义到不同组里面去,且利用不同的关键字名称.

不同的时钟域管脚编写相对应的Time Sets和Edge Sets sheet,如果在同一个Time Sets里面进行了不同时钟域管脚的TSB设置,IG-XL会产生一个错误.如果不同时钟域的管脚是同步的,则软件不需要进行额外的编程;如果不同时钟域的管脚是异步的,则必须规定主时钟time set强制使用同样的MOSC周期.且如果利用了UltraPin4000用于多时钟域的测试,则必须规定UltraPin4000为主时钟域,因为UltraPin4000有更高的限制.

对于不同时钟域的管脚需要对应各自不同的测试向量图形或者图形组,这同时也对应着设计仿真时的要求,在编译多时钟向量图形时,将原来PinMap sheet设置的关键字嵌入到Compiler Options中的Value中(如图3).

图2 PCB布局图

图3 向量编译

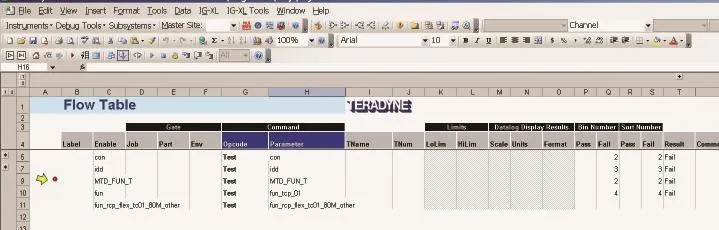

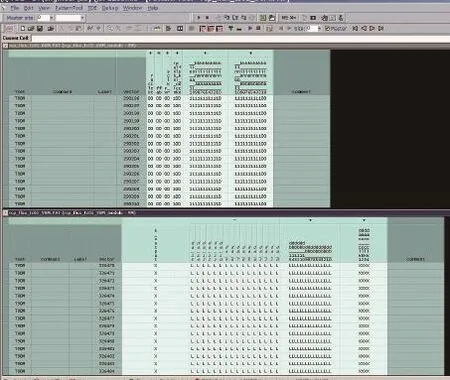

在相应基础框架搭建好之后,需要对已经编译好的向量进行调用,首先编写Test Instance,将不同时钟域的向量图形拉取到同一个Function Test中,除了利用Test template将不同的Patset_UP800拉取同一路径之后用"+"连接,还可以用VBT代码利用TheHdw. Patterns("pat1.PAT+pat2.PAT").Load和TheHdw.Patterns ("pat1.PAT+pat2.PAT").Test将不同的测试图形一起执行.在测试向量运行过程中,进行CPU Flag的握手且必须利用VBT中的TheHdw.Digital.TimeDomains. Patgen.SetFlagMatch属性对不同时钟域的flag进行使能.最终在FLOW table(如图4)中使用debug tool刷新出来的pattern格式较一般程序有较大不同,不同时域的两组pattern同时显示且可同时进行编辑(如图5).

不同时钟域的向量图形对应不同的向量图形组,因此数据排布和内容与一般电路不同.可选的方式有3种:tlResultModeOne,tlResultModeDomain和tlResult ModeModule.同时可以利用TheHdw.Digital.Time Domains.Patgen.PatternBurstPassed于显示结果的输出,数据最终如下:

Number SiteTest NamePattern1st Failed CycleTotal Failed Cycles

00MTD_PatSet_Onehsd_mtd+up4k_mtd N/AN/A

10MTD_PatSet_Domain hsd_mtdN/AN/A

20MTD_PatSet_Domainup4k_mtdN/AN/A

图4 FLOW talbe

图5 多时域pattern tools

3 结果与讨论

文章介绍并且应用了一种利用UltraFlex实现多时钟域电路测试的方法,此方法不需要对多时钟域电路增加可测性设计,降低了设计人员的工作量,也降低了多时钟域产品的设计和测试周期,具有较好的经济性和实用性.

[1]Josef Schmid,Joschim Knablein.Advanced synchronous scan test methodology for multi clock domain ASICs[C].In∶Proceedings of the 17th IEEE VLSI Test Symposium,San Diego,1999,105-113.

[2]周锦锋,陈志冲,倪光南.针对多时钟扫描测试的可测性设计方法[J].北京:计算机辅助设计与图形学学报,2003.

[3]王巍.多时钟域ASIC的可测性设计[M].北京:EDA专栏,2003.

Test Method for UltraFlex-based Multiple Clock Domain Circuit

YAN Huaxin

(China Electronics Technology Group Corporation No.58 Research Institute,Wuxi 214035,China)

The article introduces a test method for multiple clock domain circuit in UltraFlex system.The method refers to UltraFlex hardware design and VBT to solve the problem that the lowest common multiple exceeds test system capacity when the multiple clock domain frequency is high.The method is universally applicable for multiple clock domain ASICs. It reduces the workload of design and test algorithm design and accelerates the design and test process.

multiple time domain;test method;UltraFlex

TN307

A

1681-1070(2016)06-0024-04

2016-1-18

严华鑫(1987-),男,江苏盐城人,毕业于南京理工大学光电信息工程专业,目前就职于中国电子科技集团公司第58研究所,从事半导体电路测试与应用工作.