MIMO-OFDM系统时间同步算法的研究与实现

聂 伟,晋 红,严 寒

(北京化工大学 计算机系统与通信实验中心,北京 100029)

MIMO-OFDM系统时间同步算法的研究与实现

聂伟,晋红,严寒

(北京化工大学 计算机系统与通信实验中心,北京 100029)

在FPGA平台上实现了一种MIMO-OFDM系统的时间同步器。该同步器基于CAZAC序列的相关特性,采用了对接收信号进行量化处理,将复杂的复数相关运算变化成简单的映射,从而降低了运算复杂度和硬件开销。实验结果验证了同步器在实际的硬件环境中的可用性,并且能够在降低运算复杂度和减少硬件开销的情况下,实现较好的同步。

时间同步器;MIMO-OFDM;量化;FPGA

0 引 言

多输入多输出(MIMO)技术和正交频分复用(OFDM)技术的结合是第四代移动通信的热点研究课题。它不仅增加了系统容量,而且提高了频谱利用率[1-3]。在MIMO-OFDM系统中,时间同步的准确率问题一直是研究的重点内容,它直接影响着MIMO-OFDM系统性能的好坏。

文献[4]分析了MODY算法和Schenk &Zelst算法这两种经典的同步算法,以上提到的同步算法都遵循着“分组检测-频偏补偿-符号同步”的一般过程,时间同步分成了两步,而且中间间隔着频偏补偿的过程,使得最终的时间同步结果易受到频偏补偿结果的影响。文献[5]提出了一种WPS算法,利用自相关性良好的CAZAC序列,提高了时间同步的精度,但是没有考虑到频偏对定时位置的影响。文献[6]提出的同步算法基于 CAZAC序列良好的互相关和自相关特性,通过相关运算能准确的找到定时点,但是仍然受到频偏影响,需要进一步修正定时估计结果。文献[7]针对CAZAC序列的良好特性和WPS算法的不足,对前导序列结构和定时同步算法进行了改进,虽然增加了训练序列的长度,但是同时也使得定时位置不受频偏影响,并且能估计出整数倍频偏,但仅仅进行了算法仿真,并没有真正实现。

本文针对文献[7]中所提出改进后的时间同步算法进行了FPGA实现。在实现过程中,针对所使用的时间同步算法运算复杂,硬件不易实现的问题,采用对接收信号进行量化的方法,将复数乘法运算简化成映射操作,大大减少了硬件实现上需要的乘法器,实验结果验证了同步器在实际的硬件环境中的可用性,并且表明“量化法”能够在不影响同步性能的前提下降低运算复杂度和减少硬件开销。

1 MIMO-OFDM系统模型

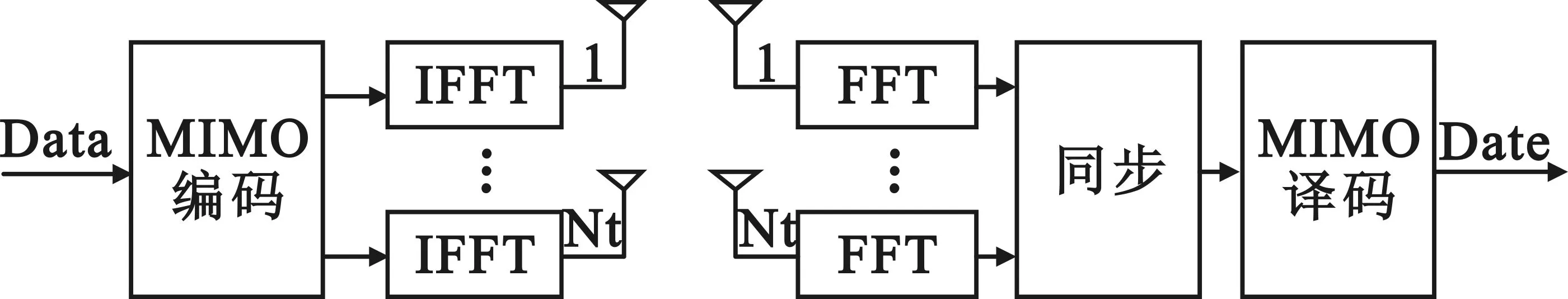

图1为一个Nt发Nr收的MIMO-OFDM系统框图[8]。

图1 MIMO-OFDM系统框

(1)

式(1)表示各发射天线发送的OFDM符号。其中,i表示发射天线序号,最大为Nt;N表示IFFT变换的点数,也即系统所用子载波个数;Ti(k)为第i个发射天线、第k个子载波上的调制数据;Ng为循环前缀的长度,为了消除OFDM符号间干扰。

经过AWGN信道之后,接收天线接收到的信号可表示为:

(2)

式中,j表示接收天线序号,最大为Nr;τi,j和εi,j分别表示第i条发射天线到第j条接收天线的时间延迟和频率偏移,εi,j包括整数部分和小数部分,在同步过程中需要分别估计;ωj(n)表示第j根天线上接收到的AWGN总和。

2 基于CAZAC序列的时间同步方案

2.1采用的前导序列结构

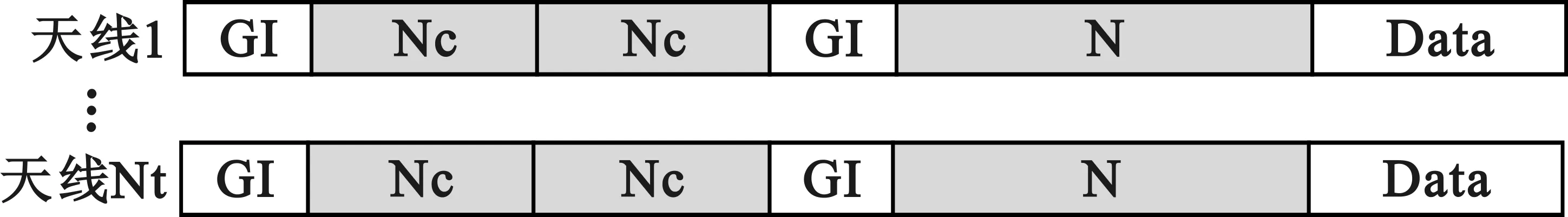

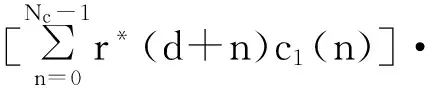

针对文献[5]中WPS算法的定时准确性受频偏的影响,文献[7]改进的同步序列结构如图2所示。

图2 本文采用的同步序列结构

该序列占用两个OFDM符号长度,由周期分别为Nc和N的CAZAC序列组成,N=2Nc。各天线上的序列由CAZAC序列循环移位得到。若第1根发射天线上的序列为c(n),则第i根发射天线上的序列可以表示为c(n-(i-1)·D),D表示循环移位数。

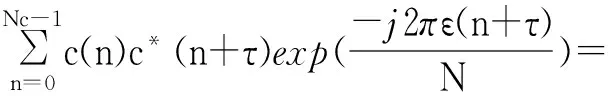

当存在频偏ε时,将接收端接收到的信号同本地序列c(n)进行互相关如下:

(3)

2.2时间同步方案

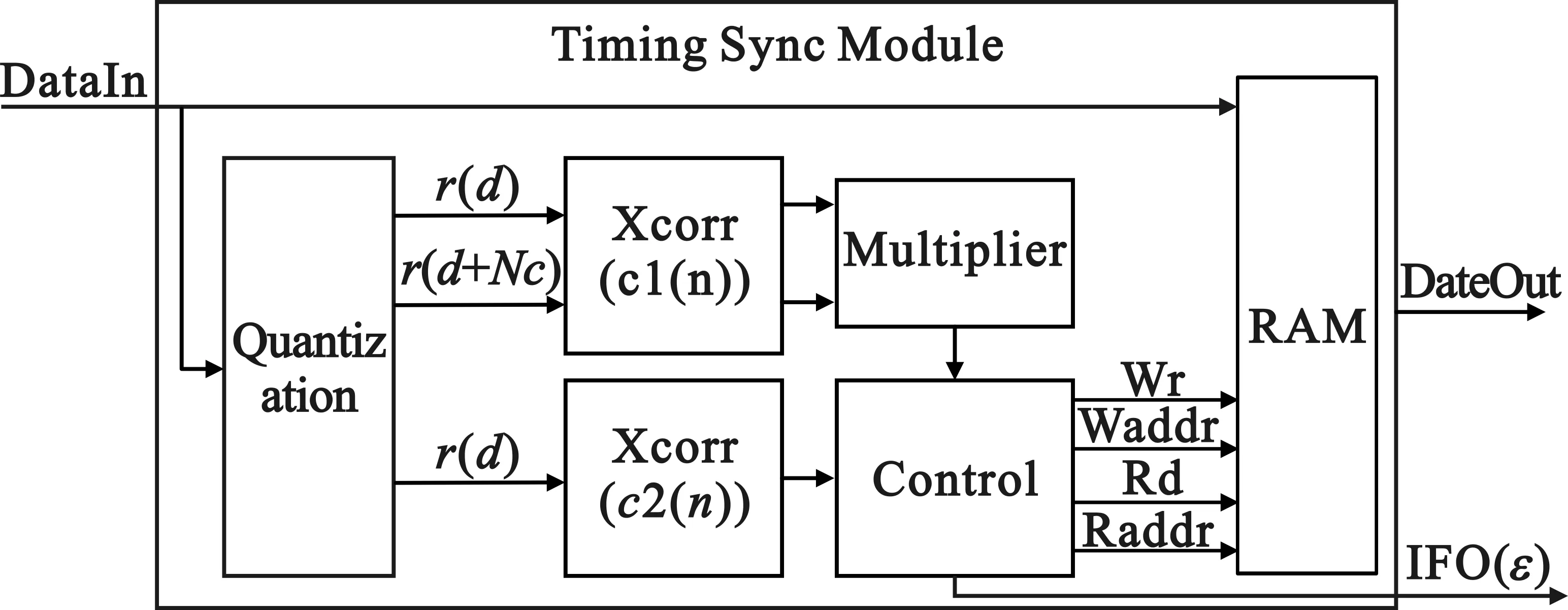

本文提出的方法利用接收信号同本地序列进行互相关来进行定时同步[9-10]。假设本地序列分别为长度为Nc的c1(n)和长度为N的c2(n),则判决函数可表示为:

(4)

(5)

在P1(d)和P2(d)分别取得最大值处即为训练序列c1(n)和c2(n)的起始位置处。

图3 理想定时点与峰值点的位置关系

(6)

(7)

本文采用的时间同步算法虽然增加了训练序列的长度,占用了一定的信道资源,但是能够直接地得出准确的定时点,使定时不受频偏影响,并且在定时的同时能够估计出整数倍频偏,缩短了同步过程,从而降低了系统同步的复杂度。

3 时间同步算法的FPGA实现方案

3.1接收信号量化处理

由前文可知,本文采用的时间同步算法不仅性能优良,而且结构简单、易于实现。但是由式(4)和式(5)可知,将接收信号同本地训练序列进行互相关,仍然需要大量的乘法运算。为了进一步降低同步方案的复杂度和减少硬件资源开销,本文在FPGA实现过程中,对接收信号进行量化处理:正值为1,负值为-1。这样接收到的信号变成统一的(1+j)的结构形式,复数乘法运算则化简如下:

[rr(n)+j·ri(n)]·[cr(n)+j·ci(n)]=

(1+j)·[cr(n)+j·ci(n)]=

[cr(n)-ci(n)]+j·[cr(n)+ci(n)]

(8)

可以看出,经过量化后无需使用乘法器,只需要两个加法器就能实现原本的乘法运算,节约了资源。而且,接收信号经过量化后与本地序列的相关值虽有所变化,但峰值依然尖锐,如图4所示。

图4 量化前后CAZAC序列相关值比较

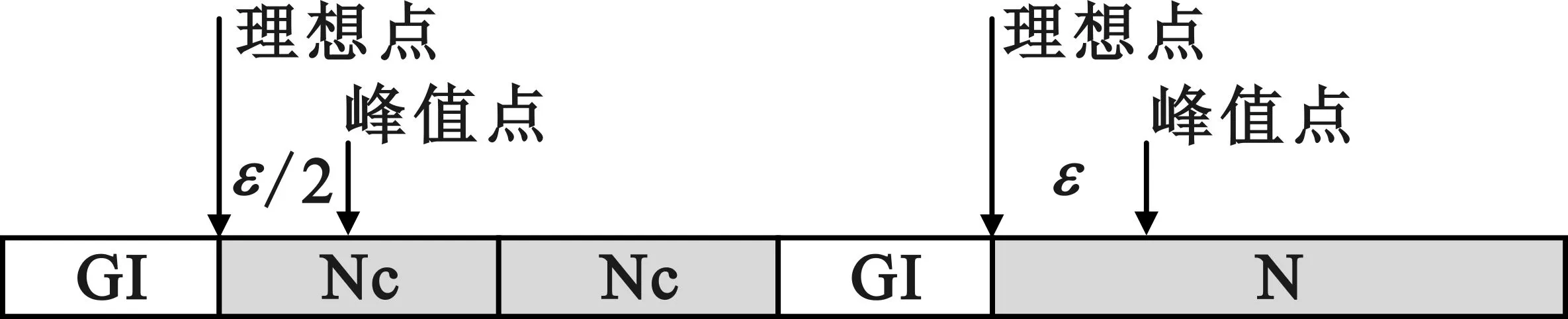

同步性能仿真结果如图5所示。

图5 量化处理前后同步性能比较

由图中可知,采用对接收信号进行量化的方法在低信噪比时会对定时性能稍有影响。而当SNR=0,对接收信号进行量化后在多径信道下就能达到85%的准确率;当在SNR=2以上时,不论在AWGN信道还是多径信道都能达到几乎100%的定时准确率,量化对于同步性能的影响可以忽略不计。

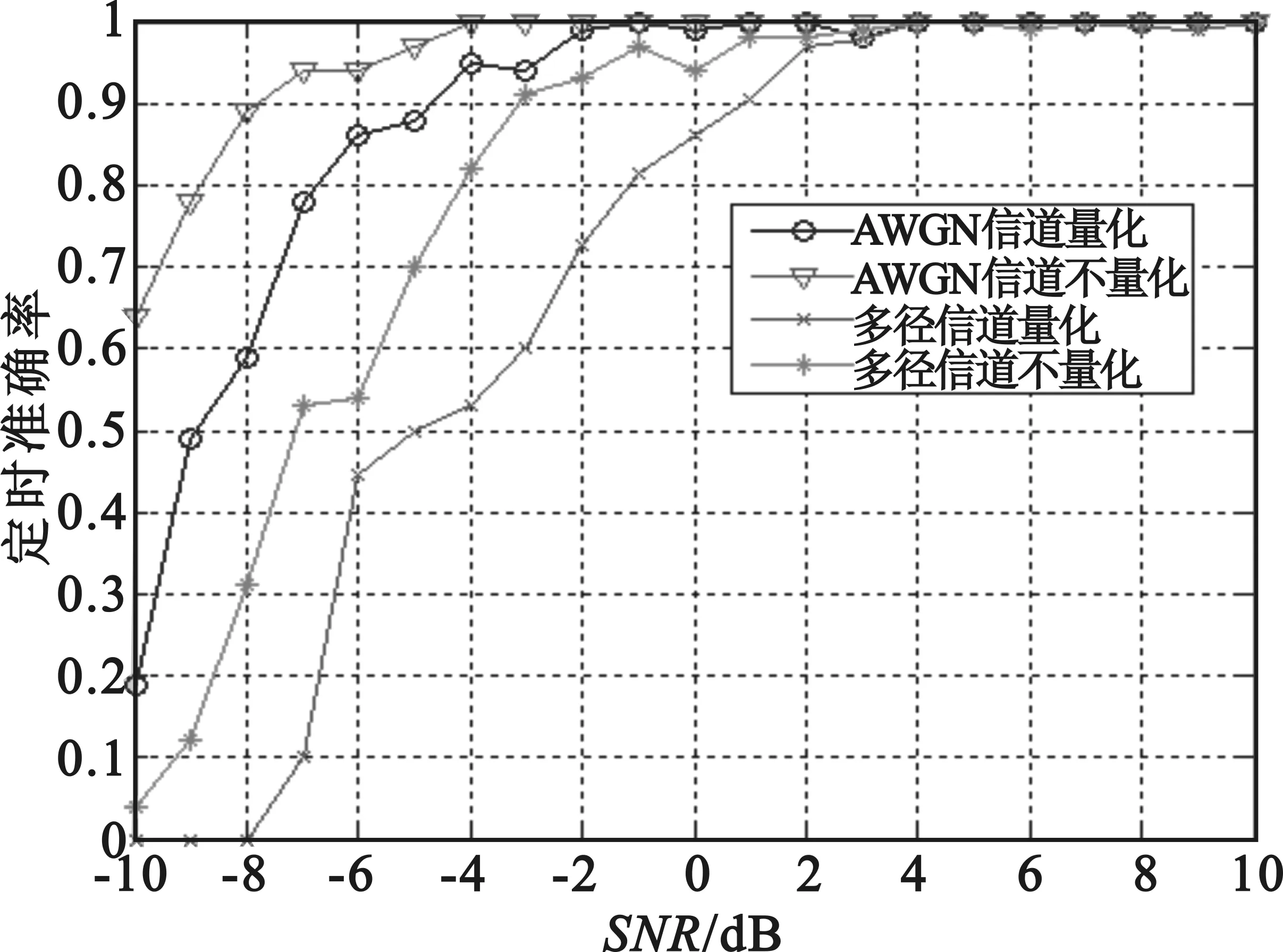

3.2FPGA实现方案

本设计的时间同步算法参数如下:天线数目2发2收;系统带宽20 MHz;OFDM符号长度64;循环前缀长度16;CAZAC序列1周期:32;循环移位:8;CAZAC序列2:周期:64;循环移位:16。图6为时间同步算法实现结构图。

图6 时间同步算法实现结构

由图6可看到,天线接收到的数据被分成两路,一路直接进入RAM存储器等待同步输出;另一路进行量化和延迟操作,使得r(d)和r(d+Nc)能同时进入到互相关模块(Xcorr)。计算出的相关值被送入控制模块(Control),在控制模块内进行判决和修正处理,并根据得到的定时点的位置产生RAM的读控制信号,将从接收信号中检测出的有效数据输出。此外,在设计中还将估计出的整数倍频偏引出(IFO),以供后续频偏补偿模块使用。

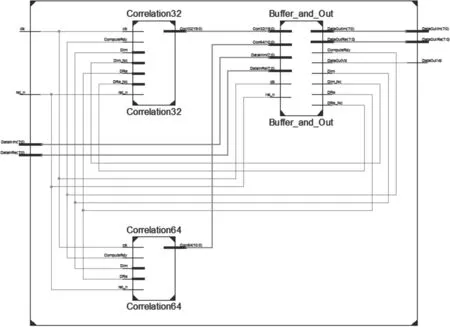

图7所示为在ISE Design Suite 14.3中进行综合生成的顶层模块连接图。图中只有三大模块,是因为量化和RAM都是在Buffer_and_Out(Control)模块内部完成的,合并成了一个模块。

图7 时间同步算法实现的顶层模块连接

4 实验结果与分析

在以上分析讨论的基础上,利用ModelSim软件对时间同步算法模块进行了仿真,并基于Xilinx公司的Virtex-6 LXT FPGA ML605开发平台,对MIMO-OFDM基带系统进行了上板验证。

将经过模拟AWGN信道的数据重复送入算法模块,接收天线上的本地序列分别与发射端的序列对应。仿真结果以其中一根天线为例,发射的每帧有效数据包含训练序列和10个OFDM帧长度的数据,以突发分组方式重复发送。

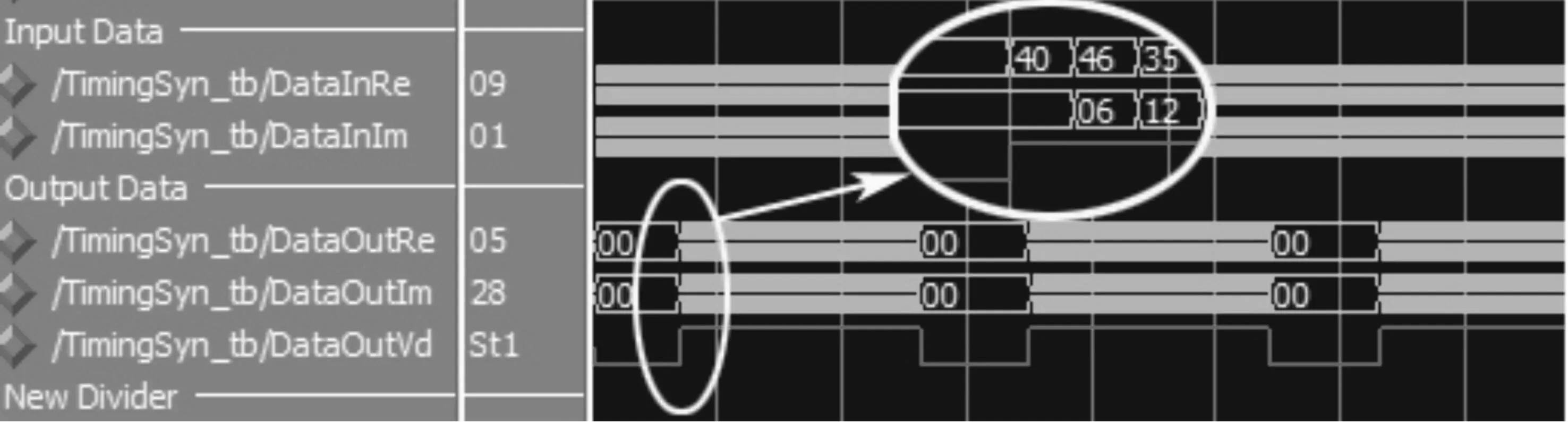

从图8中可看出,该设计能够确定接收信号中的有效数据部分,圆圈放大部分显示定时点正好在CAZAC序列的起始位置,表明该模块具有良好的定时效果。

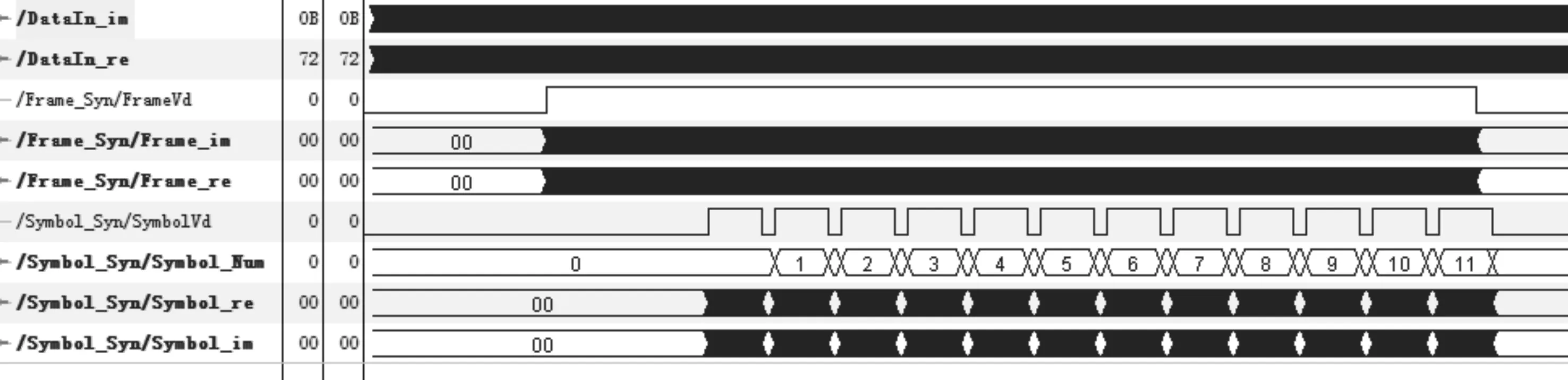

图8 同步模块的Modelsim仿真

仿真结果验证了时间同步方案的正确性,在此基础上对MIMO-OFDM基带系统时间同步方案进行上板验证。运用片上逻辑分析仪ChipScope对基带系统运行过程中的信号进行采样、观察和分析。联立同步的各个模块,并将经过信道处理的基带信号送入接收机,得到的接收天线1上的时间同步的测试结果如图9所示:FrameVd为帧有效信号,表示数据帧区间;SymbolVd为符号有效信号,表示OFDM符号区间。测试图表明,接收天线通过时间同步,找到了有效的数据帧,并且将每个FFT区间区分开来,便于后续的OFDM解调处理,可以看出,本模块在有效数据帧内,找到了正确的OFDM符号区间。

图9 时间同步的ChipScope测试结果

通过ModelSim以及Xilinx公司的在线逻辑分析工具ChipScope,验证了实现的时间同步模块的正确性。

5 结语

基于本文作者在文献[7]中提出的一种改进的MIMO-OFDM系统时间同步算法,本文在FPGA平台上实现了基于CAZAC序列的MIMO-OFDM系统的时间同步器。该同步器采用了对接收信号进行量化处理的方式,解决了运算复杂度高的问题。实验结果验证了同步器在实际的硬件环境中的可用性,并且能够在降低运算复杂度和减少硬件开销的情况下,实现较好的同步。该时间同步器可以广泛应用于MIMO-OFDM基带实验系统的同步模块中。

[1]JIA K J, DU T H, ZHANG X W, et al. Frequency Offset Estimation and Symbol Timing of MIMO-OFDM System based on Modified Auto-Correlation Matrix in Industry Environment[J]. Energy Procedia, 2012, 16(Part B):1187-1192.

[2]Hsu T Y and CHENG S Y. Low-Complexity Sequential Searcher for Robust Symbol Synchronization in OFDM Systems[J]. Very Large Scale Integration Systems IEEE Transactions on, 2012, 20(5):959-963.

[3]TANG T and Heath R W. A Space-Time Receiver with Joint Synchronization and Interference Cancellation in Asynchronous MIMO-OFDM Systems[J]. IEEE Transactions on Vehicular Technology,2008,57(5):2991-3005.

[4]邵峰.MIMO OFDM同步技术研究[J].电子科技,2012(03):85-89.

SHAO Feng. Research on MIMO OFDM Synchronization Technology [J]. Electronic Science and Technology, 2012(03):85-89.

[5]FENG C, ZHANG J, ZHANG Y, et al. A Novel Timing Synchronization Method for MIMO OFDM Systems[C]// Vehicular Technology Conference, 2008. VTC Spring 2008. IEEE. IEEE, 2008:913-917.

[6]刘晶,熊春林,魏急波.多径衰落信道下的OFDM时频联合同步算法[J]. 通信技术,2015,48(04):386-391.

LIU J, XIONG C L, WEI J B. Timing-and-Frequency Synchronization Algorithm for OFDM Systems in Multipath Fading Channels [J]. Communications Technology, 2015, 48 (04): 386-391.

[7]聂伟,严寒. 一种改进的MIMO-OFDM系统时间同步方法[J]. 电子技术应用, 2015, 41(05):112-115.

NIE Wei and YAN Han. An Improved Timing Synchronization Method for MIMO-OFDM Systems [J]. Application of Electronic Technique, 2015, 41(05):112-115.

[8]杨冰, 王勇, 袁哲明等. MIMO-OFDM系统定时同步算法的FPGA设计[J]. 北京邮电大学学报, 2006(04):99-102.

YANG B, WANG Y, YUAN Z M , et al. FPGA Design of Timing Synchronization in MIMO-OFDM System [J]. Journal of Beijing University of Posts and Telecommunications, 2006(04):99-102.

[9]Kung T L. Robust Joint Fine Timing Synchronization and Channel Estimation for MIMO Systems[J]. Physical Communication,2014,13:168-177.

[10]WANG J, YANG X,LI Dao-ben. Synchronization of MIMO OFDM Systems by Perfecting Complete Generalized Complementary Orthogonal Loosely Synchronous Code Groups[J]. Journal of China Universities of Posts & Telecommunications,2009,16(8):1-7.

聂伟(1960—),男,博士,副教授,主要研究方向为软件无线电、通信信号处理等;

晋红(1989—),女,硕士研究生,主要研究方向为软件无线电、通信信号处理等;

严寒(1991—),男,硕士研究生,主要研究方向为软件无线电、通信信号处理等。

Time Synchronization Algorithm for MIMO-OFDM System

NIE Wei,JIN Hong,YAN Han

(Computer System and Communication Laboratory,Beijing University of Chemical Technology,Beijing 100029,China)

A time synchronizer of MIMO-OFDM system is implemented on the FPGA platform. This synchronizer, based on the relevant characteristics of CAZAC sequences, conducts quantization of the received signal, and turns the complicated complex correlation operation into a kind of simple mapping, thus reducing the computational complexity and hardware cost. Experimental results indicate the availability of this synchronizer in the actual hardware environment, and that this synchronizer could achieve better synchronization at a reduced computational complexity and decreased hardware expenditure.

time synchronizer; MIMO-OFDM; quantization; FPGA

10.3969/j.issn.1002-0802.2016.03.023

2015-10-06;

2016-01-20Received date:2015-10-06;Revised date:2016-01-20

TN929.53

A

1002-0802(2016)03-0374-04