FPGA的弱小信号处理关键技术研究

国 磊, 尚 勇, 白 森

(1.中国空空导弹研究院, 河南 洛阳 471009; 2.民航飞行学院洛阳分院, 河南 洛阳 471009)

FPGA的弱小信号处理关键技术研究

国磊1, 尚勇2, 白森1

(1.中国空空导弹研究院, 河南 洛阳471009; 2.民航飞行学院洛阳分院, 河南 洛阳471009)

算法的计算精度要求和算法实现所需的FPGA资源是FPGA选型的关键因素。本文从工程应用角度出发,详细地论述了基于FPGA的弱小信号处理关键技术研究及实现,结合噪声成形算法给出FPGA实现信号处理时滤波器输出截断位数确定原则,依此原则既确保计算精度又可节省FPGA硬件消耗。最后分析影响弱小信号检测的直流问题,阐述其产生的原因并给出有效的直流抑制方法。

信号处理;弱小目标检测;FPGA;噪声成形;直流抑制;滤波器截断

0 引 言

随着信号处理技术的发展, 数字信号处理越来越多的应用于信号处理的各个领域, 其中FPGA占有广阔的市场。 由于FPGA器件自身的特点, 其运算大多采用有限位数定点运算形式实现, 如何既保证运算精度又有效地利用FPGA资源, 从而避免FPGA资源的浪费甚至无法实现成为数字信号处理必须面对的问题。 本文基于此, 对FPGA的弱小信号处理关键技术开展了研究。

1 数学模型

数字接收系统一般由A/D和FPGA组成, A/D将模拟信号转换成数字信号, FPGA接收数字信号完成后续信号处理操作, 高精度A/D(以2 208为例)量化位数为16 bit, 有效位数约11 bit, 本文以此为依据建立的仿真模型可表示为

R(t)=S(t)+N(t)+D

式中:S(t)为信号;N(t)为噪声;D为直流分量。

模型中噪声采用均值为零的高斯白噪声, 根据A/D有效位数可推算出量化后信噪比为66 dB, 设信号满量程输入为10 dBm, 噪声功率约为-56 dBm。 直流分量根据各系统实际测量所得数值确定即可, 本文直流分量定为40。 由于A/D量化位数为16 bit, 在FPGA中数据处理格式为有符号补码, 有效量程为-32 768~32 767, 因此S(t)取在此量化区间的连续波单频信号即可满足算法验证需求。 为证明算法的有效性和通用性, 本文信号动态范围取+10~-105 dBm, 即包含满量程和淹没在噪声背景下两种极限情况。

2 信号处理设计及实现

2.1信号处理流程

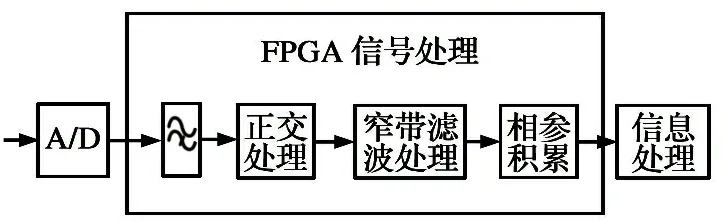

信号处理一般流程如图1所示, FPGA接收A/D转换后的数字信号后, 完成正交变换、 窄带滤波处理、 相参积累等一系列算法, 将时域信号转换成频域信息, 转由信息处理单元完成后续工作。

图1信号处理基本流程

传统正交变换主要通过输入信号与固定频率的正余弦信号进行混频, 后经过低通滤波得到IQ两路信号, 当采样率满足fs=4f0/(2k+1)时, 正余弦信号可简化成0, 1, -1交替出现序列, FPGA实现正交处理时可将正交系数与后续低通滤波器系数组合形成新的滤波器系数, 转由FIR滤波器实现正交处理。 式中,f0为信号载频;fs为采样率。

窄带滤波处理主要完成降采样率操作。 当前A/D量化一般在中频进行, 采样率较高, 给后续处理带来巨大压力, 增加了FPGA程序设计难度, 同时不利于信噪比的改善。 为了改善信噪比, 同时降低程序开发难度, 降采样处理是必要的。 通过仿真可以看出要得到系统需求的数据率, 单滤波器实现滤波, 滤波器阶数过大, FPGA无法实现。 这里采用窄带滤波器组分级处理实现降采样。

相参积累可根据FPGA资源情况选择在FPGA或DSP中实现, 本文选择在FPGA中实现。

2.2滤波器输出截断分析

FPGA内部运算基于定点二进制有符号补码, 滤波器输出有全精度输出和截断输出两种形式。 全精度输出数据没有损失, 但运算量较大, 占FPGA硬件资源较多, 滤波器组级联设计在不做截断处理的情况下无法实现, 必须考虑滤波器舍位处理, 滤波器舍位应顾全满量程信号和淹没在噪声中信号两种极端情况。

2.2.1满量程信号高位处理

满量程信号输入时, 滤波器输出高位取舍需考虑溢出问题, 一般保留原则为高位只有一位符号位, 其他为数据有效位即可, 这样既保证数据位数有效利用, 又避免发生溢出。 工程实现中ISE10.1以下版本滤波器输出一般保留3~4位符号位, 程序设计时需要仿真定位, 而ISE10.1以上版本由于滤波器核采用新型结构实现, 滤波器输出一般保留2位符号位, 从次高位开始保留即可。

2.2.2淹没在噪声中的信号低位处理

信号淹没在噪声中时, 为了得到有效信号信息, 噪声必须占据3~4位数据位数, 即噪声成形算法。 A/D量化后引入的噪声分量可用chipscope实际测量获得, 也可根据A/D有效位数算出。 如前设A/D有效位数约为11 bit, 以16 bit A/D计算, 噪声约占5 bit。 经过滤波降采样处理后, 噪声能量降低, 噪声幅度变小, 噪声占据位数后移。 根据噪声成形原理, 为保留信号信息, 噪声占有位数需维持在3~4 bit, 在滤波器系数增益为1的情况下, 需合理考虑滤波器输入输出之间的位数展宽, 以保证噪声成形的应用条件。

依据上述分析完成每级滤波器输出位数的确定, 既可节省FPGA资源, 又保留了全部的信号信息, 完成了信号处理算法实现。

2.3直流产生及抑制

FPGA实现数字信号处理中不可避免会存在直流分量, 这会直接影响对弱小信号的检测, 在系统进行信息处理之前, FPGA必须采取有效的措施对直流进行抑制。

FPGA内直流主要来源于A/D量化、 失配引入的直流和定点非全精度运算引入的直流。 前者可通过改善A/D输入匹配电阻、 提高A/D量化精度等措施减小。 在A/D型号电路确定后, 外界引入直流分量已定, FPGA内部可加入高通滤波进一步削减外界直流分量。 后者由于受FPGA硬件资源限制, 无法做到全精度运算, 只能采取四舍五入措施减小。 一般情况下, A/D量化引入的直流经过正交处理后不会对后续信号处理带来影响, 但工程实现中可能会对A/D采样信号进行调制, 从而造成直流延拓。 A/D量化输入直接进行高通滤波处理是目前广泛采用的手段, Xilinx公司FPGA软件开发工具ISE提供的滤波器软核最低阶数为8, 本文从工程应用角度出发, 考虑FPGA硬件资源有效利用, 提出一种更加简单有效的直流抑制算法, 具体如下:

简单高通滤波(仅使用简单的寄存、 移位操作即可, 不使用FIR滤波器), 滤波器系数bp = [0, -0.25, 0, 0.5, 0, -0.25, 0], 缓存5个时钟同期, 分别记作dat_delay1, dat_delay2, dat_delay3, dat_delay4, dat_delay5。 然后定义16位数据data_new, 作如下运算: Data_new=dat_delay3*2- dat_delay1- dat_delay5

ISE10.1以上版本滤波器软核自带对称式四舍五入处理选项, 当滤波器输入不大于18 bit时可直接利用滤波器核完成四舍五入, 但工程实际应用中, 经反复验证发现, 当滤波器输出舍位较多时, 软核自带对称式四舍五入功能存在缺陷, 并未达到抑制直流的效果甚至引入新的直流分量。 本文根据FPGA内部数据运算基于二进制有符号补码实现的特点, 提出自定义四舍五入算法, 解决FPGA内的直流问题, 算法公式如下:

Dout=floor([Din+1]/2)

FPGA内部实现: Din为比经过滤波器输出截断处理数据位数多一位的滤波器输出; Dout为Din加1后舍去最低位的结果, 即四舍五入处理后的数据。 本算法在滤波器输出为最大正数时会溢出, 需加入判断逻辑, 防止溢出, 一般工程应用很少会发生溢出现象。

3 实验结果

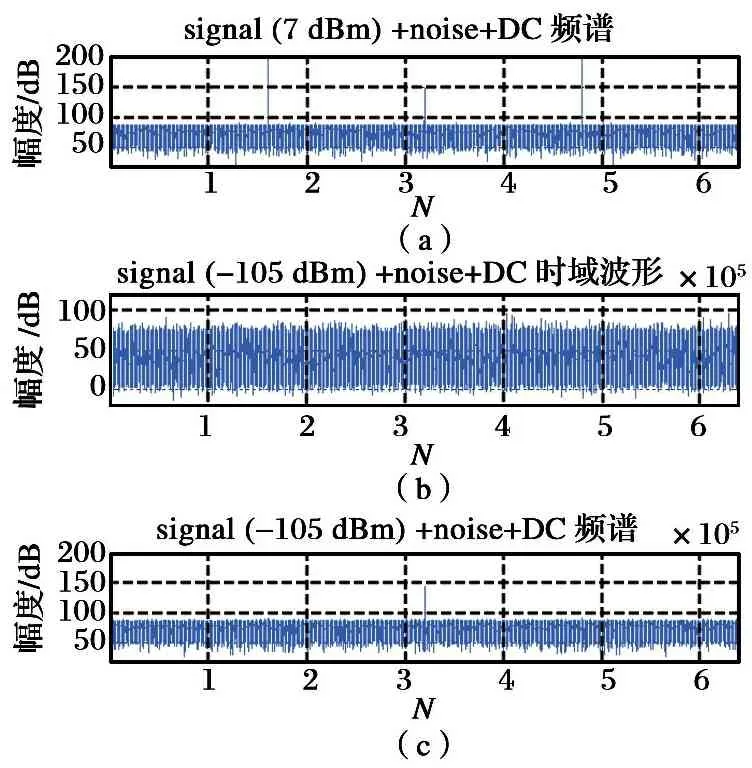

实验仿真数据通过安捷仑逻辑分析仪16822A采集获得, 中心频率60 MHz, 多普勒频率5 kHz, 为验证算法有效性, 信号输入幅度取典型值7 dBm和-105 dBm。 其中: 7 dBm为大信号, 用于确定程序中关于大信号情况下滤波器输出高位保留是否合理; -105 dBm为弱小信号。 采集数据的时/频域效果图如图2(a)所示, 横坐标为采样点数N, 纵坐标为信号量化后绝对幅度, 由于大信号状态信号呈现完美包络形式, 这里未给出, 只给出了大信号频域处理结果。 弱小信号时域波形如图2(b)所示, 从图中可以看出弱小信号已经淹没在噪声背景中, 并且其频域结果直流分量明显, 如不作任何处理则对后续目标检测处理会造成影响, 如图2(c)所示。

图2实采数据时/频域显示

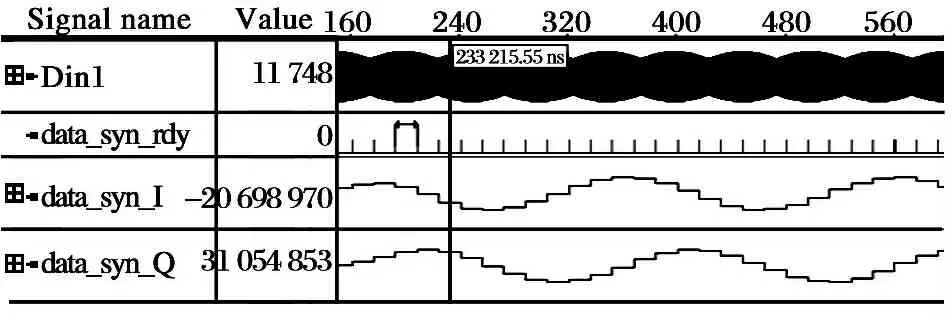

FPGA实现的功能仿真结果如图3所示, 证明算法在FPGA实现中的可行性。 图中给出了大信号经A/D量化后的中频时域波形、 经过信号处理后的低频输出结果及数据有效标志。 可以看出中频时域波形呈现为包络状态, 目标速度信息隐含在包络里并调制在中频载波上, 经过信号处理后的低频数据为只包含目标多普勒信息的正弦波形。 仿真结果说明FPGA实现了对雷达目标回波的正交下变频和滤波处理, 完成了雷达目标回波的初步解析, 并未造成目标信息丢失, 而弱小信号情况下波形仿真结果不直观, 这里不给出。

图3FPGA仿真结果

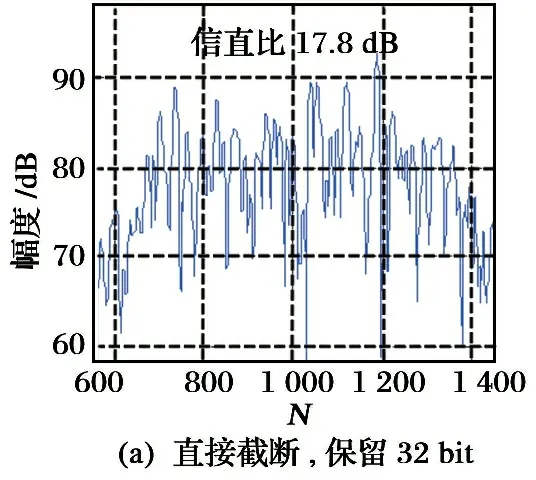

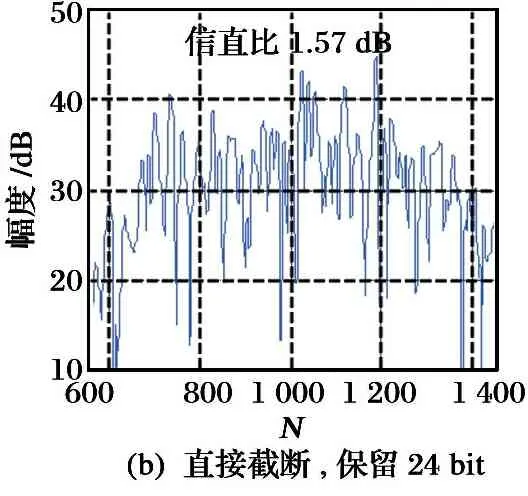

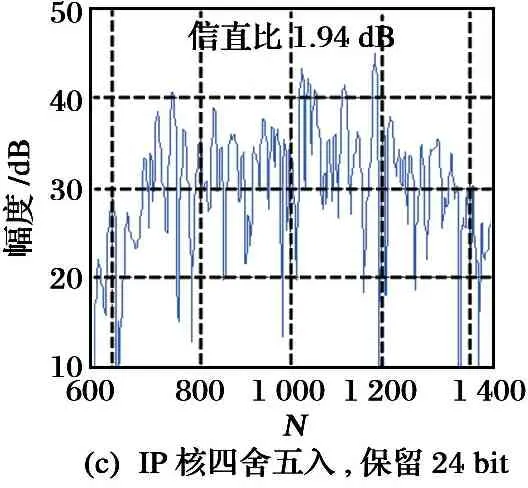

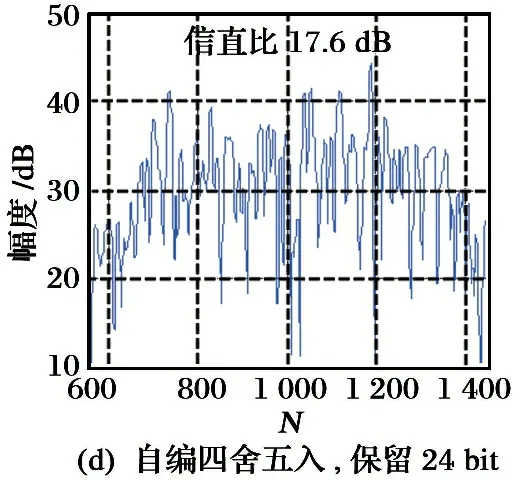

各种滤波输出舍位处理对直流影响分析见图4。 在不考虑FPGA硬件资源的情况下, 图4(a)为滤波器直接截断并保留32位输出, 其处理结果经过存储, 由Matlab进行分析信号直流比为17.8, 直流对信号检测不造成影响。 但由于保留位数过多, 不利于FPGA实现和资源优化; 图4(b)为直接截断并保留24位输出时, 节省了FPGA资源但信号直流比恶化, 信号直流比只有1.57, 严重影响后续信号检测, 此仿真同时说明直流影响与保留位数有关, 当数据保留位数较多时, 直流影响可以忽略。 图4(c)为直接利用Xilinx提供四舍五入选项得到的仿真结果, 信号直流比为1.94, 可见直接调用IP核对直流抑制并无显著改善; 图4(d)为采用本文设计的四舍五入算法并保留相同位数仿真结果, 信号直流比为17.6, 可见本算法既降低了FPGA硬件资源损耗, 又抑制了直流分量, 净化了弱小信号检测的噪声背景。

图4各种舍位处理结果对比

4 结 论

本文提出的算法既保证了系统性能, 又不对信号处理应用环境作过多的资源限制, 节省硬件资源降低工程造价, 间接提高了FPGA在信号处理领域的应用空间。 该算法只能在一定动态范围内改善系统性能, 目前可适应110 dB的系统动态, 对进一步增加动态范围方面能力略显不足。 如系统需求更大的动态范围信号处理能力而又不期望硬件提升所带来的工程设计成本的提高, 则需在自适应滤波技术方面进行考虑。

[1] 于丽霞, 王福明. 微弱信号检测技术综述[J]. 信息技术, 2007(2): 115-116.

[2] Gong Xuemei, Gaalaas E, Alexander M, et al. A 120 dB Multi-Bit SC Audio DAC with Second-Order Noise Shaping[C]∥IEEE International Solid-State Circuits Conference, 2000: 344-345.

[3] Yu S H, Hu J S. Analysis and Design of a Single-Bit Noise-Shaping Quantizer[C]∥American Control Conference, 2003: 1631-1636.

[4] Xilinx. Virtex-6 Family Overview[M].USA: Xilinx, 2012.

[5] 克劳切 R E.多抽样率数字信号处理[M]. 北京: 人民邮电出版社, 1988.

[6] 奥本海姆 A V, 谢弗 R W. 数字信号处理[M].西安: 西安交通大学出版, 2002.

[7] 万建伟, 王玲.信号处理仿真技术[M].长沙: 国防科技大学出版社, 2008.

[8] 徐明远, 邵玉斌.MATLAB 仿真在通信电子工程中的应用[M].西安: 西安电子科技大学出版社, 2010.

[9] Lyons R. Interpolated Narrowband Low Pass FIR Filters[J]. IEEE Signal Processing Magazine, 2003, 20(1): 50-57.

[10] MathWorks. Efficient Narrow Transition-Band FIR Filter Design[K]. MATLAB7.0 HELP, 1999-2000.

Study on Key Technologies for Weak Signal Processing Method of FPGA

Guo Lei1, Shang Yong2, Bai Sen1

(1.China Airborne Missile Academy, Luoyang 471009, China;2. Civil Aviation Flight University of Luoyang, Luoyang 471009, China)

The calculation precision of algorithm and the FPGA resources for the algorithm implementation are the key factors in the FPGA selection. From the perspective of engineering application, the research and implementation of weak signal processing technology based on FPGA is discussed in detail. Combined with the noise shaping algorithm, the paper gives the principle of determining the fliter output truncation number when the signal processing is realized by FPGA. This can ensure the accuracy of calculation and save the FPGA hardware consumption. Finally, the influence of direct-current(DC) in the weak signal detection is analyzed, the reason for DC generation is expounded and an effective method of DC inhibition is provided.

signal processing; weak target detecting; FPGA; noise shaping; DC suppression; filter truncation

10.19297/j.cnki.41-1228/tj.2016.03.010

2015-06-25

国磊(1982-), 男, 辽宁锦州人, 硕士, 高级工程师, 研究方向为信号处理及FPGA应用。

TN911.72

A

1673-5048(2016)03-0045-04