数字化手术室多路高清视频合成系统的研究

魏 涛,杨勇勇,邵 蕾.上海市中医医院医学装备管理处,上海 0007 .上海医疗器械股份有限公司工程部,上海 0009 .同济大学附属上海同济医院科研处,上海 00065

·医疗器械园地·

数字化手术室多路高清视频合成系统的研究

魏 涛1,杨勇勇2,邵 蕾3

1.上海市中医医院医学装备管理处,上海 200071 2.上海医疗器械股份有限公司工程部,上海 200093 3.同济大学附属上海同济医院科研处,上海 200065

目的数字化手术室多路高清视频合成对于提高手术教学及手术远程会诊具有重要的意义。方法针对国内现有手术室视频清晰度低、可视角度少、切换繁琐等问题,采用现场可编程门阵列(field-progtammable gatearray,FPGA)硬件架构,设计了四路HD-SDI高清视频信号的合成,现场测试。结果系统运行稳定,操作方便。结论设计和实现手术室内多路高清视频合成系统,是数字化手术室建设的重点和难点。

数字化手术室;高清视频合成;现场可编程门阵列

随着信息技术及现代医学的快速发展,医院数字信息化程度越来越高,在现代微创医疗中,医师需借助视频显示进行手术,这使高清视频在数字化手术室内显得十分重要。此外,数字化手术室不仅具有对患者进行手术治疗的功能,还应满足手术教学观摩、学术交流及远程医疗等诸多新型应用的需求,这就对数字化手术室内的视频图像质量和多路视频信号的处理和显示技术提出了更高的要求,以达到高质量、全方位、多角度的视频获取和观看效果。

1 手术室视频系统

在手术室内部安装专用摄像头、录像设备等可以获取手术室内的动态图像,对手术过程进行实时记录、监控、转播和存储,以便进行临床手术示教并在术后对影像资料进行学术探讨,手术室视频系统提升了手术室的功能和效率,也使得手术质量得到提高。

目前,很多医院都开发或者引进了临床手术示教系统,但现有的系统普遍存在一些设计缺陷和技术问题,最为突出的如手术视频清晰度低、图像失真严重、色彩还原能力弱、图像质量不高等问题,并且传统的显示系统往往都用一个显示器显示一路视频信号,无法全面地获取手术室内的各种图像信息,难以满足全方位、多角度的视频观看和研究的需要。当需要同时显示多路视频信号时,就需要多个显示器,造成资源浪费且操作不便。

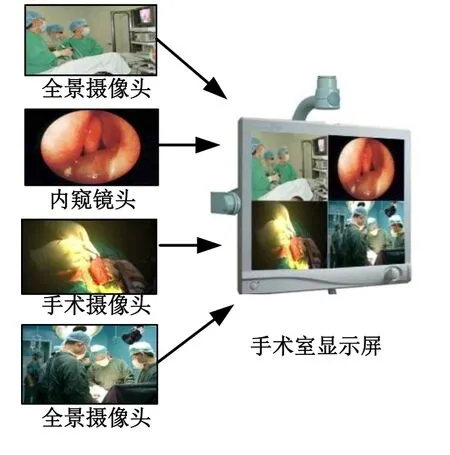

针对上述情况,本研究设计了高清视频控制器,可以对手术室内的多路高清视频信号进行处理,实现高清晰度视频信号的多合一显示。将多路视频信号按照一定的比例缩小后合成一路视频信号,传送至显示器屏幕显示,这样一台显示器屏幕被分割成多个大小相等的部分,每一个部分显示一路视频图像,与此同时,也可以切换至某一路视频(所输入的视频信号中的一路)的独立显示。这样,大大增加了显示器的灵活性,节约了空间设备资源[1]。示意图见图1。

图1 系统示意图Fig.1 Diagram of the system

2 高清串行数字信号(HD-SDI)的构成

HD-SDI的全称是为高清非压缩串行数字接口,数字视频接口是非线性编辑系统中数字信号输入和输出的通道,对视频质量的好坏有直接的影响。HD-SDI标准由SMPTE(电影电视工程师协会)制定,HD-SDI能够以简单、低成本的方式传送高速率的高清数字视频信号,在当今的广播和视频产品领域得到了广泛的应用[2]。SMPTE292M标准定义了通过HD-SDI传输速率为1.485 Gbps的串行数字接口的数据格式。

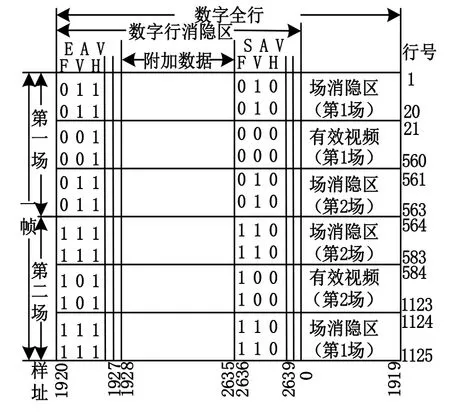

以隔行扫描1080P50i为例,每帧图像分两场扫描。数字视频分量采用Y:Cb:ξ 4:2:2格式,每帧画面亮度(Y)像素数为1 920×1 080,带宽为30 MHz;2个色差信号(用基色信号减去亮度信号就得到色差信号)像素数各为960×1 080,带宽为15 MHz;根据采样定理,取样频率必须在带宽的2倍以上。SMPTE将亮度信号的采样频率定为74.25 MHz,色差信号采样频率定为37.125 MHz,量化位数为10 bit。采用74.25 MHz采样频率,则数字设备向外输出每帧内的像素数据时,色差信号按次序时分复用。亮度信号Y和经过时分复用后的色差信号组合成一个包含两个分量的数字信号(Y)或(Cr,Y),数据宽度为20 bit。复用次序如下:(Cb1,Y1)(Cr1,Y2)(Cb3,Y3)(Cc3,Y4)…,其中Yi表示每行的第i个亮度有效取样,而Cbi、Cri表示与Yi取样点位置相同的色差Cb和Cr分量的取样。将此数据转换为串行数据,即构成串行数字信号,其传输速率为74.25 MHz×20=1.485 Gbps。

HD-SDI信号里,除了有效视频信号之外,在视频信号消隐区间里还有其他的信息[3]:

(1)EAV/SAV:定时基准码,有效数据的起始和结束标志(样址:1920~1923,2636~2639);

(2)LN:行数信息(样址:1924~1925);

(3)CRC:冗余校正码(样址:1926~1927),检查亮度信号、色差信号的数据错误;

(4)ANC:辅助数据(样址:1928~2635)。

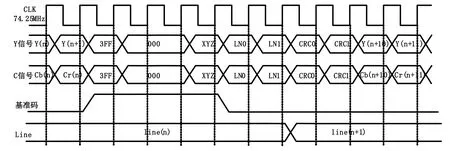

HD-SDI隔行扫描数字场定时关系见图2。

图2 数字场定时关系图Fig.2 Digital domain timing relational graph

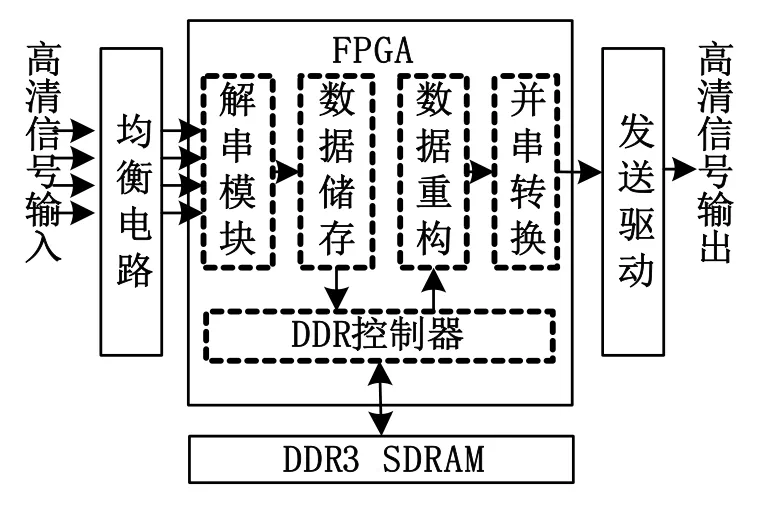

3 多路高清视频合成系统

数字视频处理过程中涉及到大量的数据传输和交换。其核心数据处理单元与片内数据缓冲区,以及内存控制器与片外存储芯片之间的数据吞吐能力直接影响到视频处理的速度[4]。随着FPGA技术的迅速发展,内部丰富的硬件逻辑资源和可编程的特性使得FPGA在高性能、高灵活性的数字视频处理中被广泛采用,该多路高清视频合成系统以高性能的FPGA为核心,经过均衡后的HD-SDI信号输入FPGA,在FPGA中进行视频信号的解串、存储控制、帧格式的重构等处理。FPGA中对信号的处理过程用Verilog HDL语言来编程实现,系统由视频信号均衡模块、视频信号解码模块、视频帧存储及重构模块、视频输出模块等构成,系统主要模块框图见图3。

图3 系统组成框图Fig.3 System frame composition diagram

3.1 信号均衡电路

在视频信号的传输过程中,输入信号的衰减程度不但与电缆长度成正比,而且与频率的平方根值也成正比[5],HD-SDI的传输速率高达1.485Gbit/s,频谱分布在4 GHz以上,经过不同长度的电缆传输以后,信号会不同程度的衰减,抖动增大。因此,必须使用电缆均衡器,在相应的频率范围内对衰减信号进行提升和补偿,以满足后续处理的要求。均衡器采用National的LMH0384,该芯片支持SMPTE 424 M及SMPTE 292M标准,以1.458 Gbps的速率传送信号,传送距离可达200 m。

3.2 解串电路

为实现对视频数据的编辑处理,需要将串行数字信号转换为并行数据。由于高清数字视频信号传输速率较高,数据量较大,对传输质量要求严格,因此本设计在FPGA内部完成相应的功能模块,无需其他外围电路,保证视频信号的传输质量。

系统选用Xilinx公司的高性能FPGA芯片XC6VLX240T作为核心芯片。其内部集成24个高速串行收发器(GTX),能以480 Mb/s~6.6 Gb/s的数据速率运行,可以实现灵活编码,占用很少的FPGA逻辑资源,非常适合实现HD-SDI信号的接受和发射,Xilinx公司提供的triple-rate SDI core IP具有支持SMPTE标准的HD-SDI的接收器和发射器接口,通过一个GTX参考时钟频率就可以确定传入的SDI的比特率和配置,并完成信号解码功能。均衡电路输出一对差分信号,送入GTX接收器,通过对GTX接收器的控制,输入的串行信号转换成20bit的并行信号,同时输出并行时钟信号RXRECCLK,传送到triple-rate SDI,完成视频信号分量的提取及信号误码检测和纠正。

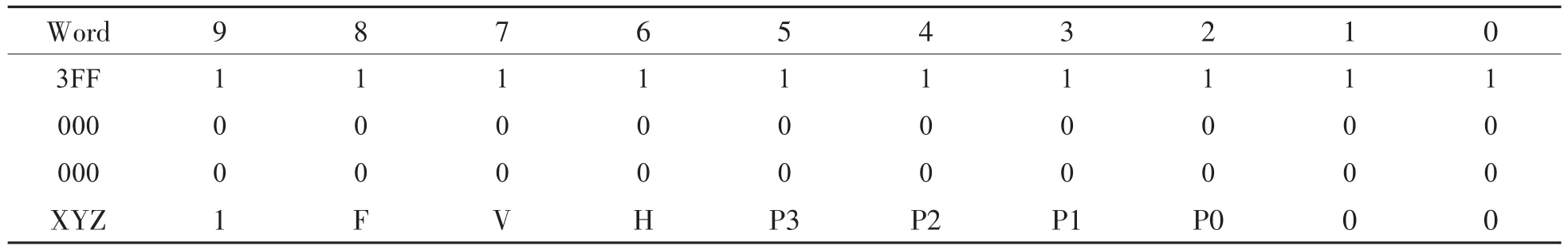

根据输入的时钟频率,进行信号模式判断,并输出两路10bit的信号,分别是HD-SDI信号里的亮度信号Y和色差信号C,以及基准码、行号等标识信息,数据时序图见图4。

后解串后的并行信号进行误码检测和误码纠正(EDH),检测并纠正传输及解码过程中出现的误码,包括视频标准检测、循环冗余码检测、时钟基准误码检测、锁定误码检测、辅助数据效验检测HD信号行数误码检测及对应的纠正。最后将2路10bit的并行信号传输到下一模块进行处理,完成HDSDI数据流的解串。

3.3 视频有效信号的获取

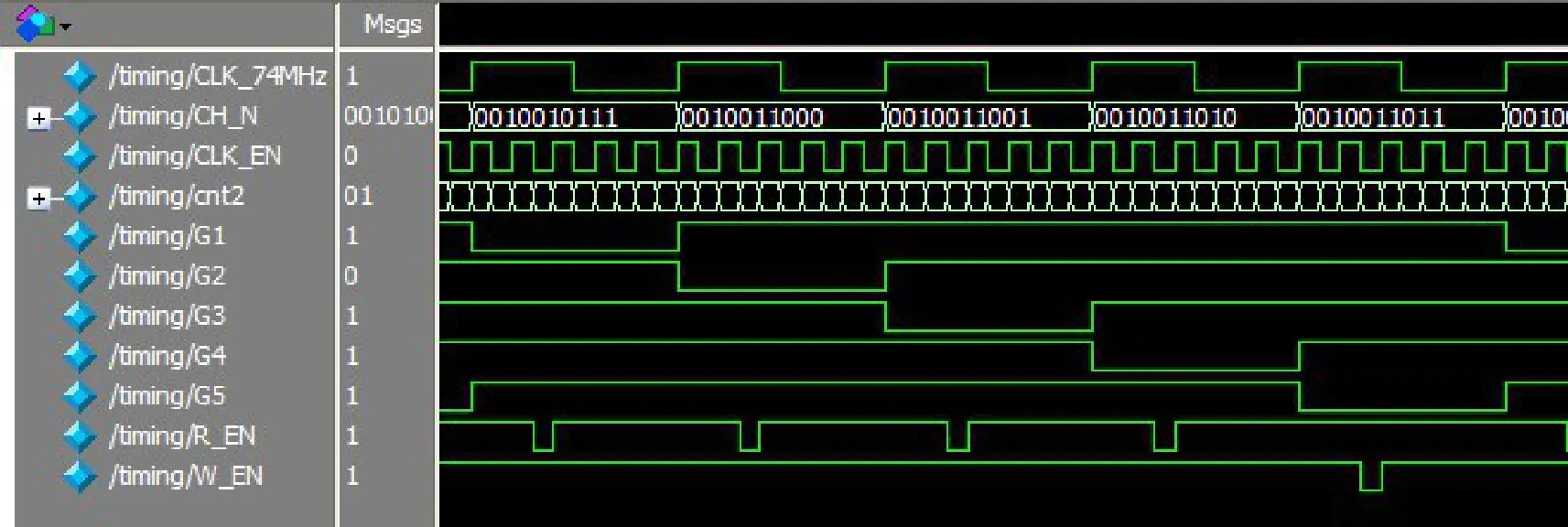

每帧视频信号中并非都是有效数据,因此在对数据进行存储时要将有效视频信号分离出来。对于HD-SDI,每行有效信号数据起始端有定时基准码SAV,结束端有EAV。定时基准码由四个字组成,每个字为10比特,前三个字固定不变,为3FF 000 000,第四个字是由奇偶场F、场消隐V和行消隐H及保护比特Pi组成,Pi的状态取决于F、V、H的状态,其比特分配见表1。

F为0表示奇数场,1表示偶数场,V为1表示场消隐,0表示场有效,H为1表示在EAV中,0为SAV中。只有在这两个标志位之间的数据才是有效的视频数据,要将其分离出来,构造一个检测电路,对定时基准码进行检测,代码如下:

wireV_check=( (R3==10'h3ff) && (R2== 10'h000)&&(R1==10'h000))?1:0;

always@(posedge CLK)

begin

R1_buf=V_DATA;R2_buf=R1;R3_buf=R2;

end

always@(negedge CLK)

begin

R1=R1_buf;R2=R2_buf;R3=R3_buf;

end

always@(posedge CLK)

begin

if(V_check==1)

begin

START=~V_DATA[6];Field=V_DATA[8];

end

当检测到三个存储器的值为3FF、000、000时,V_check将会置1,然后存储下一位数据XYZ,由表1可知,区分SAV和EAV是根据XYZ[6]来区分,区分奇偶场是根据XYZ[8]来区分,当XYZ[6]的值为0即SAV时,START有效,系统开始采集视频数据,完成有效数据的分离。

3.4 视频信号的存储及读取

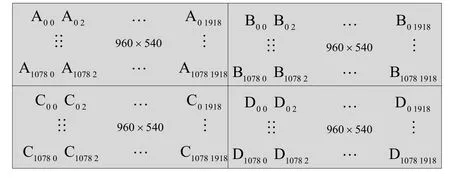

以四画面合成为例,将四路1 920×1 080格式的高清视频数据合成一路,每一路视频画面的有效像素点变换为原始数据的1/4,即为960×540,应在垂直方向和水平方向上进行1/2的抽值。考虑到系统可实现对单路信号的切换显示,应对每路视频信号的全部有效数据进行存储,在数据合成时,对数据进行隔点和隔行的读取即可。

在外部存储芯片中,为每路信号预留出一帧图像的存储空间,在一个时钟周期内,四路信号各进行一次数据的写入操作,并对其中的一路信号的存储空间进行一次读操作,其仿真时序图如图5所示。

图4 视频数据流时序图Fig.4 Video data flow sequence diagram

表1 视频定时基准码比特分配Tab.1 Bit allocation of video timing reference number

图5 视频数据存储和读取仿真时序图Fig.5 Emulation sequence chart of video data storing and reading

数据的写入操作按照每一路信号规定好的起始地址分别进行地址累加写入即可,四路高清视频信号的存储起始地址分别设为Aij、Bij、Cij、Dij,当下一个数据写入时,地址j自动加1,当j的值为1 919时,说明图像中第一行的像素点写入完毕,j数值清零,i数值增加1,进行下一行数据的写入,当i为1 079,j为1 919时,即一帧图像写入完毕,i、j清零,进行下一帧图像的写入。

根据画面合成模式要求,对每路数据进行隔点和隔行读取,进行组合,构成1 920×1 080个有效像素数据。合成视频的有效数据的前540行由第一、第二路数据构成,后540行由第三、第四路数据构成。第一行数据前面960个像素数据由第一路A0j里的A00、A02、A04…A01918隔点抽取出构成的,后960个像素数据由第二路B0j里隔点抽取构成的。下一行则有A2j和B2j隔点抽取构成。同理第541行是由第三路数据C0j和第四路数据D0j隔点抽取构成,直至第1 080行,一并构成新的一帧图像里的有效数据。其数据地址映射示意图见图6。

图6 视频数据合成地址映射图Fig.6 Mapping of video data synthesis location

由于数据量较大,选用外部的存储器件DDR3 SDRAM MT4JSF6464HY-1G1。利用Xilinx公司的存储器接口生成器工具(MIG),在MIG工具的GUI图形界面,根据存储器件型号选择相对应的模板、总线宽度和速度级别,并设置CAS延迟、突发长度、引脚分配等关键参数,即可生成控制器的RTL代码(HDL代码)和UCF文件(约束文件)。并且可以在代码生成后灵活修改这些代码,方便实现视频数据的存储和重构。

3.5 并串转换电路

通过数据的缓存和重构,对四路高清信号中的Y、C分量分别进行了组合,将信号传送至FPGA内部的高速串行收发器GTX的发送器部分,并输入参考时钟频率,通过对GTX发送器的控制,将输入的20 bit并行信号转换成串行信号,完成YC的复合处理。

3.6 帧信号消隐信息的添加

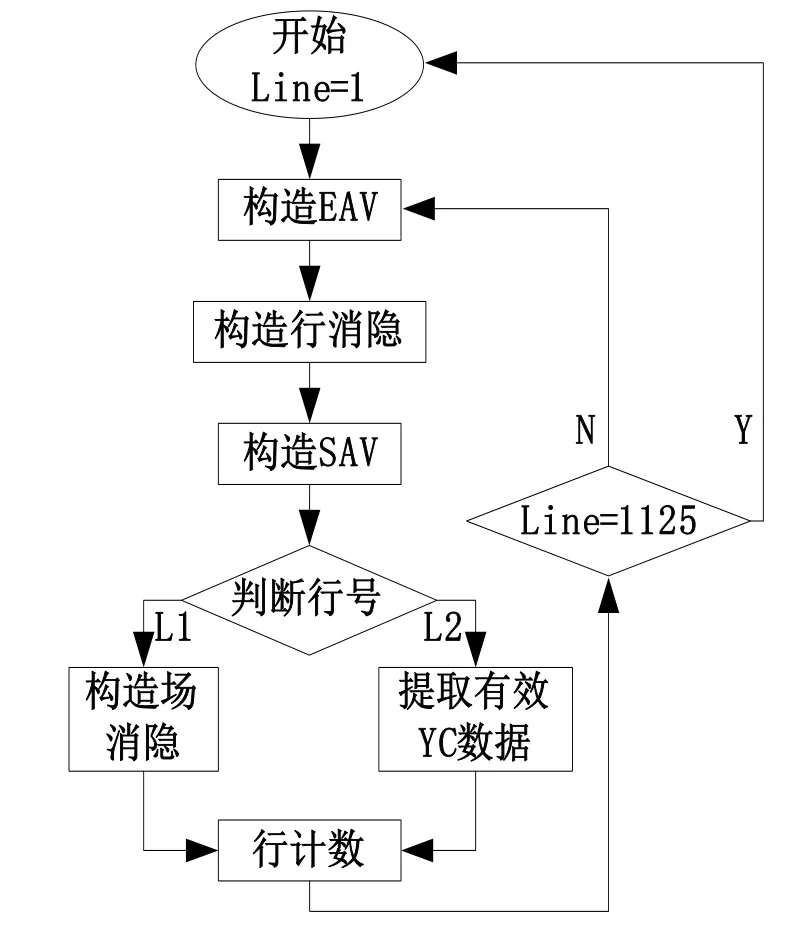

重构数据要满足高清HD-SDI并行分量信号所要求的格式输出,则要在信号中构造高清分量信号中的视频定时基准码SAV、EAV,行消隐数据、场消隐数据,处理过程的流程图如图7所示。

图7 HD-SDI帧信号构造流程图Fig.7 HD-SDI flow diagram of frame signal structure

3.7 视频输出

HD-SDI信号在输出传输过程中会有不同程度的衰减,会导致阻抗失配、反射、信号损耗等,降低了信号的保真度。因此高清视频信号的输出端,设计高清视频信号电缆驱动器模块,采用National的电缆驱动器LMH0303,支持多种SMPTE标准并具有输入信号丢失检测功能,保证了高清视频信号的传输质量。

4 总结

本设计是针对手术室内的多路HD-SDI信号进行的处理变换,对各路高清视频信号进行信号均衡、解串、有效视频信号分离、存储并重构成一路高清视频信号,传送至高清视频显示屏,进行多画面的显示。该设计在保证视频质量的同时,节约了设备资源,符合现代医院数字化手术室对空间的要求,能够满足医院高清晰度、全方位、多角度的手术室视频观看和研究的需要。

[1] 李鸿强,苗长云,刘晓军.HD-SDI数字视频信号处理及传输的FPGA设计与实现[J].计算机应用研究,2007,24(10):269-272.

[2] 姜宏旭,刘亭衫,李辉勇,等.FPGA+DSP异构视频处理系统中基于SRIO的数据高效传输方法[J].计算机学报,2015,38(6):1119-1130.

[3] 冯永茂,徐秀知,邓春健.基于FPGA的数字视频多窗口内存地址生成器设计[J].液晶与显示,2006,21(6):708-713.

[4] 储蓄蓄,陈伟,樊丰.长线电缆数字基带传输中自适应均衡器的设计[J].电视技术,2009,33(S1):126-127.

[5] 周雄.浅谈高清数字化手术室系统的设计和实现[J].中国继续医学教育,2015,7(33):20-21.

[6] 唐晓,周莉,孙涛,等.高清视频后处理模块的ASIC设计[J].计算机工程与应用,2016,52(3):7-11.

[7] 董青,朱洪翔,祁晓鹏.基于FPGA视频合成系统设计与实现[J].计算机测量与控制,2016,24(4):247-249.

[8] 徐大鹏,孙海江.HD-SDI视频嵌入式图像采集系统与设计[J].计算机测量与控制,2015,23(9):3213-3215.

Research on multiplex high definition video synthesis system for digital operating room

WEI Tao1,YANG Yongyong2,SHAO Lei3

1.Department of Medical Equipment,Shanghai Traditional Chinese Medicine Hospital,Shanghai 200071,China;2.Department of Engineering,Shanghai Medical Instruments Co.,Ltd,Shanghai 200093,China;3.Office of Scientific Research,Tongji Hospital,Tongji University School of Medicine,Shanghai 200065,China

ObjectiveThe multiplex high definition video synthesis system for digital operating room is important for improving the quality of medical teaching and tele-surgery.MethodsTo solve the problems such as lower resolution and less visual angles of video in domestic operating room,a system of four HD-SDI video signals synthesis was designed,with the hardware structure of field-progtammable gatearray,and on-site tests were performed.ResultsThe system worked stably,and was convenient for operation.ConclusionDesigning and implementing multiplex high definition video synthesis system plays a vital role in the construction of digital operating room.

Digital operating room;High definition video synthesis;Field-progtammable gatearray

R197.39

A

2095-378X(2016)04-0281-06

10.3969/j.issn.2095-378X.2016.04.016

2016-11-11)

魏 涛(1982—),男,本科,助理工程师,研究医学装备管理

邵 蕾,电子信箱:13818165282@163.com