VLSI低功耗设计方法的研究

樊持杰 司巧梅 张 丹

(牡丹江师范学院,黑龙江 牡丹江 157011)

VLSI低功耗设计方法的研究

樊持杰 司巧梅 张 丹

(牡丹江师范学院,黑龙江 牡丹江 157011)

针对近年来VLSI功耗问题越来越被关注,尤其是在电池供电的便携式设备中CMOS电路的功耗问题尤为重要。本文对VLSI的低功耗设计方法进行了研究,首先对VLSI作了简介,其次分析了VLSI的功耗来源,最后就如何实现VLSI开关功耗的低功耗设计,着重讨论了几项技术。本文对电子行业从业人员有一定的积极意义。

VLSI;CMOS;低功耗;设计方法

1 引言

近年来,随着电路规模逐渐扩大,其处理数据速度越来越快,而其集成度也不断提高,功耗越来越大。如今人们对便携式设备越来越依赖,但其不给力的电池续航能力,以及设备大功耗带来的温度过高而致系统不稳定的问题,都迫使我们就如何降低大规模集成电路的功耗进行思考。选择合适的低功耗方法,必须首先要对VLSI中芯片的功耗进行预估分析,通过早期的分析,我们可以使用不同设计层次的技术来降低大量的功耗,从而更容易达到功耗的要求。下面本文主要对VLSI进行功耗分析,并重点研究降低其功耗的设计方法。

2 VLSI功耗分析

VLSI中CMOS电路的功耗来源主要有两种:动态功耗和静态功耗。

2.1 动态功耗

(1)开关功耗

开关功耗是指当反相器的输入是理想阶跃波时,纯电容负载CL进行充放电所消耗的功耗。其公式为:

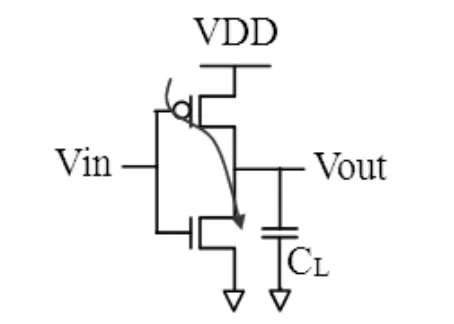

公式中,f为时钟频率,a为翻转活动因子,也就是每个时钟周期中,状态发生变化的器件的个数,Vdd为供应电压,CL为负载电容,不仅依靠电路结构,还依靠系统的输入类型。如图1所示为CMOS电路的开关功耗。

图1 CMOS电路的开关功耗

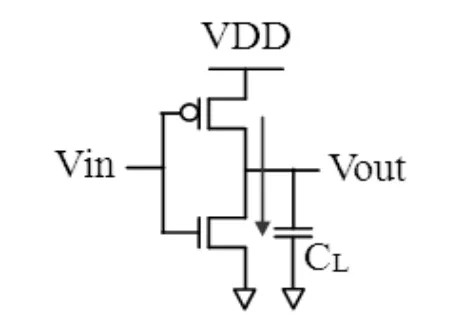

(2)短路功耗

反相器输入是非理想阶跃波时,会在输入波上升或下降沿的瞬间,有一个N管与P管同时导通的区域存在,这一过程引起的功耗我们称为短路功耗。其公式为:

PS=ISTVdd

公式中,IST为电路的短路电流值,VDD为电源电压值。如图2所示为CMOS电路的短路功耗。

图2 CMOS电路的短路功耗

2.2 静态功耗

静态功耗在理论上讲是不存在的,因为在稳定状态下,CMOS电路不存在电源到地的直接路径。然而,实事上,扩散器与衬底间的PN结上会存在反向泄漏电流,而造成一定的功耗。CMOS电路主要存在以下几种泄漏电流:栅泄漏电流、亚阈值泄漏电流、反偏结泄漏电流,以及门栅感应漏极泄漏电流。这些泄漏电流所引起的功耗之和就是芯片的静态功耗。其计算公式为:

PL=IleakageVdd

公式中,Ileakage为泄漏电流的值,Vdd为电源电压值。

通过上述分析,动态功耗与静态功耗之和就是电路的总功耗:

P=PD+PS+PL

其中,短路功耗PS和静态功耗PL占总功耗的比例很小,而且PS和PL与工艺密切相关,在进行系统设计时很难控制,因此本文主要是对如何降低电路的开关功耗进行讨论。

3 VLSI低功耗设计实现方法

降低VLSI功耗有很多方法,主要分为对其系统层、算法层、结构层、逻辑层以及物理层的设计方法研究。其中对系统层、算法层和结构层的设计改善,对VLSI整体功耗的降低有着非常明显的作用,也是本文下面重点研究的内容。

3.1 动态功耗管理

动态功耗管理是系统层的低功耗设计技术,主要是指对电路在正常工作状态时产生的功耗进行管理。在电路正常工作时,由于各模块的活动级别有所不同,因此有的会被系统调用,有的不被调用。动态功耗管理的核心思想就是:在执行某一操作时,将电路中不被调用的模块挂起,来降低电路功耗。如在进行浮点运算时,整数运算单元处于不被调状态,我们可以将其挂起以降低功耗。

3.2 算法层设计技术

在这一算法级设计层面上,我们通过使用恰当的编码技术来降低翻转活动,从而来降低功耗。事实证明,这是一个比较有效的方法,对于如总线这种结点电容较大的信号线,效果尤为明显。总线的编码技术有多种:如独热编码(One-Hot)、格雷码(Gray2code)、T0编码等,其中One-Hot编码通过对二进制数进行编码,实现在一个二进制数中,仅允许有一位不同于其它位的值。如表1所示,为独热编码(One-Hot)与三位二进编码的比较。

表1 三位二进制编码和One-Hot的比较

从表1可知,在连续变化时,二进制编码可能会有多个数位同时发生变化,而One-Hot编码仅有一个数位发生变化。这样在访问相邻两个地址内容时,总线的翻转活动次数比较少,从而来降低功耗。

在算法级设计中,还存在一种基于减少翻转电容的设计方法,主要是对执行算法所需的操作类型和操作个数进行充分考虑。不同类型的操作,其所消耗的功耗也不同,如乘法器操作的功耗要比加法器操作的功耗大,因此我们既要减少算法的操作个数,也要考虑操作的类型。

3.3 结构层设计技术

结构层也称为RTL(Register Transfer Level,寄存器传输层),在这一层的设计中会常用到加法器、乘法器、存储器以及寄存器堆等。结构层的优化设计技术有并行结构、流水线结构等。

(1)并行结构

如图3所示,为16位乘法器应用参考结构与并行结构的比较图。

图3 参考结构与并行结构示意图

由图3可知,并行结构是通过牺牲芯片面积来降低功耗的,与参考结构具有相同的计算速度的前提下,其工作频率能够降为原来的1/2,而且电源电压也可以降低。并行结构将一个功能模块“复制”为N(N≥2)份,因为有N个同样的模块同时工作,所以每个模块的时钟频率就成为1/N分频,每个模块的工作速度同样降为原来的1/N,基于上面公式中延时与工作电压的线性关系,电路面积增长N倍,同时电容增长N倍,但电压和频率却下降N倍,则最后功耗降低了N2倍。

并行结构可以应用多个单元并行,但同时随着单元数的增加,则可能会出现一些问题:一是芯片面积增大,造成成本增加;二是布线长度增加,造成线电容增加;三是电压的降低会受阈值电压的限制,因此电压接近阈值电压时,会造成延迟退化。基于以上问题的影响,如果并行单元过多,反而会使功耗增加,所以在设计时要充分考虑这些因素,从而使并行效果达到最优。

(2)流水线结构

流水线结构的核心思想是:控制通过数据通路指令流,来获得最大的吞吐量,从而提高电路性能。这种结构将指令分为多个步骤,利用模块的时钟周期来并行处理多条指令,从而提高电路的性能。如图4所示为CPU的流水线结构图。

图4 CPU流水线结构图

图4中将CPU数据通路分为5段流水作业,其中每段由一个模块完成,模块与模块之间插入寄存器来驱动这些模块。利用这种方法,我们可以实现与并行结构相似的低功耗结果,而电路面积其本保持不变。但流水线结构也有其自身的缺陷:一是这种结构设计具有较高的复杂性,需要插入流水线寄存器,从而会导致芯片面积增加,而且由于寄存器还需要增加时钟控制,这样就会造成时钟单元负载增大;二是在一些算法的流水线结构设计中,会出现“管道冒险”现象,损害流水线的操作效率。

4 结语

除了上面分析到的技术,VLSI低功耗设计技术还有多种,如:阈值电压设计技术、门控时钟技术、SOI(硅绝缘体)设计技术等。由于篇幅问题,本文就不再详述。总之,随着技术的发展,人们已不只关心设备的运行速度,还很关注设备的工作寿命。而高功耗必然会导致低寿命,因此对器件的低功耗设计研究具有战略意义,它关系到企业产品的市场竞争力,甚至是企业的生死存亡。

由于作者水平有限,本文还有很多不足之处,希望通过今后不断的学习进步,能对VLSI的低功耗设计方法有更深的理解与研究,弥补本文的缺憾。

[1]陈秀华.基于图论的VLSI中最小斯坦纳树问题及其改进算法[J].南京师范大学学报:工程技术版,2015(4):47-52.

[2]许斌,罗俊.VLSI CMOS模拟集成电路可靠性仿真设计技术[J].微电子学,2013(2):250-256.

[3]陈耀.计算机硬件组装虚拟实验系统设计与实现[J].电脑与电信,2014(12):67-69.

Research on Low Power Design Method of VLSI

Fan Chijie Si QiaomeiZhang Dan

(Mudanjiang Normal College,Mudanjiang 157011,Heilongjiang)

In recent years,VLSI power problems have been paid more and more attention,especially the power consumption problem of CMOS circuit in battery powered portable devices.This paper studies on the low power design method of VLSI.Firstly, VLSI is introduced;then the VLSI power consumption source is analyzed;finally,several techniques to achieve low power consumption design of VLSI switch power are discussed.This paper has a certain positive significance for the electronic industry practitioners.

VLSI;CMOS;low power consumption;design method

TN47

A

1008-6609(2016)05-00101-03

樊持杰,女,湖南宁远人,副教授,研究方向:计算机教育,数据挖掘。