DDR2高速PCB设计和信号完整性分析

邓思维,凌 凯

(许继电源有限公司 研发部,河南 许昌 461000)

DDR2高速PCB设计和信号完整性分析

邓思维,凌 凯

(许继电源有限公司 研发部,河南 许昌 461000)

随着现代高速电路设计的发展,DDR2因其内存强大的预读取能力成为许多嵌入式系统的选择。然而,DDR2的仿真工作不仅繁琐耗时量大,对EMI的仿真也比较困难,给PCB设计也带来了大量的工作难点。文中针对DDR2高速电路中存在的信号完整性问题进行了分析,提出了PCB设计要点。并以单个DDR2存储器与控制器间的PCB设计为例,对如何在减少仿真工作的情况下成功完成一个可用的设计进行了论述。

DDR2;PCB;信号完整性

DDR2内存强大的预读取能力使其成为许多嵌入式系统的选择,然而,由于其具有的高频与快速的上升、下降沿,给PCB设计带来了困难。PCB设计者不仅需要严格遵循通用的高速PCB布线规则,更要对系统中的各种信号完整性问题进行一一分析与解决。当然,对于电路中的问题逐个仿真是一种比较有效的方法,虽然仿真成功并不能保证设计完美,却可以排除大量的错误。但是,DDR2的仿真工作不仅繁琐耗时量大,对EMI的仿真也比较困难,特别当一些单位并没有专门的仿真人员或者项目时间紧张,逐个仿真是不切实际的。本文以单个DDR2存储器与控制器间的PCB设计为例,讲述了如何在减少仿真工作的情况下成功完成一个可用的设计。

1 DDR2电路PCB设计步骤

DDR2电路的主要组成部分为控制器U1和DDR2存储器U3,此外还有一些小封装的串联电阻和旁路电容。

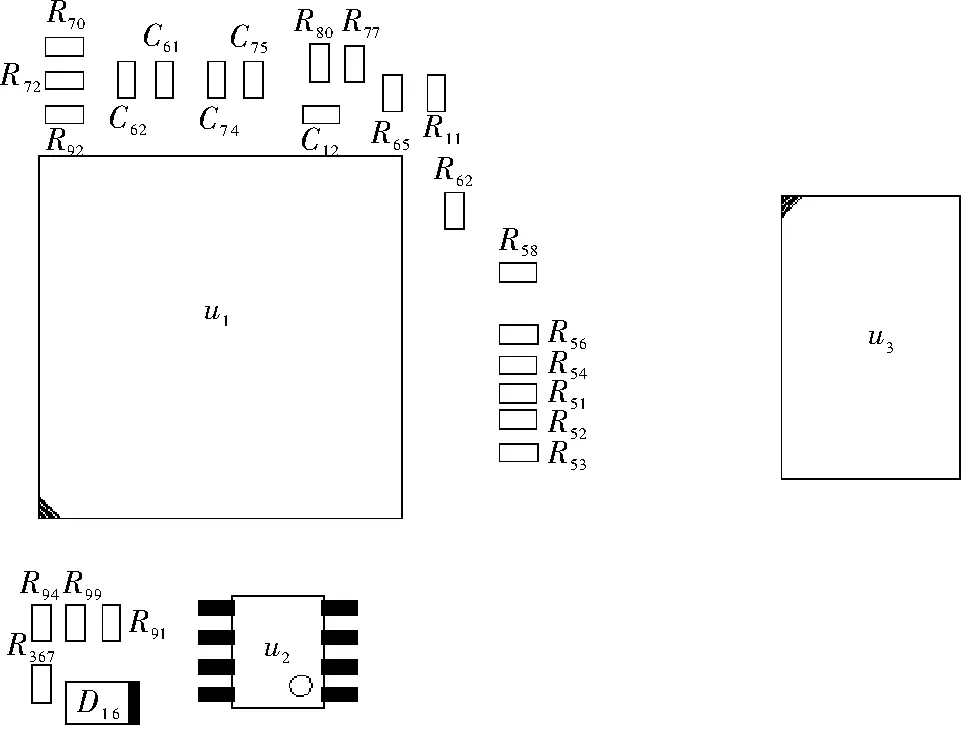

如图1所示,从U1到U3要形成一个电路隔离区,串联电阻在两者中间,而旁路电容在线路板的另一面。DDR2电路与其它电路隔离距离越大越好,推荐20 mil(1 mil=0.025 4 mm)以上。

图1 DDR2电路正面布局图

在满足布线空间的情况下,控制器U1与DDR2存储器U3之间的距离越小越好。当图1中所示仅使用一个DDR2存储器时,二者的中心最好在同一条直线上。这样的布局是为了保证走线的长度,一般信号线长度控制在5 000 mil以内。旁路电容是在电源和地平面并联的体积很小的电容,要放在非常靠近需要旁路的引脚处,降低寄生电感,从而减少电源的高频阻抗参数。摆放旁路电容时,过孔仅当另一个高速旁路电容在另一面时才可以共用,否则会大幅增加寄生电感。

高速电路非电源线的线宽和过孔尺寸要结合空间的大小和印制板制作工艺来决定,本例中选择5 mil的信号线线宽与6 mil/18 mil的过孔,而电源线尽量做到20 mil的线宽。DDR2电路隔离区必须要有自己完整的地平面和电源平面。

2 信号完整性分析与应对方法

在DDR2电路中,飞行时间延迟和时钟偏移是最重要的信号完整性问题之一。飞行时间延迟是信号从驱动端传输到接收端,并达到一定电平之间的延时。时钟偏移是指由同样的时钟产生的多个子时钟信号之间的延时差异。由于DDR2信号的传输速度快、周期短,必须保证同组信号中第一个到达接收端并稳定的信号和最后一个到达接收端并稳定的信号之间的时间差不能大于一个周期。也就是说,飞行时间延迟和时钟偏移要控制在严格的范围内,否则就会造成数据混乱的现象。影响延迟的因素有很多,包括线长、线宽、铜厚、板层结构等。对于线长而言,直接严格控制PCB上走线的传输距离;对于其它因素,因为单位长度的线延迟是固定的,可以通过PCB的走线阻抗来控制。

2.1 等长控制

为调整时延一致,对于DDR2的时钟、地址控制线、数据、DQS等信号的等长要求很高,走线的具体要求如下:

对于时钟线(CK)、地址线、片选及控制线(DDR_A、BA、CS、CAS、RAS、WE、CKE),这一组线的标准长度为组中信号的最长曼哈顿距离,误差在±50 mil以内。时钟线要求精确匹配差分对走线,二者误差允许在25 mil以内,最好控制在5 mil。地址线,片选和控制线与时钟线尽量做到等长,可以比时钟线长,但绝对不能短,误差在100 mil以内。

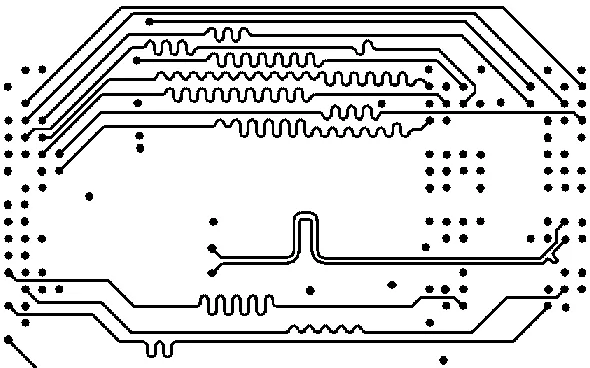

对于数据线(DDR_D,DQM)、时钟线(DQS),这一组线的标准长度同样为组中信号的最长曼哈顿距离,误差在±50 mil以内。数据线与时钟线尽量做到等长,误差控制在±50 mil。为达到要求,走蛇形线是必不可少的,另外,一条信号线从控制器到DDR2存储器,长度并不是单指线长,还要把过孔,元件封装内部引线长度计算在内。图2~图5所示,即为DDR2电路的4层走线。

图2 布线层1

图3 布线层2

图4 布线层3

图5 布线层4

2.2 阻抗匹配

DDR2的PCB设计对于走线阻抗也是有严格要求的。差分线要求差分阻抗为100 Ω,地址线、片选和控制线,数据线及数据时钟线的单端阻抗都应控制在50 Ω。

PCB上走线的阻抗是传输线的固有属性,与走线宽度、PCB材料厚度和介电常数有关,所以,阻抗匹配具体的实现要通过PCB设计者和印制板制作厂家的共同努力来完成。Si9000是一款专门计算走线阻抗的软件,PCB设计者可以通过此软件计算DDR2走线中的差分阻抗和单端阻抗,以保证最终设计可以通过印制板制作厂家的对印制板结构的调整达到阻抗匹配的要求,图中为Si9000软件中计算单端阻抗和差分阻抗的示意图,图6中标示的元素即为影响阻抗计算的参数。

图6 阻抗计算示意图

本例中的信号线线宽为5 mil,使用FR4板材,通过软件计算是可以达到阻抗要求的,所以与印制板厂家沟通即可实现阻抗匹配。

2.3 串扰

串扰是最常见的信号完整性问题之一,它存在于任何一对信号网络之间,且不可能被消除,只能减小。减小串扰的方法很多,但采取减小串扰的措施总会增加系统费用,因此,能够选用合适的方法使设计在容许的串扰范围内是至关重要的。

2.4 控制回流路径

在DDR2电路中,控制回流路径可以通过PCB的叠层设计来完成,每一个信号布线层都要有一个相邻的完整的地平面来提供最短的返回路径。

串扰与两个或多个信号及其返回路径之间的容性耦合和感性耦合有关,当返回路径不是均匀平面时,增加的感性耦合比容性耦合高很多,而要使一对信号回路之间的噪声保持在可接收的水平,他们的回路互感要尽量小;当返回平面是宽平面时,串扰最低,这时容性耦合与感性耦合相当;当返回平面与信号平面相邻时,返回路径的阻抗最小,地弹噪声也最小。所以,在良好的叠层配置基础上,DDR2电路下方电源铜和地铜应当完整且完全覆盖所有的DDR2电路信号。

2.5 增大走线间距

当信号沿传输线传播时,信号路径和返回路径之间将产生电力线,围绕在信号路径和返回路径周围也有磁力线圈。它们所形成的边缘场会延伸到周围的空间,距离导线越远的地方,边缘场耦合和串扰就越小,反之则越大。

所以,增加信号路径之间的间距和减小耦合长度是减小串扰最直观有效的方法。实验证明,把间距从1倍线宽增加到3倍,可以使远端串扰减小65%。在DDR2走线中,在空间允许的情况下,使走线间距为2~3倍的线宽,尽量减小平行线的耦合长度,就可以达到减小串扰的效果。

2.6 发射

信号无论在何处遇到阻抗突变就会发生发射,传输信号会失真,这是单一网络信号质量问题的主要根源。振铃是由源端和远端的阻抗突变、两端之间不断往复多次反射引起的。所以,如果至少在一端消除反射,就可以减小振铃。本例中用到的方法是在重要位置上放置一个或多个电阻,将电阻串联在控制器端,称为源端串联端接。在重要信号上串联电阻,这些电阻在印制板上均要靠近控制器放置。源端串联端接是点对点互连常用端接方式,端接电阻与控制器内阻之和应等于传输线的特性阻抗。

3 结束语

对于涉及信号完整性问题的工程师而言,仿真实验必不可少,但好的实践经验使设计周期和反复性大幅减小。因此,一个高速印制板设计,需要同时建立在灵活的经验运用和精确的仿真模型基础上。

[1] 王芳.提高印制电路板的抗干扰能力及电磁兼容的措施[J].信息技术,2009(7):174-177,180.

[2] 聂琼,钱敏,丁杰.PCB的电磁兼容设计[J].印制电路信息,2010(12):9-12.

[3] 高进,韩军杰.基于EDA软件的PCB电磁兼容分析[J].电子产品可靠性与环境试验,2008,26(1):8-12.

[4] 俞海珍,冯浩.电磁兼容技术及其在PCB设计中的应用[J].计算机工程与科学,2004,26(4):80-81,105.[5] 吴卫兵,蒋万良.产品的PCB阶段的电磁兼容EMC设计[J].电子质量,2005(8):70-72.

[6] 朱葛俊,崔景,张海全.电子设备PCB电磁兼容设计的分析[J].内蒙古电力技术,2005,23(5):26-28.

[7] 阮琼,廖红华.高速电路板的信号完整性设计与仿真[J].湖北民族学院学报,2010,28(4):446-449.

[8] 朱文龙,钟龙平,廖乐平,等.多层高速PCB中参考平面转换的信号完整性问题研究[J].厦门大学学报,2010,49(5):629-630.

[9] 周博远,于立新,褚军舰.IBIS建模和PCB信号完整性分析[J].微电子学与计算机,2010,27(10):111-113.

[10]覃婕,阎波,林水生.基于Cadence_Allegro的高速PCB设计信号完整性分析与仿真[J].现代电子技术,2011,34(10):169-171,178.

DDR2 High-speed PCB Design and Signal Integrity Analysis

DENG Siwei,LING Kai

(R & D Department,XJ Power Co.Ltd.,Xuchang 461000,China)

With the development of modern high speed circuit design,DDR2 has become more designers’ choice due to the great pre-reading capability of its memory.However,DDR2 simulation is time consuming,and its simulation of EMI is difficult,which constitute difficulties for PCB design.The problem of signal integrity in high speed circuit DDR2 is analyzed in detail and the key points of design of PCB are put forward.Taking a PCB design of a single DDR2 memory with a controller for instance,this paper describes how to complete an available design successfully with decreased simulation work.

DDR2;PCB;signal integrity

2014- 09- 23

邓思维(1987—),女,助理工程师。研究方向:电力电子硬件设计。E-mail:dengsiwei2006163@163.com。凌凯(1987—),男,本科。研究方向:电力电子系统设计。

10.16180/j.cnki.issn1007-7820.2015.04.035

TN41

A

1007-7820(2015)04-132-04