0.13 μm CMOS工艺抗辐射触发器优化设计

李晓蓉,周昕杰(中国电子科技集团公司第58研究所,江苏 无锡 214035)

0.13 μm CMOS工艺抗辐射触发器优化设计

李晓蓉,周昕杰

(中国电子科技集团公司第58研究所,江苏 无锡 214035)

摘 要:随着体硅CMOS工艺尺寸不断减小、集成度不断提高,电路受到单粒子辐射效应的影响会变得越来越严重。在大尺寸工艺条件下常用的DICE结构触发器结构,在受到单粒子效应影响后,会产生一定脉宽的扰动并传输至下一级,对整个电路的可靠性产生影响。为消除上述影响,采用了C单元结构对触发器的输出端口进行优化设计,将原有的一个结点输出结构优化为利用两个互补的存储结点作为C单元结构的输入。利用仿真手段对优化后的结构进行验证,证明了优化后的结构有很好的抗扰动能力,同时通过优化版图设计,提升触发器结构的抗辐射能力。经过此次对触发器的优化设计,为今后超深亚微米抗辐射电路的设计提供了借鉴。

关键词:辐射效应;抗辐射设计;触发器

1 引言

随着我国航天事业的不断发展,集成电路在空间环境中的应用越来越多,这就对电路在辐射环境中的可靠性提出了很高的挑战。目前,被大家熟知的辐射效应包括:总剂量效应和单粒子效应[1]。随着体硅CMOS工艺尺寸不断减小、集成度不断提高,电路受总剂量效应的某些影响会有所改善,但受单粒子效应的影响会愈加严重。特别是对低压、高频电路而言,单粒子效应会导致整个电路数据传输出错,导致电路失效、可靠性降低。所以,国内外对单粒子效应展开了很多的研究[2~4]。

此次,针对大尺寸条件下常用的双互锁(DualInterlocked storage Cell, DICE)触发器加固结构[5],基于0.13 μm体硅CMOS工艺条件,分析了该触发器在低压、高频工作条件下抗单粒子辐射效应的缺陷,并对原有的DICE结构进行了优化。通过仿真分析及辐射实验,证明了优化后的触发器结构抗单粒子辐射效应的能力优于原有的DICE触发器结构。此次优化设计研究,为今后超深亚微米抗辐射电路的设计提供了借鉴。

2 DICE触发器介绍

2.1DICE触发器抗辐射性能介绍

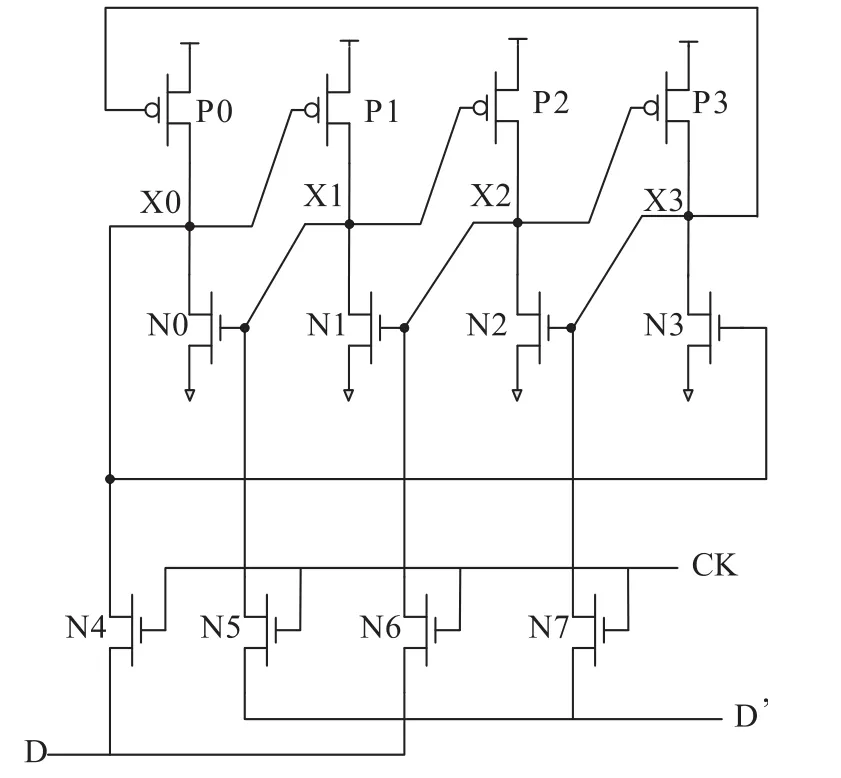

DICE触发器的加固设计中,完全采用单管反相器构成反馈回路,获得一个抗辐射的锁存结构。这种加固存储单元的设计,采用了4结点的冗余锁存,结构如图1所示。图中采用了两个传统的交叉藕合的反相锁存结构N0-P1、N2-P3和两个双向连接反馈反相器结构N1-P2和N3-P0。4个结点X0/X1/X2/X3存储了两对互补的数据(如1010或者0101),可以通过传输门的同时存取来进行读/写操作。

图1 DICE结构存储单元

单元中有4个结点存储逻辑状态,其中每个结点的状态都由相邻对角的结点控制,而这对角的结点并不互相联系,它们的状态也由其他相邻对角结点的状态控制。当单粒子效应影响X0~X3其中某一个结点状态时,该结点的状态虽然会发生变化,但当单粒子效应消失后,由于其他结点的状态没有改变,该结点会受到相邻状态的影响,而恢复到受单粒子效应影响前的状态,从而保证了存储数据不变。

在大尺寸工艺条件下,由于电路的工作频率低、工作电压高、结点寄生电容大,DICE加固触发器结构能够提供很好的抗辐射性能,满足抗辐射电路设计的需要。但是,当进入超深亚微米工艺条件后,电路的工作频率增加、工作电压降低、结点寄生电容减小,导致DICE加固触发器结构的抗辐射性能下降。

2.2DICE触发器抗辐射缺陷分析

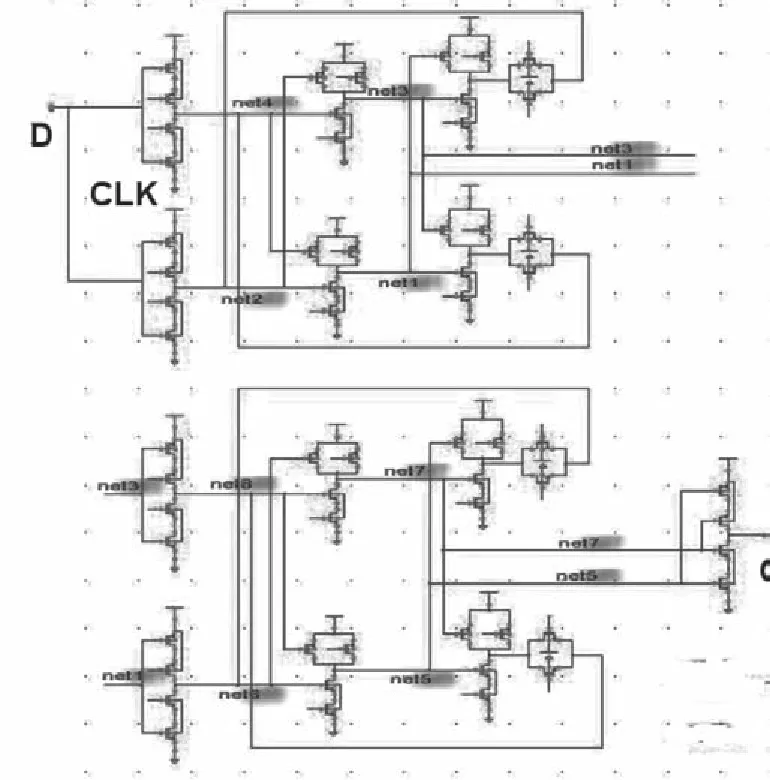

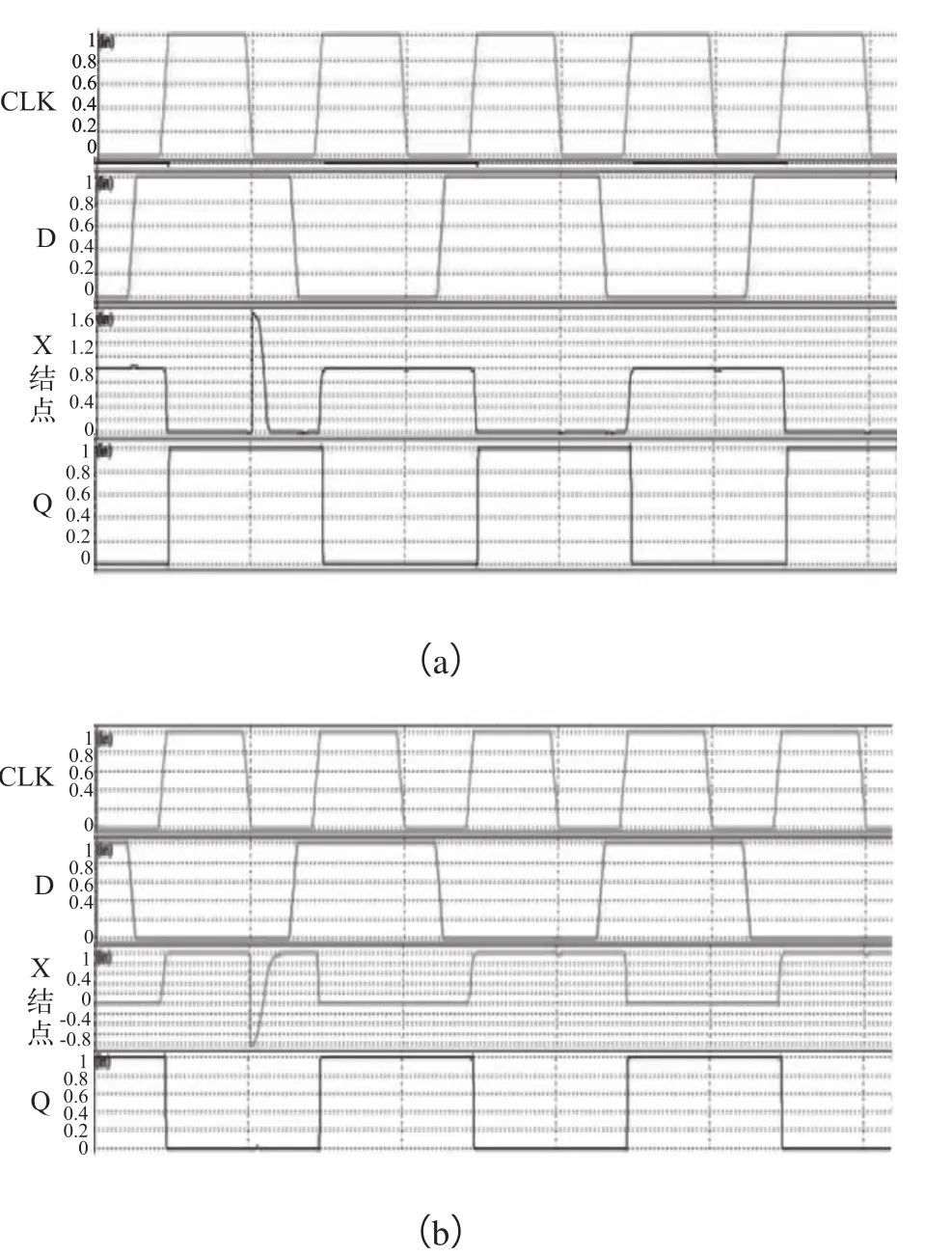

大尺寸工艺条件下的DICE结构触发器如图2,当X0~X3中的输出结点受到单粒子效应的影响,会产生一定脉宽的扰动,该扰动如果传出触发器,会对下一结点的状态产生影响。该现象的仿真波形如图3所示。该仿真结果采用的是单粒子效应电流双指数模型,结合中芯国际0.13 μm体硅CMOS器件模型参数得到。

图2 大尺寸工艺的DICE触发器结构

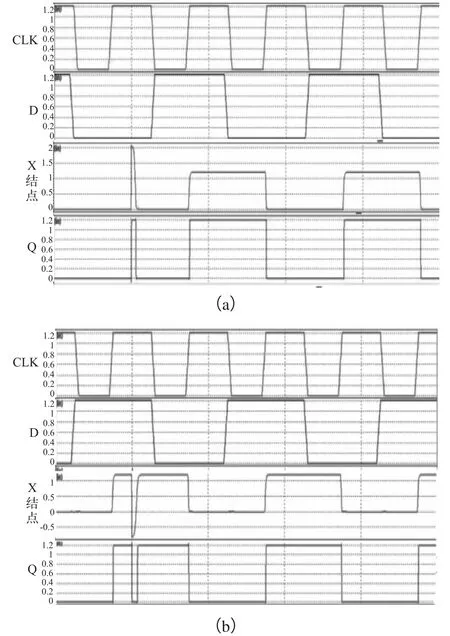

从图3(a)中可以看出:当数据端D输入为低电平信号时,由于X结点受单粒子效应的影响,使得在触发器输出端Q引入了一定脉宽的高电平。同样,从图3(b)中可以看出:当数据端D输入为高电平信号时,由于X结点受单粒子效应的影响,使得在触发器输出端Q引入了一定脉宽的低电平。在超深亚微米工艺条件下,由于电路规模庞大、逻辑更为复杂。如果受单粒子扰动产生的脉宽传入后面的逻辑,会对后面的逻辑产生影响,从而给整个电路带来不可预知的影响。所以,必须通过设计手段消除单粒子效应对输出端Q产生的脉冲扰动。

3 抗辐射触发器优化设计

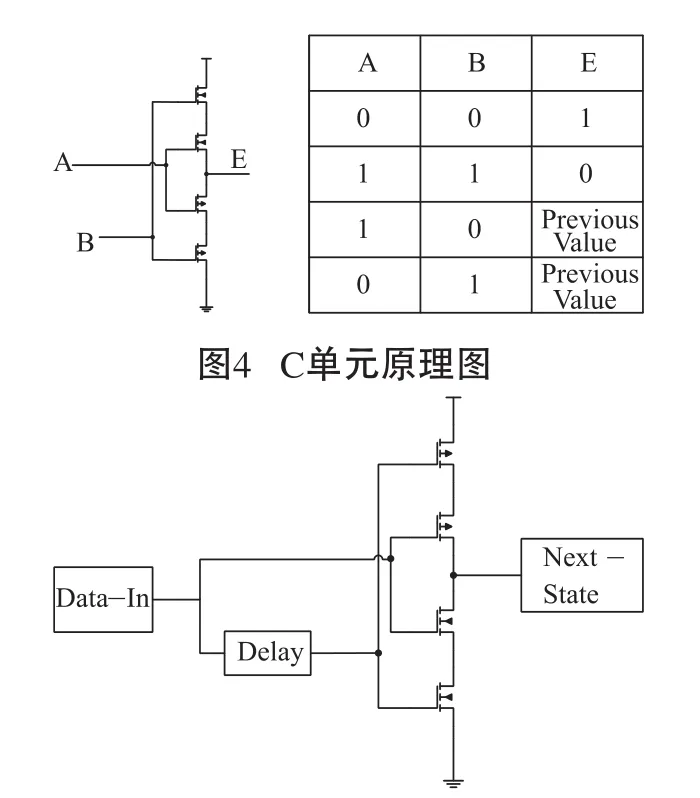

为消除单粒子效应对输出端的脉冲扰动,我们将在数据输出端之前采用Muller提出的C单元[6]进行抗单粒子效应加固。

C单元结构如图4所示,当两个输入端A和B状态相同时,输出端E的状态才会改变,此时,C单元相当于一个反相器。如果,A和B的状态不相同,E则保持原有的状态不变。

Mongkolkachit等人首先将C单元用于抗辐射电路[7],设计出一种保护门电路,如图5所示。图中Delay电路的加入,使得保护门起到了滤波的作用,提高了电路抗SET效应的能力,但降低了工作频率。而Al Tarawneh等人也验证了C元素能使电路获得较好的抗单粒子效应的能力[8]。

图3 DICE结构输出受单粒子扰动仿真波形

图5 保护门电路

采用C单元优化后的触发器结构如图6所示。在优化后的触发器结构中,我们在第一级的输出端采用双结点结合CLK信号作为第二级的输入。而在第二级的输出采用了两个互补结点作为C单元结构的输入。并利用C单元的原理,可以滤除单粒子效应产生的扰动输出至Q端口,从而对下一级输入信号产生影响。

对优化后的结构,我们同样采用单粒子效应电流双指数模型结合中芯国际0.13 μm体硅CMOS器件模型参数进行仿真。仿真结构如图7所示。

图6 采用C单元优化后的触发器结构

图7 优化结构输出受单粒子扰动仿真波形

将图3和图7的仿真结果进行比较,可以得出:图3所示的DICE结构的仿真结果会将X结点上的单粒子效应扰动输出至下一逻辑。在低压、高频的超深亚微米电路时代,该点的单粒子效应扰动必然会对电路的可靠性产生影响。而采用C单元优化后的触发器结构,将单粒子效应产生的扰动屏蔽,对下一级的输入信号不会产生干扰,在满足电路抗单粒子效应的同时,也提高了电路的可靠性,使得触发器抗辐射效应的能力较之前的DICE结构有所提升,满足了超深亚微米抗辐射电路设计的需要。

4 抗辐射触发器的版图设计

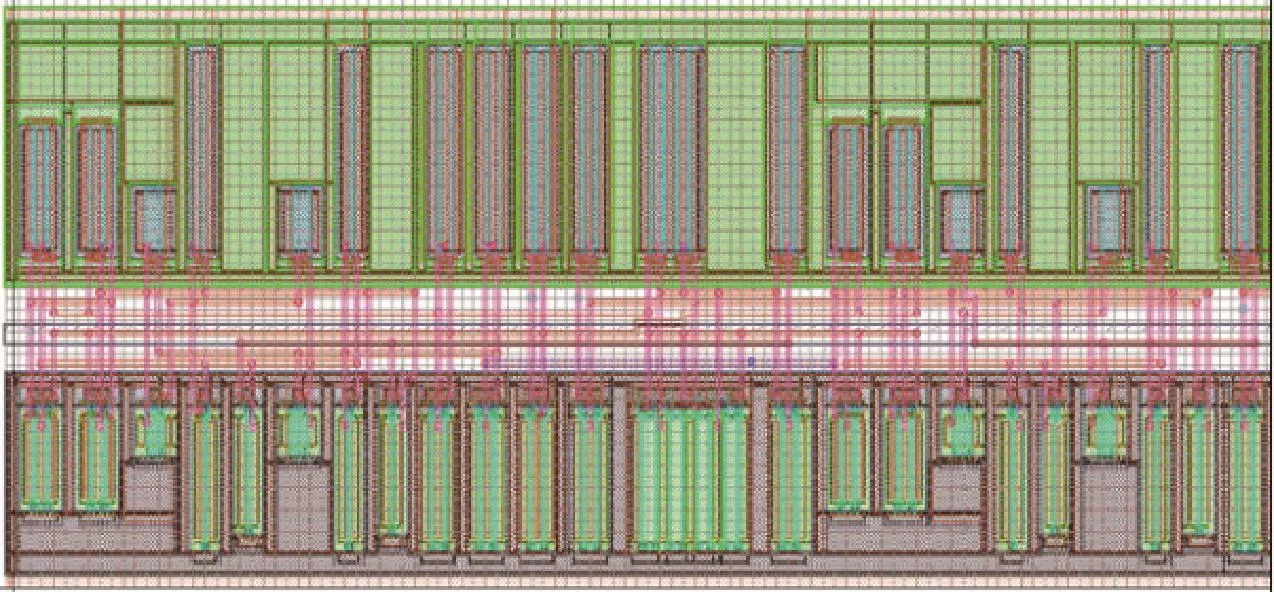

此次设计的抗辐射触发器版图结构如图8所示。在版图设计时,我们考虑了抗总剂量效应辐射及抗单粒子效应辐射加固方案。

图8 抗辐射触发器版图设计

对于总剂量效应加固,我们采用具有自主知识产权的大头条型MOS器件结构,消除了器件内源/漏端的漏电通路。同时,在器件的外围采用了保护环结构,消除了器件与器件之间的漏电通路。对于单粒子效应加固,我们采用的方案是将互补的敏感结点在版图上进行物理隔离,并分开较大的距离。同时在尺寸较大的MOS画法上,采用多管组合的版图画法,保持器件驱动能力的同时分散器件的敏感点,从而达到抗单粒子效应的目的。

5 小结

本文首先分析了在大尺寸工艺条件下采用DICE结构触发器用于高频、低电压的超深亚微米抗辐射电路时会遇到的问题。由于工作电压降低、结点寄生电容减小、工作频率增加,单粒子效应对触发器输出结点的扰动会转化为一定脉宽的扰动,传输给下一逻辑的输入,从而对电路的可靠性产生影响。

而采用C单元优化后的触发器结构,将单粒子效应产生的扰动屏蔽,对下一级的输入信号不会产生干扰,在满足电路抗单粒子效应的同时,也提高了电路的可靠性。使得触发器抗辐射效应的能力较之前的DICE结构有所提升,满足了超深亚微米抗辐射电路设计的需要。经过此次对触发器的优化设计,为今后超深亚微米抗辐射电路的设计提供了借鉴。

参考文献:

[1] Ronald C Lacoe. Improving Integrated Circuit Performance Through the Application of Hardness-by-Design Methodology [J]. IEEE Trans. Nucl. Sci., 2008,55 (4):1903-1925.

[2] N S Sake, M G Ancona, J A Modolo. Generation of Interface States by Ionizing Radiation in Very Thin MOS Oxides [J]. IEEE Trans Nucl Sci,1986, 33 (6):1185-1190.

[3] R Ramanarayanan, V D egalahal, N Vijaykrishnan, M J Irwin, D Duarte. Analysis of Soft Error Rate in Flip-Flops and Scannable Latches [J]. 2003.

[4] N Seifert, Xiaowei Zhu, D Moyer, R Mueller, R Hokinson, N Leland, M Shade, Massengill. Frequency Dependence of Soft Error Rates of Sub-Miron CMOS Technologies [J]. IEDM Technical Digest, International Electron Devices Meeting. 2001.

[5] T Calin, M Nicolaidis, R Velazco. Upset Hardened Memory Design for Submicron CMOS Technology[J]. IEEE Trans Nucl Sci, 1996, 43 (6):2874-2878.

[6] D Muller, W Bartky. A Theory of Asynchronous Circuits[C]. Proceedings of International Symposium on the Theory of Switching, 1959. 204-243.

[7] P Mongkolkachit, B Bhuva, Y Boulghassoul, J Rowe, L Massengill. Mitigation of Single-Event Transients in CMOS Digital Circuits[C]. Proceedings of Radiation and its Effects on Components and Systems, Noordwijk, Netherlands, 2003. 335-340.

[8] Z Al Tarawneh, G Russell, A Yakovlev. An Analysis of SEU Robustness of C-Element Structures Implemented in Bulk CMOS and SOI Technologies [C]. 22ndInternational Conference on Microelectronics, 2010.

Improved Design of Radiation-Hardened Flip Flop in 0.13 μm Technology

LI Xiaorong, ZHOU Xinjie

(China Electronics Technology Group Corporation No.58 Research Institute, Wuxi 214035, China )

Abstract:As the line width of CMOS technology is decreased, the density is increased; the influence of single event effect which the circuits suffered is more and more serious. The DICE fl ip-fl op which usually use in big line width of CMOS technology will transfer a few pulse width disturbance to the next logic when suffered the single event effect. It will influence the reliability of circuits. For eliminating above phenomenon, we optimized the export using C-cell, and we substituted two complementary nodes as C-cell’s input signal for a node export, original. We validate the new structure using a way of simulation analysis, and proved the new structure have a good ability for radiation hardening. And we improved the layout design way for enhancing the ant-radiation ability of fl ip-fl op. Though this improved design of fl ip-fl op, it supplies a well base for the design of radiation hardened circuits in future.

Keywords:radiation effect; radiation hardened design; fl ip-fl op

中图分类号:TN303

文献标识码:A

文章编号:1681-1070(2015)10-0026-04

收稿日期:2015-6-4

作者简介:

李晓蓉(1987—),女,江苏张家港人,本科,电子科学与技术专业,现从事集成电路设计工作。