一种FPGA模拟射频在ASIC原型验证系统中的应用

商 阳,王茜竹(重庆邮电大学通信与信息工程学院,重庆 400065)

一种FPGA模拟射频在ASIC原型验证系统中的应用

商 阳,王茜竹

(重庆邮电大学通信与信息工程学院,重庆 400065)

摘 要:在ASIC芯片原型验证过程中,FPGA凭借其可重复编程的特性扮演了重要角色。然而FPGA作为ASIC原型验证平台与射频进行数据交互时,因为性能较低不能匹配高带宽下的射频数据流处理流程。基于此问题,提出一种基于FPGA实现的模拟射频解决方法。首先就模拟射频的背景进行介绍,然后分析模拟射频模块的实现思路和结构,最后使用Verilog语言将它实现出来并通过VCS仿真验证。结果表明该方法控制简单、灵活可靠,可以为FPGA基带系统提供合适的数据速率。

关键词:ASIC芯片;原型验证;FPGA;射频;Verilog语言

1 引言

随着ASIC芯片的设计规模与日俱增,其功能日趋复杂,芯片的验证阶段占据了整个芯片开发的大部分时间,如何缩短验证时间变得非常重要;传统的功能验证是基于仿真软件进行的,这种验证方式在软硬件联合验证时效率极低。近年来,因FPGA的性能不断提升,功耗和成本也不断下降,使得越来越多的ASIC厂商采用FPGA来搭建ASIC设计的原型验证平台,即将RTL代码移植到FPGA上来进行芯片功能的验证。

虽然和仿真软件相比较,FPGA的硬件特性可以让设计运行在较高的频率上,但相对于ASIC而言它的频率仍然较低(一些研究资料表明,对于相同的工艺而言,ASIC的时钟频率是FPGA的5倍左右)[1],因此基于FPGA的原型验证平台与射频芯片进行数据交互时,不能匹配高带宽下的数据流处理流程,造成不能完全验证ASIC设计的性能,本文就此提出一种模拟射频的解决办法,即在FPGA平台上模拟射频芯片的数据发送流程,并使FPGA基带系统的速率和模拟射频进行匹配,以此来验证各种带宽下的系统测试。

2 ASIC原型验证系统概述

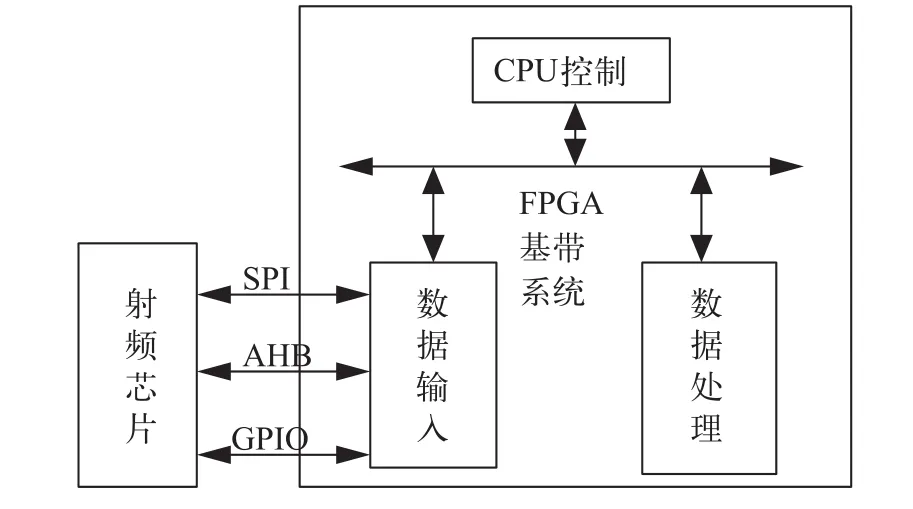

通用的ASIC原型验证平台如图1所示;将ASIC的RTL设计代码(包括ARM、 DSP等软CPU处理器)放在FPGA内,基于这种架构的ASIC原型验证平台,外接的射频芯片发送的IQ数据速率较高,而FPGA的处理主频较低,这种射频与基带系统的IQ数据速率不一致,给系统测试带来了一定麻烦。

图1 通用ASIC原型验证平台

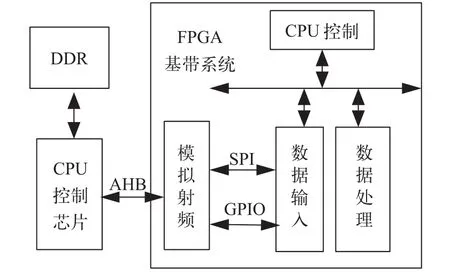

为了解决上述数据速率的匹配问题,本文提出了一种基于模拟射频的ASIC验证平台的解决方法,如图2所示;在通用ASIC原型验证平台的基础上增加了一个模拟射频模块、外接一个CPU控制芯片和DDR存储器。它的作用如下:在FPGA基带系统CPU控制单元的作用下,GPIO和SPI总线完成模拟射频模块的参数配置;外接CPU控制芯片作用下,AHB总线将DDR存储的IQ数据搬移至模拟射频模块,然后通过模拟射频模块按比率降速将IQ数据发送给基带系统,以此来避免上述数据速率的不匹配问题。

图2 基于模拟射频的ASIC验证平台

3 模拟射频的IP设计实现

3.1结构说明

本文模块设计框图如图3所示,它由3部分组成,分别是接口模块、存储器模块、控制模块。各个模块的功能如下。

图3 模块设计框图

(1)接口模块:此模块实现与SPI总线和AHB总线的交互功能,SPI接口支持DigRF SPI和Motorola SPI协议[2];通过此模块,FPGA基带系统通过SPI总线实现对寄存器的读写访问操作, 通过AHB总线实现对存储器的读写访问操作[3]。

(2)存储器模块:包括4块双端口30720x24bit(半帧LTE数据长度的十分之一[4],大小可根据实际测试场景的需求修改)存储器;端口A作AHB总线读写数据使用,端口B作控制模块读数据使用。

(3)控制模块:整个模块的控制中心;在SPI总线配置了控制寄存器、延时寄存器、中断状态寄存器之后,完成时钟的分频降速处理、中断请求信号的产生与清除操作以及数据的接收与发送处理过程。

3.2接口时序说明

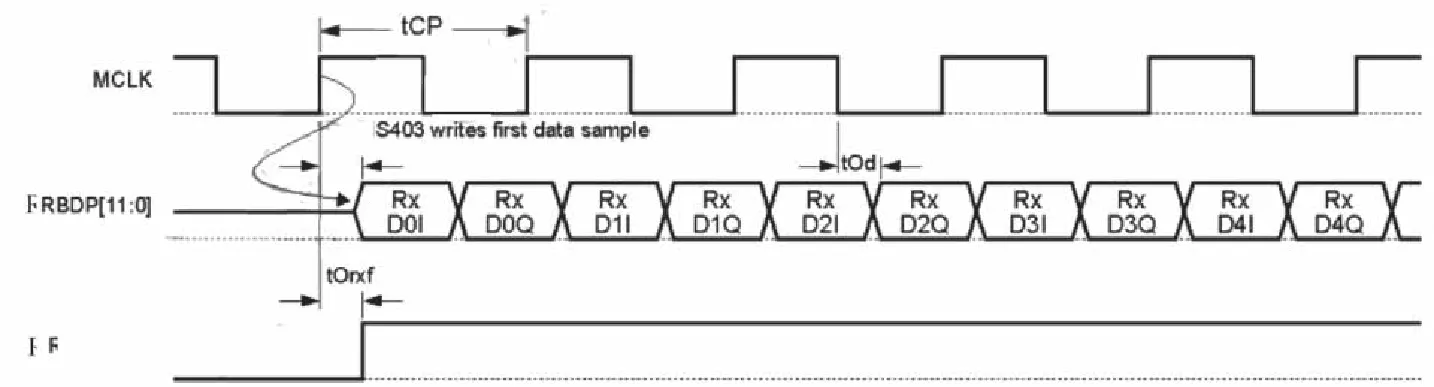

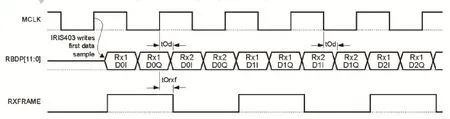

本文的模拟射频设计数据接口时序参照目前常用的数字并口射频芯片的接口时序,如ACP公司多模RFIC IRIS405[5]。其中SISO和MIMO两种模式的接口时序分别如图4和图5所示。

3.3模拟射频详细设计说明

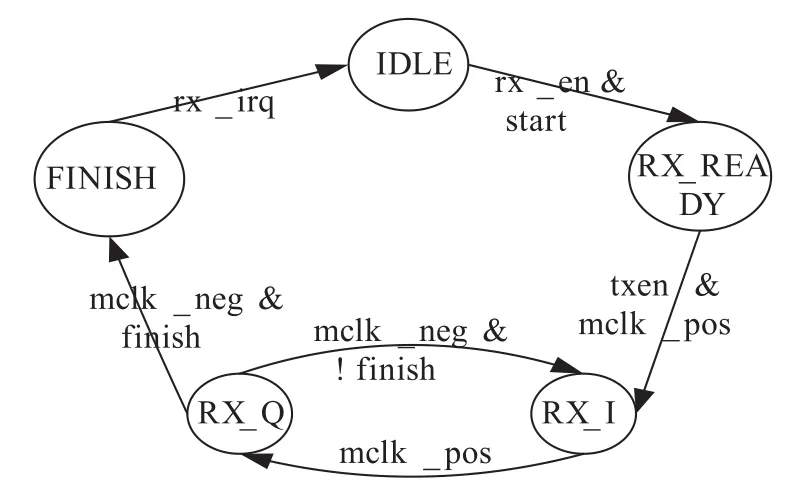

本模块的功能主要是模拟射频芯片的数据处理流程,操作过程由控制模块完成,这个控制模块主要由一个三段式状态机[6]组成。状态转移如图6所示,各状态的功能和转移条件说明如下。

(1)IDLE:空闲状态;复位有效进入此状态,完成各寄存器初始化,若启动位start和接收使能rx_en均拉高,则状态机进入下一个状态。

(2)RX_READY:准备数据状态;完成接收延时后读数使能txen有效,读数地址addrb自增,为后续发送IQ数据准备好数据doutb,同时状态机跳转至下一个状态。

图6 控制模块状态转移图

(3)RX_I:接收实部数据I(来源于doutb的部分比特),完成RXFRAME的赋值;按照图4和图5时序给RBDP和RXFRAME赋值,完成赋值之后,状态机跳转至下一个状态。

(4)RX_Q:接收虚部数据Q(来源于doutb的另一部分比特),完成addrb的自增运算;按照图4和图5时序给RBDP赋值,txen有效,则addrb自增,根据读存储器数据状态发出乒乓中断,若停止标志fi nish有效,则状态机转移至FINISH,否则跳转至RX_I。

(5)FINISH:产生结束中断信号,寄存器复位,状态机转移至IDLE。等待基带系统做出中断处理,利用SPI总线重新配置寄存器。

3.4仿真验证结果

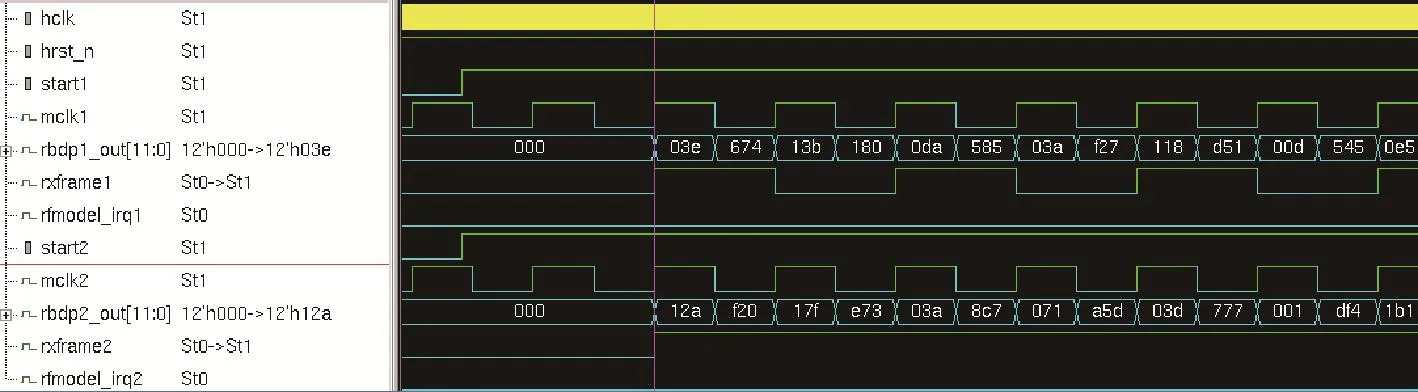

为了验证该模块工作的正确性,搭建了testbench随机测试平台并借助VCS仿真完成测试,图7和图8给出了部分仿真时序。

仿真时序图作简要说明:在图7、图8中,hclk、hrst_n为AHB总线工作时钟和复位信号,其它如SPI和AHB总线控制信号为方便查看波形没有列出。start、mclk、rbdp、rxframe、rfmodel_irq、irq_state、irq_state_w1c分别是接收使能、接收时钟、数据输出、模式标志(MIMO或SISO)、中断输出,其中1为后缀表示通道1,2为后缀表示通道2,为节约图表的篇幅,信道1工作在MIMO模式下,信道2工作在SISO模式下。由仿真时序可知本模块功能正确,方法可行。

3.5系统的优化

本文提出的基于模拟射频原型验证平台主要针对通用ASIC原型验证平台做了如下几点优化。

(1)系统验证更高效:在图2中,IQ测试数据存储于大容量DDR存储器中,外接CPU控制芯片利用AHB总线对两块存储器采用乒乓读写的方法,数据可不间断处理,提高了测试效率。

(2)系统验证更灵活:本文设计的模拟射频模块可根据测试需要灵活配置,可以模拟实际通信场景下的单信道或双信道,支持FDD_LTE/TDD_LTE/TDSCDMA模式下多天线(MIMO)或单天线(SISO)的数据处理流程,其次对AHB总线时钟采用对数分频的方式,以2~64分频使基带系统按比率降速运行来分别模拟实际通信LTE模式下20 MHz~1.4 GHz带宽、TD-SCDMA模式下的数据传输场景。

(3)系统验证更可靠:芯片RTL代码不经大幅修改即可在模拟射频平台上完成基带芯片大部分的功能验证,这在一定程度上保证了RTL移植前后功能的等价性,有助于提高原型验证系统的可靠性和流片成功率。

4 结论

图4 SISO模式下数据发送时序

图5 MIMO模式下数据发送时序

本文的创新点在于提出了一种在ASIC原型验证平台FPGA和射频芯片数据交互过程中高带宽下数据速率不一致的解决方法,使得相对于真实射频芯片下的原型验证更加可靠,虽然在一定程度上增加了RTL的编码及测试的任务量,但仍不失为一种较好的解决FPGA与射频芯片高速数据匹配问题的优选方案。

图7 20 MHz带宽下1信道MIMO 2信道SISO数据发送时序

图8 2 MHz带宽下1信道MIMO 2信道SISO数据发送时序

参考文献:

[1] 朱江,尹廷浑,乔庐峰. FPGA高手设计实战真经100则[M]. 北京:电子工业出版社, 2013.186.

[2] Digital Interface Working Group. DigRF BASEBAND/RF DIGITAL INTERFACE SPECIFICION [S]. 2004.

[3] ARM. AMBA Specifi cation (Rev 2.0) [S]. 1999.

[4] 3GPP. LTE; Revolved Universal Terrestrial Radio Access (E-UTRA); Physical Channel and Modulation (Release 10) [S]. 2011.

[5] ACP AG. Integrated Circuit Data Sheet [S]. 2013. 44.

[6] 夏宇闻. Verilog数字系统设计教程[M]. 北京:北京航空航天大学出版社, 2013.177-180.

FPGA-based Imitate RF in the Application of ASIC Prototyping System

SHANG Yang, WANG Qianzhu

(Chongqing University of Post and Telecommunication, School of Communication and Information Engineering, Chongqing 400065, China)

Abstract:In the process of verifying ASIC prototype, FPGA plays an important role due to its reprogrammable characteristics, however FPGA-based ASIC prototyping platform cannot matching the highbandwidth data processing fl ow because of its low performance, especially when FPGA interacts with RF, this paper present an FPGA-based imitate RF method to solve this problem. Firstly the paper introduced the background of imitate RF, and then it analyzed the design ideas and structure of imitate RF. Finally it was implemented by Verilog HDL and simulated through VCS, result show that the method is simple, fl exible and reliable, and can provide appropriate data rate for baseband system.

Keywords:ASIC; prototype verifi cation; FPGA; RF; Verilog HDL

中图分类号:TN492

文献标识码:A

文章编号:1681-1070(2015)10-0016-04

收稿日期:2015-5-25

作者简介:

商 阳(1989—),男,硕士研究生,主要研究方向为移动通信技术;

王茜竹(1975—),女,硕士生导师,重庆邮电大学通信与信息工程学院高级工程师,主要从事手机基带芯片算法的研究工作。