基于FPGA的射频收发前端系统设计

苟欢敏,支 敏(中国电子科技集团公司第58研究所,江苏 无锡 214035)

基于FPGA的射频收发前端系统设计

苟欢敏,支 敏

(中国电子科技集团公司第58研究所,江苏 无锡 214035)

摘 要:以Xilinx公司的V5系列FPGA芯片为研究对象,设计实现了一种基于VPX标准的6U射频收发前端信号处理系统。该系统主要由控制电路和射频电路组成,控制电路主要完成对外、对内的接口通信功能以及核心器件的控制。射频电路主要完成信号滤波、放大、正交上变频、功率放大等。设计的系统支持串行Rapid IO高速数据传输,为数据的高速交换提供了可能,满足了系统对带宽和数据处理能力的要求,经过验证系统的各项性能指标符合设计要求。

关键词:FPGA;VPX;串行Rapid IO

1 引言

随着信息技术的发展,要求信号处理系统能够高速实时、高性能、灵活地完成各种处理任务,对于信号处理系统处理器的处理能力、系统数据带宽、系统可重构能力提出了更高要求[1]。尤其是蓬勃发展的电信、航天和航空领域。传统的总线结构已不适应当前系统的要求[2],传统并行总线互连所需要引脚数较多,给器件封装、测试和焊接都带来了一些问题,也会增加在系统中应用的复杂度。随着大规模现场可编程门阵列(FPGA)被广泛应用,串行高速输入输出口(serial rapid IO,SRIO)接口被广泛应用,其具有速度快、管脚数少、系统成本低、可以实现点对点或点对多点通信等优点。本文以Xilinx公司的V5系列FPGA芯片为核心,搭建了射频收发前端信号处理系统,该系统支持串行Rapid IO高速数据传输,提高了数据交互能力。

2 SRIO简介

SRIO属于系统内部互连技术,适用于高性能嵌入式设备的系统内部互连,还提供了嵌入式系统开发者所需的可扩展性和效率。Rapid IO采用包交换技术,在网络处理器(network processing)、中央处理器(central processing unit)和DSP之间的通信具有高速、低延迟、稳定可靠的互连性,可行的应用包括多处理器、存储器、网络设备中的存储器映射I/O器件、存储子系统和通用计算平台的数据交互,具有广阔的应用前景。

2011年5月发布的Rapid IO V2.1规范提供了2种接口模式(1x和4x)[3],1x使用较少的逻辑资源,数据带宽也比较低;4x需要更多的逻辑资源,但是提供了更高的带宽和更好的可靠性。时钟采用内部的差分时钟,支持的波特率[4]分别有1.25、2.5、3.125和5 Gboud,满足不同的应用需求,还支持多种事物类型,包括读/写非共享寄存器、流写、维护、门铃和信箱服务等。

3 射频收发前端信号处理系统设计

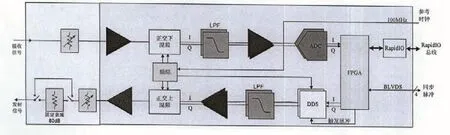

3.1整体方案

射频收发前端信号处理系统由接收通道、发射通道、频综模块和控制模块组成。控制模块完成整个发射通道和接收通道的控制工作,其基本组成框图如图1所示。

图1 原理框图

3.2系统设计

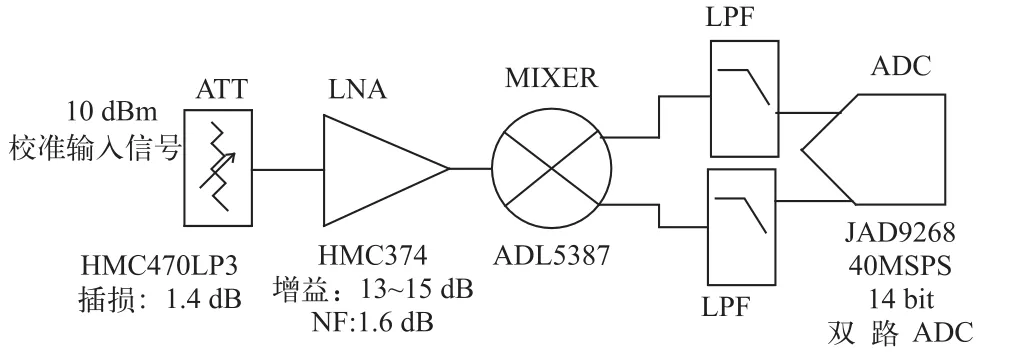

3.2.1 接收通道设计

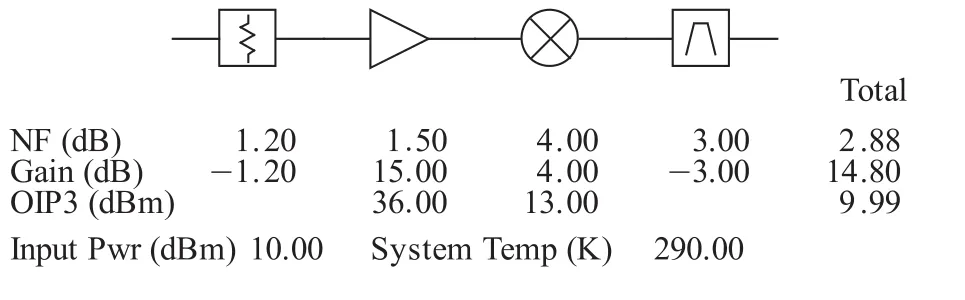

接收通道主要完成信号放大、正交下变频及滤波放大,最终得到基带信号,并送入AD进行数字化处理。接收通道原理框图见图2。

图2 接收通道原理框图

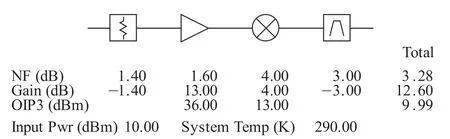

噪声系数、衰减控制、模数转换是整个接收通道的重要设计指标。为了保证通道良好的噪声系数,系统选择HITTITE公司的HMC470LP3数控衰减器,该芯片插损小,在DC~2 GHz频段内的插损小于1.4 dB;低噪放选取的是HITTITE公司的HMC374,该芯片工作在0.5 GHz~2 GHz频段内,可以提供13~15 dB的增益,并确保噪声系数小于1.6 dB。具体的增益分配和噪声系数见图3和图4。

由图3和图4得出,接收通道工作在0.5 GHz时的噪声系数最优为2.88 dB,工作在2 GHz的噪声系数最差为3.28 dB,因此满足频段内<4 dB的要求。

在接收通道的末级,我们选取模数转换器AD9268,将混频器输出的I/Q正交信号进行数字量化,并最终送给FPGA进行计算。AD9268是一款+1.8 V单片单电源工作、提供两路16位并行输出、采样率高达125 MSPS的模数转换器,完全能满足系统要求。

图3 接收通道工作在2 GHz时的链路增益和噪声系数

图4 接收通道工作在0.5 GHz时的链路增益和噪声系数

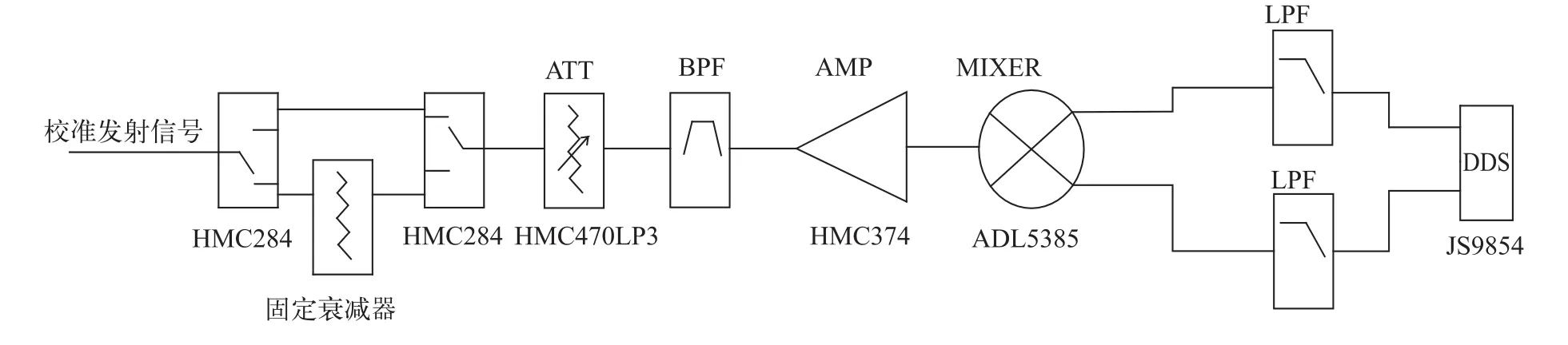

3.2.2 发射通道设计

发射通道的原理框图见图5。

发射通道主要完成本振信号与DDS信号混频,并将混频后的基带信号通过滤波、放大、正交上变频、功率放大及衰减后输出发射信号。发射通道的关键设计指标有输出功率、通道衰减、输出杂波抑制、输出谐波抑制。

系统选取中国电科58所生产的JS9854,该芯片内部工作时钟频率可达300 MHz;内部含两路12 bit D/A转换器,I路、Q路输出相位误差优于1°;器件输出10 MHz模拟信号时,SFDR高达83 dBc,可以满足设计要求。

图5 发射通道原理框图B

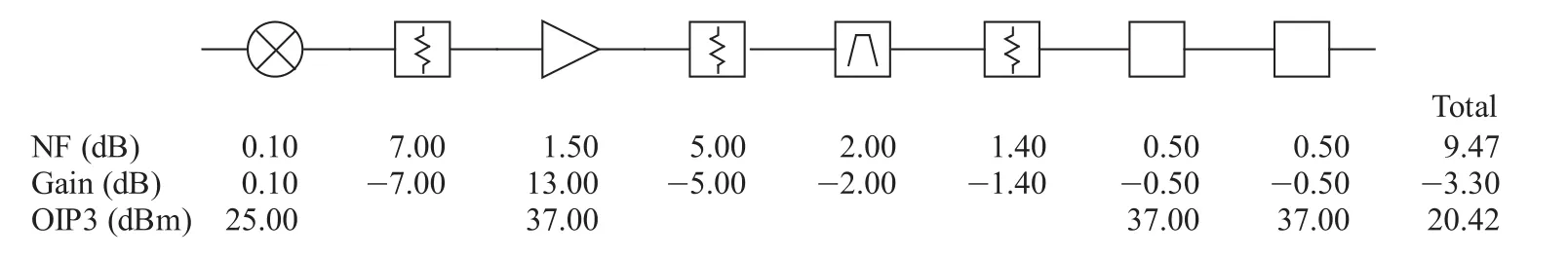

发射通道的输出功率主要由IQ混频器的输出功率和发射通道的链路增益决定。DDS的输出信号幅度最大500 mV,满足IQ上变频器的输入信号幅度要求,IQ调制器的输出功率在4 dBm左右,发射通道的固定增益见图6。由图6可知,发射通道在混频器之后的总增益为-3.4 dB,结合正交混频器的输出功率在4 dBm左右,从而使最终的输出功率控制在0 dBm。

图6 发射通道增益分配图

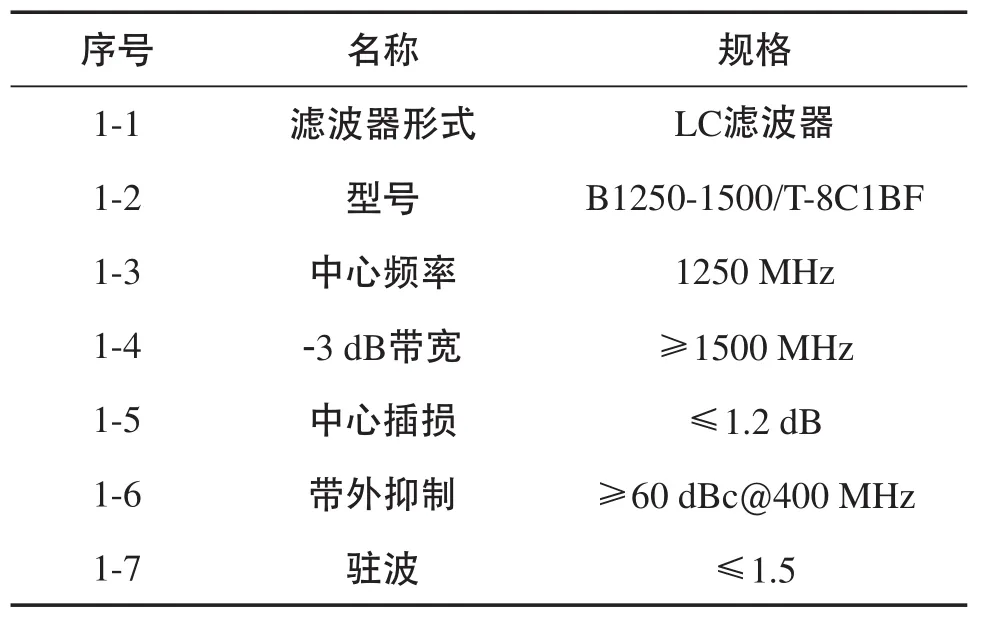

为了保证发射通道输出信号对谐波和杂波的抑制度要求,系统在放大器的后级加一个带通滤波器,以滤除输出信号可能的杂波和谐波。选取的滤波器指标如表1所示。

表1 带通滤波器技术指标

由表1可以看出,该滤波器可以满足系统指标要求。

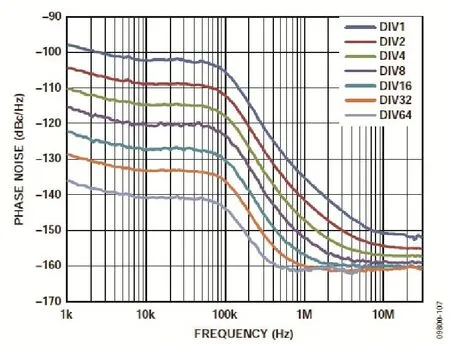

为了保证本振信号输出频率范围为0.5 GHz~2 GHz,步进10 MHz。在偏离载波1 kHz处的相位噪声要求小于-80 dBc/Hz@1 kHz。我们选取AD公司的频率综合器ADF4351,ADF4351结合外部环路滤波器和外部参考频率使用时,可实现小数N分频或整数N分频锁相环(PLL)频率合成器,其具有一个集成电压控制振荡器(VCO),基波输出频率范围为2200 MHz~4400 MHz。此外,利用1/2/4/8/16/32/64分频电路,用户可以产生低至35 MHz的RF输出频率,完全能满足系统需求。AD4351在VCO振荡在2.2 GHz时的相位噪声性能见图7。

图7 VCO=2.2 GHz时的闭环相位噪声

3.2.3 控制模块设计

3.2.3.1 控制器设计

控制模块为整个射频前端收发系统的关键部分,模块以FPGA为核心,主要完成:

(1)控制Rapid IO接口实现与外界通信,实现Rapid IO通信协议;(2)控制ADC完成对接收通道校准信号的采集控制和处理;(3)将ADC采集的数据通过Rapid IO总线输出;(4)控制DDS产生指定频率的基带校准信号;(5)控制频率综合器产生需要的本振信号。

基于以上功能,我们优先选取XILINX公司V5系列的XC5VSX95T为核心芯片,主要原因如下:

(1)XC5VSX95T的内部逻辑和乘法器资源较为丰富,更易于逻辑编程实现;(2)与XC5VSX95T器件封装相同FPGA型号更为丰富,LX50T、SX50T、LX85T、FX70T、FX100T、LX110T和LX155T;先通过SX95T器件进行功能性能验证,评估资源占用率后进行器件替换以降低器件成本。

3.2.3.2 Rapid IO接口设计

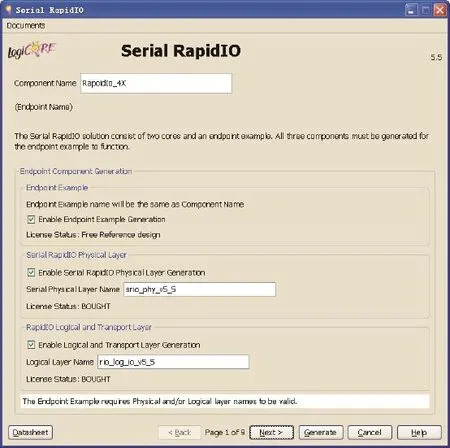

Rapid IO是针对嵌入式系统中高速互连应用而设计,是一种高性能、低引脚数、基于包交换的系统级互连协议,是专门为多种多样的嵌入式系统互连而建立的一种标准。当前方案采用Xilinx公司的ISE软件生成基于SX95T的Serial Rapid IO核,如图8所示。

图8 ISE软件生成基于SX95T的Serial Rapid IO核

Serial Rapid IO网络是系统内部数据交换的核心,利用Rapid IO网络通过VPX背板来实现与其他板卡间的数据交互。

3.2.4 抗干扰设计

系统集成了多种射频电路和数字电路,模拟电路和数字电路的交叉干扰是模块最大的风险源,必须采取措施加以防范。首先,在电路板的区域上作出明确的划分,射频模拟电路单独布置在一起,对外用地线隔离。所有的数字电路单独布置在一起,数字地与模拟地在电路板上用电感作隔离。另外,整个射频系统由VPX机箱通过背板供电,提供+12 V电压,因此模块的供电由DC-DC转换而来,开关电源的开关频率也会耦合进射频链路,必须采取一定的隔离措施。

4 系统验证

4.1Rapid IO网络测试

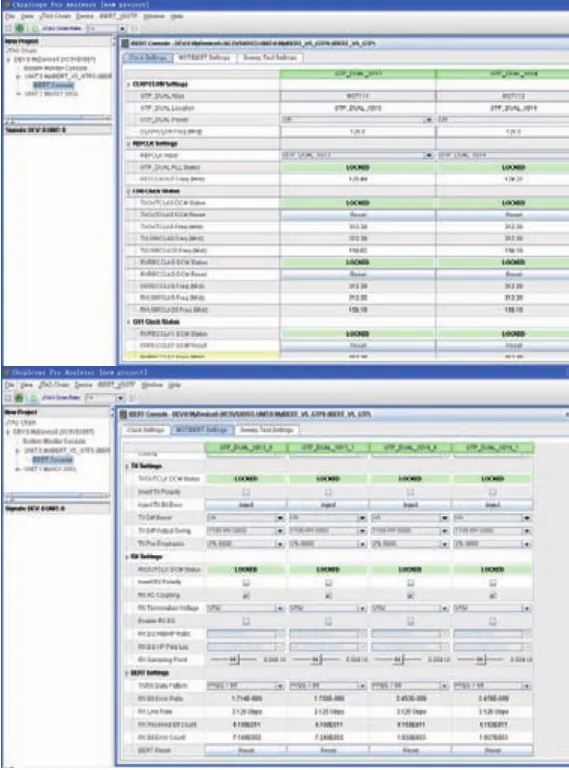

可利用XILINX自带的IBERT工具对Rapid IO接口进行闭环测试。IBERT是XILINX提供用于调试FPGA芯片内高速串行接口比特误码率性能的工具,具备实时调整高速串行接口的多种参数、与系统其他模块通信及测量多通道误比特率等功能;支持所有的高速串行标准,包括PCIE Express、Rapid IO、千兆以太网等;只需通过JTAG接口下载设计并测试硬件,无需额外的管脚和接口,大幅缩减了高速串行接口测试场景的建立和调试时间,是高速串行接口调试的理想工具。测试界面如图9所示。

图9 Rapid IO测试界面

经过测试Rapid IO的通道速率可达3.125 Gbps,比特误码率也满足要求。可见通过Rapid IO网络可以可靠地实现高速数据的交互。

4.2发射通道测试

将系统发射端接入频谱仪,对系统整个发射链路的输出功率、输出功率衰减、输出杂散等指标进行测试,均满足系统指标要求。

4.3接收通道测试

通过信号源接入系统的接收端,对系统整个发射链路的噪声系数、输入衰减等测试的指标满足设计要求。通过逻辑分析仪观察AD输出的数据,指标满足要求。

5 结束语

本射频前端收发系统集成了多种射频电路和数字电路,采用Rapid IO高速数据总线,完成指令信息的实时处理,使得板卡间的数据得以大量传输,系统设计需要具备灵活性、可拓展性、易实施性、低功耗等特点。本系统平台已经在某超宽带射频收发前端系统中得到了应用,且各项指标满足使用要求。

参考文献:

[1] 翟彦彬,蒋志焱,张保宁. 大规模Rapid IO协议交换的

A Design of RF Transceiver Front-end Signal Processing System Base on FPGA

GOU Huanmin, ZHI Min

(China Electronics Technology Group Corporation No.58 Research Institute, Wuxi 214035,China)

Abstract:Taking Virtex-5 series FPGA chips of Xilinx Company as research object, a design of 6U RF Transceiver Front-End Signal processing system base on VPX has been realized . This system is mainly consisted of control circuit and RF circuit .In which, control circuits achieved the internal and external communication interfaces function, and the control of core components, While RF circuits managed the signal filtering, amplifying and I-Q mixing functions. The design supports serial Rapid IO high-speed data transmission which makes high-speed transaction impossible, and meets the requirements in both bandwidth and signal processing ability. All the system performance is validated to be according with design requirement. Keywords: FPGA; VPX; serial rapid IO

中图分类号:TN402

文献标识码:A

文章编号:1681-1070(2015)10-0012-04

收稿日期:2015-6-12