基于FPGA的ADC自检系统

李 戈,夏 威,李 雷

(电子科技大学电子工程学院,四川成都 611731)

基于FPGA的ADC自检系统

李 戈,夏 威,李 雷

(电子科技大学电子工程学院,四川成都 611731)

在监测接收机中要实现快速的ADC(Analog-To-Digital)内核处理功能检测,针对这个问题,提出了一种基于ADC内置自测(BUILD-IN SELF-TEST)技术的ADC自检系统。该系统以现场可编程门阵列(FPGA)为核心,实现了对ADC检测的控制。经过测试,系统能够快速完成对ADC芯片内核处理功能的检测。

BIST;ADC;现场可编程门阵列;SPI;寄存器

0 引言

随着通信、计算机等技术的飞速发展和普及,数据采集系统迅速得以应用。ADC转换器是采集通道的核心,也是影响数据采集系统速率和精度的重要因素。所以对ADC内核性能的测试[1-3]就显得尤为重要。目前有很多介绍内置自测系统的著作[4-5],但还没有详细地论述ADC内置自测功能使用方法的文献。因此本文以监测接收机的模数转换器AD9265为背景,提出了基于ADC芯片内置自测功能的ADC自检系统,此检测系统适用于所有具有BIST功能的ADC,比如AD6642、AD9231等。BIST是一项用户可以调用的功能,它可以证明ADC芯片的内核处理功能符合预期。

1 ADC自检系统的FPGA实现

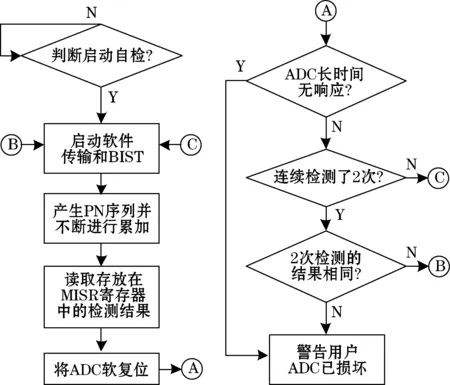

ADC自检系统FPGA实现的总体流程如图1所示。当FPGA接收到启动ADC自检的指令之后会通过SPI接口将启动指令发送给ADC,然后ADC会把一个PN序列送至转换器的数字模块并将数字模块的输出与累加器相加。累加结果包含通过数字模块的所有PN序列的和,累加器在BIST周期开始时清零。BIST检测之后的结果会被放在多输入状态寄存器(MISR)中。

FPGA会通过SPI接口读取这些寄存器中的值并对ADC进行软复位。 然后判断从寄存器中读取的检测结果是否为默认值0x00,若是默认值则说明ADC已损坏且无法正常进行自检,若不是默认值则说明ADC已正常进行了自检并将检测的结果存入了指定寄存器。最后重复上述过程并将两次读取的值相比较,对于任何给定的配置累加结果是确定的,所以两次检测的值相同的话说明ADC芯片内核处理功能正常,不相同则说明芯片内核已有损坏。

图1 ADC自检流程图

BIST测试结果以简单的“正确/不正确”方式确定器件是否在正常工作,最终的检测结果存储在ADC内部的寄存器中。由于ADC数字后端的编程选项并不唯一,因此正确响应的值也并不唯一。但是当ADC的配置确定以后就可以在正常工作的器件上读取此器件的值,这个值就是正确的响应。

ADC配置的任何改变,比如改变数据(偏置或增益等)和改变数据格式(偏移二进制或二进制补码等),都会影响最终累加结果。由于伪随机序列是可预测的,因此对于任何给定的配置累加结果是确定的。这样就能确定ADC是否在正常工作。

1.1 SPI总线及其时序

FPGA对ADC自检的控制是通过SPI端口实现的,SPI端口由3个引脚组成:串行时钟引脚(SCLK)、串行数据输入/输出引脚(SDIO)和片选引脚(CSB)[6-7]。

串行时钟引脚SCLK用来使串行接口的读写操作同步。输入数据在SCLK的上升沿有效,输出数据在下降沿有效。串行数据输入/输出引脚SDIO是双向端口,既可以输入也可以输出。引脚CSB为选通信号,低电平有效。一旦数据流开始,CSB就不能拉高直到数据流结束。

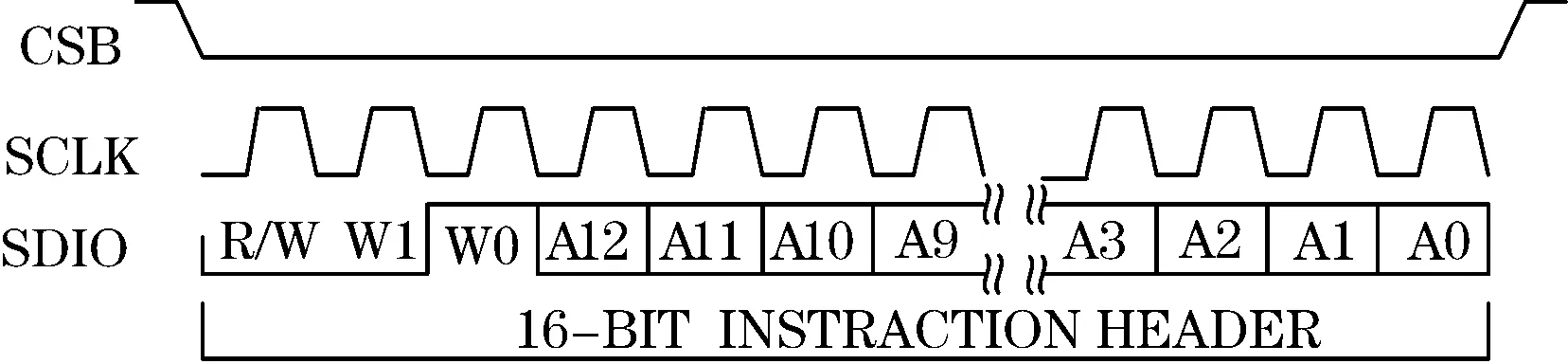

在使用SPI接口传输数据时,帧开始于CSB拉低之后SCLK的第一个上升沿。当确定了帧的开始,传输的第一阶段是指令,即传送数据时的前十六位。指令周期时序如图2所示。第一位是读/写指示位,拉高表示读指令,拉低表示写指令。W1和W0表示需要写或者读的字节数,传输的字节数为(W1:W0 + 1)。剩下的十三位指令是传输数据的首地址,如果发送的指令不止一个字节,会以顺序寻址的方式从首地址开始递增或者递减。

图2 指令周期时序

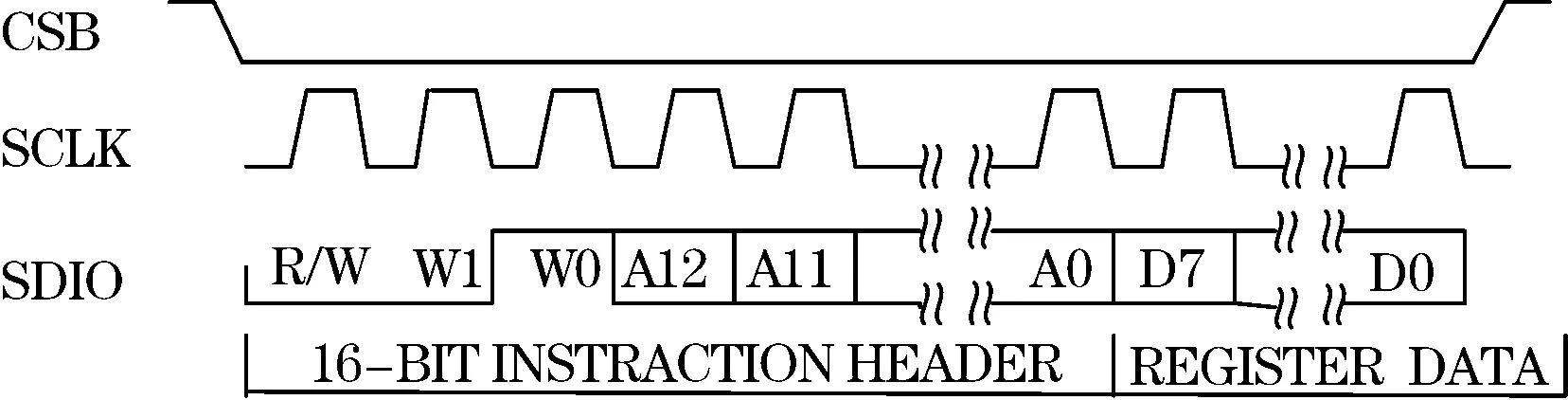

传输的第二阶段是数据,数据由多个8位组成,长度由W1和W2决定。数据周期时序如图3所示。

图3 数据周期时序

1.2 寄存器

为了对ADC进行编程,需要定义一个结构化的寄存器空间。此寄存器可以细分为许多地址,SPI数据线上进行数据传输的指令阶段中的地址即指向这些地址。寄存器分为16个地址,每个地址有8位字节,下面对BIST所用到的寄存器进行详细介绍。

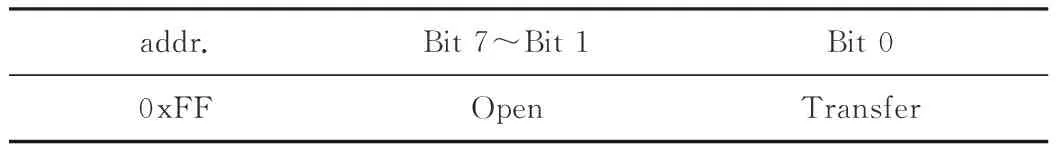

1.2.1 启动软件传输的寄存器

地址为0x0FF的寄存器用来启动软件传输。许多寄存器都需要用到主从锁存器来进行缓冲,缓冲可以增强系统的多器件同步能力,并且当其他寄存器写入的值对某寄存器的写操作有影响时,能够对被影响到的寄存器进行缓冲。SPI端口负责把信息放入寄存器,但是对于有缓冲的寄存器必须启动传输才能把主寄存器中的信息传到从寄存器。把该寄存器的第零位设置为1即可启动软件传输,当状态机识别出这一位被设置为1时,它会产生一个允许数据从主寄存器移到从寄存器的内部传送信号。寄存器的十六进制默认值为0x00。寄存器格式如表1所示。

表1 启动软件传输的寄存器格式

1.2.2 启动BIST的寄存器

地址为0x00E的寄存器用来启动内置自测(BIST)功能。把寄存器的第零位设置为1就可以启动BIST模式,此时ADC内部会产生一个伪随机序列并把输出累加在地址为0x024和0x025的寄存器中。把第二位设置为1,MISR就会在每次BIST启动之前清零,这样就可以连续地进行多次测试,并连续查看多次测试的结果而不是只能查看一次测试的结果。寄存器的十六进制默认值为0x04。寄存器格式如表2所示。

表2 启动内置自测的寄存器格式

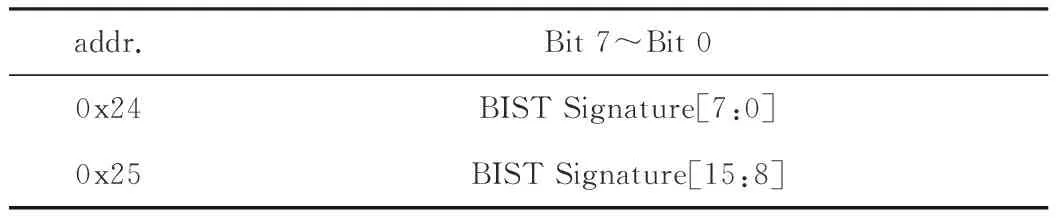

1.2.3 存储自检结果的寄存器

地址为0x024和0x025的寄存器用来存储自检的结果,它们分别为多输入状态寄存器(MISR)的低字节和高字节。该寄存器是内核MISR的镜像,与BIST功能一起使用,只能读取。寄存器的十六进制默认值为0x00。寄存器格式如表3所示。

表3 存储自检结果的寄存器格式

读取寄存器时,CSB引脚的电平值需要特别注意。如果传输数据时CSB被拉高,数据流的处理就会被终止,当CSB再次被拉低时,将开始新的指令周期。如果在流处理时CSB一直为低电平,那么第一个指令就会被不断地执行下去。这意味着一旦写(读)周期被启动,就不能再对器件进行读(写)操作。读写的首地址也会根据工作模式递增或者递减,不能改变状态机的地址。因此在对寄存器进行写操作之后想要正确地读取寄存器中存储的信息,就要将CSB拉高使状态机回到初始状态之后再进行读操作。

1.2.4 配置串行接口的寄存器

地址为0x000的寄存器用来配置串行接口。第五位能够控制软复位,默认值为0,拉高即可实现软复位,且第五位必须镜像到第二位。一旦软复位完成,该位清零。第六位决定接收或者发送数据的顺序,第六位为高则是以MSB优先的方式处理数据,为低则是以LSB优先的方式处理数据。寄存器的十六进制默认值为0x18。寄存器格式如表4所示。

表4 控制软复位的寄存器格式

1.3 ADC两种模式的切换

ADC有2种工作模式:引脚模式和SPI模式,通过控制CSB引脚的电平值可以选择两种工作模式。一般情况下,上电时只要CSB为逻辑高电平,器件便默认进入引脚控制模式。一旦CSB变为低电平,ADC即切换到SPI模式。再经过9个时钟周期(代表1个字节和1个时钟周期)后,ADC内部状态机不再检查CSB引脚的电平值并默认ADC已经切换至SPI模式。此时执行软复位功能无法使器件回归到引脚模式,唯一途径是开机重启或者利用器件的引脚复位功能。

2 测试结果及分析

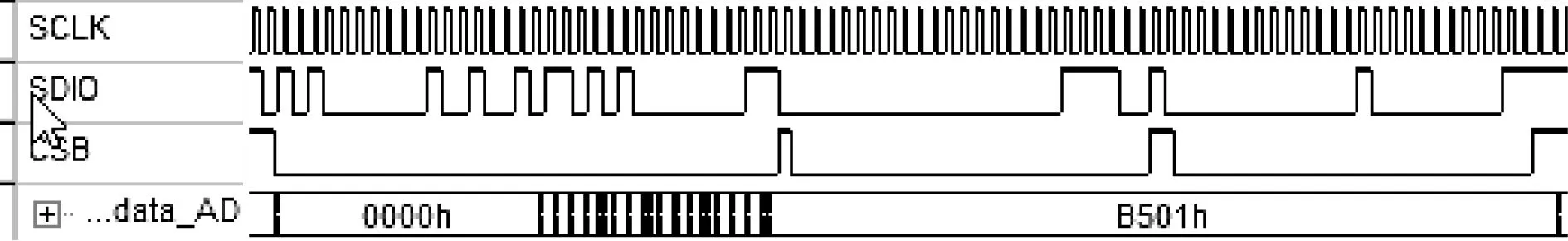

利用QuartusII软件的signaltapII功能对SDIO端口返回的数据进行采集,便可验证ADC自检功能的正确性。因为如果ADC内核正常工作,则每次启用内置自测(BIST)功能时,它都会做出同样的响应。否则,就会做出不同的响应。

图4是用signaltapII采集的第一次向ADC发送自检指令的截图。从图4可以看到通过SPI接口首先对ADC地址为0x0FF的寄存器发送了启动软件传输指令,接着又对地址为0x00E的寄存器发送了启动BIST的指令。

图4 向ADC发送启动自检指令的截图

图5是用signaltapII采集的SPI返回ADC自检结果和发送第二次自检指令的截图。从图5可以看到通过SPI接口对ADC地址为0x024和0x025的寄存器发送了读寄存器的指令之后,SDIO开始返回自检的结果,其十六进制的值为B501。读取了寄存器中的值后便向地址为0x000的寄存器发送了软复位的指令。紧接着便开始发送第二次自检的指令。

图5 返回自检结果并发送软复位指令的截图

图6是用signaltapII采集的连续两次ADC自检结果的截图。从图6可以看到两次自检的结果是一样的,说明ADC处于正常工作状态。

图6 两次自检结果对比的截图

3 结束语

本文设计了一种使用ADC内置自检(BIST)功能的系统。该系统将ADC由引脚模式转换到SPI模式,通过SPI端口对ADC的寄存器进行读写,从而完成对ADC芯片内核处理功能的检测。这种方法简便且非常准确。

[1] AD9265: 16-BIT,125 MSPS/105 MSPS/80 MSPS,1.8V ANALOG-TO-DIGITAL CONVERTER:Analog Devices,Inc,2009.

[2] 徐萍.宽带数字接收机算法研究及FPGA实现:[学位论文].成都: 电子科技大学,2012.

[3] 王晓.宽带数字监测接收机算法研究及硬件实现:[学位论文].成都:电子科技大学,2011

[4] 邹小芳,许剑.便携式高速数据采集处理系统.仪表技术与传感器,2008(3): 28-29.

[5] 刘家松,刘承玺,郑晖,等.印制电路板的可测性设计问题.仪表技术与传感器,1990(3):3.

[6] AN-877 APPLICATION NOTE:Analog Devices,Inc,2007.

Design of FPGA-based ADC Self-test System

LI Ge,XIA Wei,LI Lei

(School of Electronic Engineering,UESTC,Chengdu 611731,China)

In order to realize the rapid detection of ADC (Analog-To-Digital) core processing functions in the monitoring receiver ,this paper designed and realized an ADC self-test system based on ADC’s build-in self-test functions[1-3].The system used FPGA as its core and realized the control of ADC testing. Test results show that the system can quickly complete the detection of ADC core processing functions.

BIST; ADC; FPGA; SPI;register

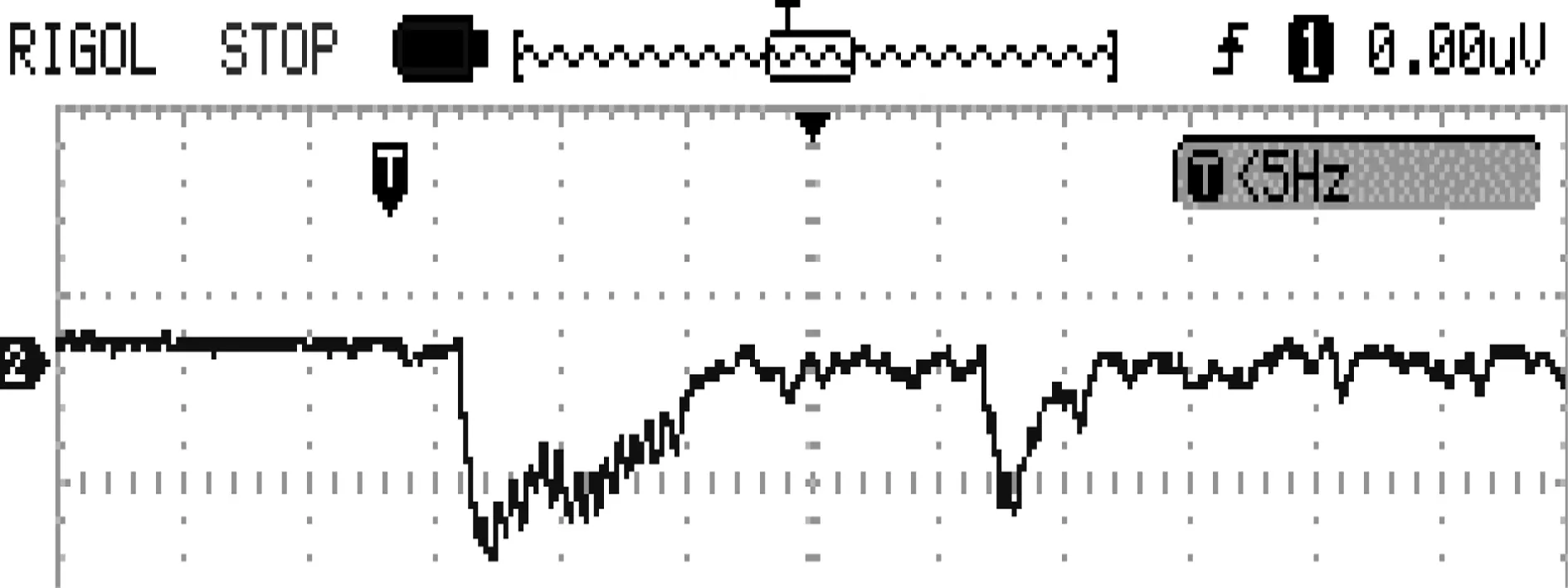

图16 电磁干扰滤波前后的波

国家自然科学基金(61101173);中央高校基本科研业务费(ZYGX2010J020)

2013-12-25 收修改稿日期:2014-10-17

TN919

A

1002-1841(2015)02-0051-03

李戈(1988—),硕士研究生,主要研究领域为雷达信号处理。E-mail:geleon@126.com 夏威(1980—),工学博士,副教授,主要研究方向:数字信号处理,自适应信号处理。E-mail:wx@uestc.edu.cn