基于CPLD硬件提升帧率的图像采集系统

朱 兵,曾延安,张南洋生,张 超,张 力

(华中科技大学光学与电子信息学院,湖北武汉 430074)

0 引言

现在主流的帧率提升手段通常是在原始视频中间插入一些通过插值算法等手段虚拟出的帧,使低帧率的视频变为高帧率的视频,这些虚拟出的帧是根据前后帧的数据进行一定插值补偿获得的[1],即这些虚拟帧的数据具有不真实性,这些不真实的图像帧对于测量等应用有可能使测量精度降低,甚至引入错误的结果。并且这些通过算法插值获得的帧率提升的图像在动态图中还存在着抖动、模糊等破坏图像质量的现象[2]。

为了解决上述的帧率提升带来的2个问题,本文设计并验证了一套利用硬件方法提升帧率的图像采集方案,这种方法实现帧率提升的本质是增加原始数据的产生速率,数据产生的速率提升后,在CCD的采集分辨率不变的情况下,将体现为帧率提升。所以这种方法可以保证图像质量不变,并且保证帧率提升后数据仍旧具有真实性。

1 帧率提升技术

1.1 帧率提升的算法

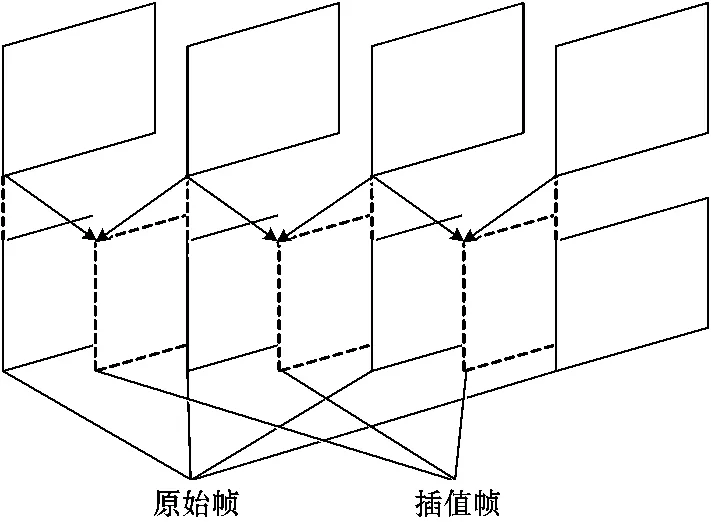

在图1中,每个实线四边形代表一帧图片,上面的视频序列为原始的低帧率的视频序列,下面的视频序列为经过算法插入虚拟帧后的的高帧率的视频序列,虚线所表示的帧是根据前后原始帧插值出来的帧。帧率提升可以分为均匀插值和非均匀插值,均匀插值是指经过帧率提升后的视频帧率为原来视频帧率的2倍,非均匀是指在经过帧率提升的视频中插值帧和原始帧满足一定的比率[3-4]。

图1 帧率提升示意图

使用算法进行帧率提升的技术多会存在一个影响视频质量比较大的问题,当视频中存在比较剧烈的运动时,使用这些技术得到的结果往往会产生比较严重的变形、模糊、抖动等问题[5-6]。

1.2 硬件帧率提升的原理

在ICX285AL图像采集芯片的典型应用中,一般能够达到15 FPS(帧/s)的帧频,此时的像素转移速度应该为28.64 MHz。要想从硬件上提升图像的帧率,就要从CCD的驱动时序上进行分析。图2、图3展示了CCD驱动信号产生的冗余数据(也称为行/帧消隐),这段时间会产生大量对实际图像数据无用的数据,并且这段时间在每帧的周期中占有比较大比例。

图2 ICX285的驱动时序行冗余数据示意图

图3 ICX285的驱动时序帧冗余数据示意图

通过硬件手段提升CCD采集器件帧率的第一种有效方法就是在CPLD产生驱动时序的时候,有目的性地压缩帧/行间的冗余信息在帧内所占比例,只留存必要的消隐时间。必要的消隐时间包括CCD垂直转移时间、CCD暗像元必须的转移时间以及CCD的帧读出转移时间等。这一方法可以将帧内冗余时间最大压缩10%左右,这也是帧率可以提高的幅度。

第二种方法是提高CCD的像素时钟。分析图4可以获得该方法的理论依据。

图4 ICX285AL的复位信号RG的波形示意图

在图4中,VRGLH和VRGLL分别是RG波形在低电平时振荡的最大值和最小值,VRGL是他们的均值:

VRGLH-VRGLL<400 mV这一限制在硬件设计上对降低噪声和抗干扰的能力提出了严格要求。

另外,VRGH是RG信号高电平的典型值,VRGL是低电平的典型值。

VφRG的取值范围在3.0~5.5 V之间,在提供各驱动信号时,不仅要满足驱动信号的电平取值范围和稳定性,还应该提供充足的功率。

从时序上分析,图4中 tr、tf和 twl的典型值为 2 ns、2 ns和24 ns,而twh最小值为4 ns。那么RG信号在一般应用中周期应大于32 ns,转换成像素时钟约30 MHz。tr、tf和 twl其实还保留了比较充分的时序裕量,在时序发生器能保证良好的开关性能(比如ns级的开关时间)时,可以考虑对这几个时间进行压缩,最终体现在驱动信号的周期被压缩上,通过这一分析,假如将ICX285AL的像素时钟从28.64 MHz提高到45 MHz,就可以将系统帧率提高57%左右。

假如第一种方法压缩的冗余时间占一帧的周期的比例为p%,第二种方法将像素时钟提升了q%,那么总的帧率提升幅度则达到:

综合以上两种方法,可以用硬件的方法将系统的输出帧率最大提升72%左右,达到25 FPS。

2 系统方案设计

在各种研究论文中已经报道过多种多样的图像采集方案,有利用FPGA(可编程逻辑阵列)的高并行性进行实时图像采集及处理的设计方案[7-8];有利用单片机实现低成本图像采集的方案[9]。

综合这些方案的优缺点,设计中将采用低成本的EPM1270T144C3型号的CPLD作为主控核心,产生高清CCD图像采集芯片ICX285AL所需的时序驱动,并将CCD采集的信号经过放大、采样和模数转换后通过cameralink接口输出到显示设备。

本系统的设计思想是利用可编程逻辑器件的并行优势和高速开关的性能,产生CCD的驱动信号,并且在产生驱动时序的过程中对提高CCD帧率起至关重要作用的位置进行压缩等优化操作,以达到减少每帧图像周期的目的,这样就直接从硬件的层面上提高了图像的帧率。并且这一设计思想可以推广到大部分的CCD应用,而不只是ICX285AL。

在系统结构图5中,以CPLD为主控核心,主要是产生用于CCD的驱动时序信号以及产生CameraLink转换芯片DS90CR285的时序信号。

图5 整机系统结构图

为了满足使驱动信号达到图像采集芯片ICX285AL对稳定性以及功率的要求,首先需要对CPLD产生的信号进行转换,转换后的驱动信号才能提供给CCD用于电荷读出和转移。并且如果需要对帧率提升,这些驱动信号应该根据具体的需要,选择上述两种提升方法并通过式(1)计算出需要时钟频率提高的比例和对驱动信号的冗余时间进行压缩的比例。CCD在这些信号的驱动下,按像素时钟频率串行输出每个像素的模拟电平,对这些模拟信号先进行放大操作有利于接下来的采样以及模数转换处理。放大后的模拟信号会进行暗电平钳位处理,这一设计的作用是将有效数据与暗像元数据进行比较并相减,从而降低有效数据的暗电流噪声,提高图像质量。接下来对模拟电平进行相关双采样操作,相关双采样的原理是对一个像素进行2次采样,一次是在有效电平处进行,另一次是在有效像素前1/2时钟处进行,再将2次采样的电平值相减获得最佳电平,这一设计可以减少噪声干扰,提高图像质量。最后有效电平经过12位A/D转换成数字信号,并传输给CPLD。

CPLD获得按像素时钟串行输入的12 bit/像素的数据后,通过为这些数据添加行同步信号和帧同步信号,可以产生一组标准的图像输出,即像素时钟、数据、行同步和帧同步。

这一组图像信号传输给DS90CR285芯片后被转换成高速的标准CameraLink信号,并通过CameraLink接口输出到显示设备进行实时显示。方案中使用CameraLink接口是因为经过帧率提升后的视频流数据量巨大,需要一种传输带宽够大的传输方式;另外由于时钟大大提高,为了降低在传输过程中受外界干扰的影响或避免引入噪声,所选择的传输方式还需要有较强的抗干扰能力,CameraLink接口无疑满足以上两个要求,是方案中比较理想的输出接口。

3 系统测试验证

根据上一章中的系统设计方案,设计的系统实物图如图6所示。

图6 系统实拍图

为了增强图像数据的可靠性,应该降低信号的走线延时,硬件PCB每组信号的走线应尽量等长,可以将驱动信号归为一组,将A/D输出数据归为一组,将图像输出信号归为一组。每组信号间都具有一定的时序对应关系,假如时序上走线延时不等,有可能会出现时序不匹配的现象,这种情况下会影响到CCD或者是A/D的正常数据输出,使图像质量下降。

对图中的硬件设备进行测试,测试平台使用MicroEnable IV-AS1-PoCL主板,该主板可以接收标准CameraLink格式输出的图像信号进行实时显示,并且利用这块主板配套的程序可以实时测量得到硬件设备的帧率。系统测试图如图7所示。

图7中,帧率测试结果是25.053 fps,这一帧率达到了系统对提升帧率的要求,提升幅度约为67%。图像清晰且运行稳定,并未因为帧率提升而降低图像质量。测试结果表明这种使用硬件方法提升帧率的图像采集系统可行性高,稳定性好。

图7 系统帧率测试图

4 结论

在深入分析研究CCD驱动信号对帧率影响的基础上,本文提出了两种可以用硬件方式提升CCD图像帧率的方法。设计了可以利用这两种方法的系统,给出系统方案框图,解释了每个模块原理、对系统的意义以及必要性,最后搭建了系统的实物,经过测试证明系统的图像帧率确实从典型应用中的15 fps提升到了25 fps,这一结果验证了这两种硬件提升CCD帧率方法的可行性。并且这两种方法具有普适性,可以推广到相同驱动原理的大部分其他公司或者型号的CCD系统设计上。

[1]AIFONSO,BAGNI D,MOGLIA D.Motion compensated frame rate up conversion for H.264/AVC decoders.Consumer Electronics,2005(6):439-440.

[2]HENTSCHEL C.Linear and nonlinear procedure for flicker reduction.IEEE Transactions on Consumer Electronics,1987(3):192 -198.

[3]CASTGNOR,HAAVISTOP,RAMPONIG.A method for motion adaptive frame rate up - conversion.IEEE Trans.on Circuits and System Video Technology,1996,6(5):436 -446.

[4]HILMAN K,PARK H W,KIM Y.Using motion-compensated framerate conversion for the correction of 3:2 pull down artifacts in video sequences.IEEE Trans.on Circuits and System Video Technology,2000,10(2):869 -877.

[5]吴勇,郑南宁,张光烈,等.具有场帧检测的自适应帧频提升算法及VLSI实现.西安交通大学学报,2002(2):143-146.

[6]吴勇,张光烈,郑南宁,等.扫描格式转换的自适应帧频提升算法及其FPGA实现.中国工程科学,2001(4):56-62.

[7]李娟,刘艳滢.基于FPGA的图像采集模块的设计.仪表技术与传感器,2012(10):27-30.

[8]周志权,刘心成,赵占锋.基于IBIS5-B-1300的视频采集和显示系统设计.仪表技术与传感器,2010(4):52-55.

[9]董大波,王湘云,赵柏秦,等.基于单片机的低成本CMOS图像采集系统.仪表技术与传感器,2014(2):45-49.