微型系统长距离DVI信号传输的FPGA实现

赵小珍,敬 敏,杨宗阳,刘 波

(1.中航华东光电有限公司,特种显示技术国家工程实验室,安徽省现代显示技术重点实验室,安徽芜湖 241002;2.总参陆航部军事代表局驻南京地区军事代表室,江苏南京 211100;3.中国人民解放军驻电子十四所军事代表室,江苏南京 211100)

0 引言

DVI(数字视频接口)是当前数字显示领域研究和应用的热点,面向DVI接口输入、输出的视频处理技术不仅解决了显示器高分辨率、高刷新率等问题,而且提高了稳定性和显示性能,具有支持高带宽数据传输、信号无衰减、画面清晰显示等优点,它被广泛应用于航空、航天等领域。因此,面向DVI接口输入、输出的视频控制器的研究具有重要意义[1]。

然而,DVI也有一个很大的缺点,就是传输距离短。通常情况下,一般的DVI电缆只能有效传输信号5 m左右,超过5 m就会产生信号的衰减。这个缺点极大地限制了DVI接口设备的普及和应用。此外,如果采用特殊的DVI光纤电缆,虽然连接简单,但电缆造价高,线缆较粗,不太适合长距离布线。总之,传输距离短,成为制约DVI发展的因素之一。因此,如何延长DVI信号的传输长度成为一个迫在眉睫的问题。本文提出一种基于在终端设备增加软件配置的方法,来实现DVI信号的长距离传输。

1 总体方案

系统由接口电路、解码电路、电源变换电路、FPGA控制电路、解码、编码电路以及存储电路组成。接口电路主要负责用户接口信号的处理;解码电路主要负责将用户输入的DVI信号解码为TTL信号,输入给FPGA处理;编码电路是将FPGA处理的TTL信号编码为LVDS信号送入液晶屏,进行相应的显示;电源变换电路主要负责生成FPGA所需的各种电压信号以及LCD显示器所需3.3 V电压;存储电路主要负责FPGA程序代码存储。其总体方案的原理框图如图1所示。

2 FPGA实现

2.1 硬件设计

2.1.1 解码、编码芯片的选择

图1 总体方案原理框图

根据用户输入信号的制式和标准,采用SiL1161芯片[2]作为DVI输入信号解码。该芯片采用了Panel Link数字技术,支持最高分辨率UXGA(25-165 MHz)的真彩色显示(每像素24bit,16,777,216 色),且可以选择单像素或者双像素输出;其内置PLL抗抖动电路,可以允许信号差动对中1个时钟的不对称,具有同步消除抖动的功能;3.3 V内核工作电压,内置节电工作模式,可在时钟探测电路检测下自动进入低功耗待机模式;采用的可扩展CMOS结构等一系列措施保证了产品的兼容性;支持热拔插检测,外围电路简单,简化了 PC机与显示器的高速、高分辨率混合信号的接口问题,降低了成本。此外,芯片自带I2C配置模块,极大地方便了设计开发人员对芯片寄存器的参数配置和优化。液晶屏的接口为双像素的奇偶LVDS信号,选用型号为 DS90C387AVJD的芯片[3]作为 LVDS信号编码。此款芯片支持从SVGA到QXGA的分辨率,带宽可以达到5.7 Gbit/s,完全兼容 LVDS接口标准。

2.1.2 时序控制模块设计

该模块主要负责对解码的数据TTL信号、时钟信号DCLK、数据时能信号DEN、行同步信号HSY、场同步信号VSY进行数据缓存后,输出给后端处理设备。由于FPGA具有I/O接口灵活、低功耗、可编程、成本低等特点,主控芯片选用FPGA芯片XC3S400-4FGG456I,内核电压 1.2 V,拥有400 000门丰富逻辑资源,可供设计人员灵活使用。另外,程序存储器选用XCF04SVOG20C,存储容量为4 M空间,足够满足开发人员代码设计[4]。另外,数据存储器选择 E2PROM,型号为 AT24C02[5],该存储器存储容量2 K,外围电路简单,数据保留时间可达到100年,完全能够满足设计要求。

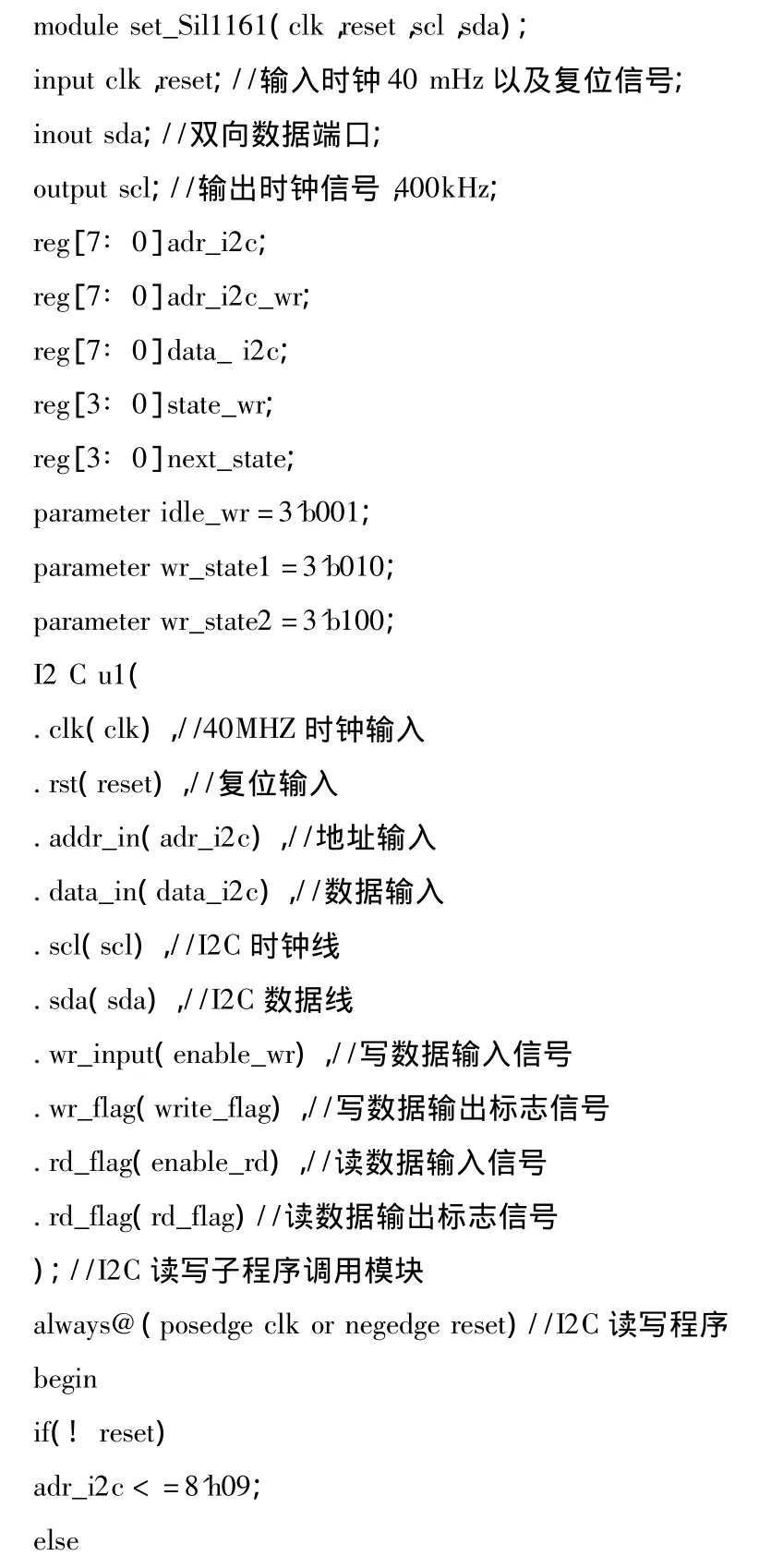

2.1.3 DVI解码控制模块设计

该模块的设计主要针对SiL1161芯片采用I2C总线对内部寄存器进行参数配置,达到预定的效果。另外,在硬件电路设计中,必须对SiL1161芯片管脚正确配置。其芯片关键引脚配置参数如表1所示。

表1 芯片关键引脚参数配置表

此外,根据相关资料及经验总结,SiL1161芯片上电复位时间至少大于10 μs,其内部上电时序图如图2(a)所示,典型的外围复位电路如图2(b)所示。

图2 复位延时及典型复位电路图

2.2 软件设计

2.2.1 寄存器配置及I2C写时序图

对SiL1161芯片内部寄存器,通过I2C总线配置,可以满足长达15 m电缆的信号传输,并且信号不失真、不衰减。SiL1161芯片内部寄存器表如表2所示。

表2 SiL1161芯片内部寄存器表

另外,I2C配置SiL1161芯片的写时序图如图3所示。

2.2.2 软件流程图及代码设计

根据I2C写时序图以及芯片内部寄存器配置说明,对芯片关键参数进行配置,其FPGA软件流程图如图4所示。

图3 I2C写时序图

图4 FPGA软件流程图

根据FPGA流程图,进行FPGA代码设计[6]。其主要功能模块代码如下:

3 结论

本文针对长距离DVI信号传输,采用内部集成均衡功能的专用解码芯片SiL1161和FPGA软件I2C配置方法,简化了硬件设计的复杂性以及节省了PCB设计成本。而且,文中从方案设计、硬件设计以及软件设计方面,详细阐述了具体实现方法。试验表明,该方案可以实现长度长达15 m标准电缆的DVI信号传输,获得信号质量无缺失、无失真的结果。此方法具有效率高、通用性好、硬件成本低、可靠性高的特点。

[1]赵小珍,刘波,朱标,等.基于FPGA多路机载冗余图像处理系统的设计与实现.现代电子技术,2013,36(23):161-164.

[2]Silicon Image.SiL1161 Panel Link Receiver Data Sheet.USA:Silicon Image,2005.

[3]National Semiconductor.DS90C387A/DS90CF388A Dual Pixel LVDS Display interface/FPD - Link.USA:National Semiconductor,2002.

[4]Xilinx.Spartan - 3 FPGA Family:Complete Data Sheet.USA:Xilinx,2005.

[5]Atmel.Two - wire Serial EEPROM.USA:Atmel,2005.

[6]杨强浩.基于EDK的FPGA嵌入式系统开发.北京:机械工业出版社,2008.