用于实时时钟的32.768kHz晶振电路Multisim13仿真实现

(上饶师范学院 物理与电子信息学院,江西 上饶334001)

石英晶体振荡器由于其Q值高,选频特性好,振荡频率稳定的特性而被各种电子电路选做时钟信号源。在数字钟中一般采用晶体振荡频率固定、温度性能完全由晶体温度性能决定的所谓简式晶振来作为晶体振荡器。此种晶振电路简单,但频率稳定度稍低[1],其32.768kHz的晶振信号再经15次分频来得到1Hz的时钟信号。而在诸多有关数字钟仿真的文献中[2-5],大多采用555多谐振荡器的振荡信号或直接使用虚拟信号发生器的脉冲信号作为时钟源,显然这与实际使用的实时时钟电路不符。而Multisim13仿真软件能够为电子电路仿真提供丰富的元器件库,有利于培养学生理论与实践相结合能力[6,7],因此本文将研究如何实现32.768kHz晶振电路在Multisim13中的仿真。

1 石英晶体

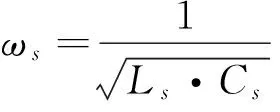

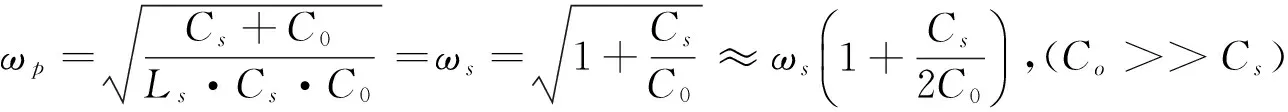

石英晶体的等效电路如图1所示。由拉普拉斯变换,该等效电路的阻抗可写成如下表达式:

(1)

或

(2)

(3)

(4)

图1石英晶体等效电路

式中s是复数频率,Ls为惯性等效电感,其大小约为毫亨到亨的数量级,Cs为弹性等效电容,其大小约为10-15~10-13法的数量级,Co为静态等效电容,其大小约为皮法的数量级 ,Rs为摩擦损耗电阻,其大小约为百欧姆的数量级。而ωs为低阻抗串联谐振角频率,ωp为高阻抗并联谐振角频率。 在晶体两端并联上额外的并联电容器会使并联后的整体共振频率降低,因此,石英晶体厂商在制作并测量石英晶体的并联谐振频率时,会在特定的并联电容值(称为负载电容)下进行测试。如使用较小的电容值,振荡频率会比标称值高,反之比标称值低。这一特性在具体电路中可以用来微调振荡频率[1]。

2 32.768kHz石英晶体在Multisim13中的spice模型数据

在Multisim13中利用主数据库(Master Database)所提供的晶体模型,理论上与其它元件一起可构成和标称频率相近的各种石英晶体振荡仿真电路。32.768kHz晶体模型在主数据库中提供了以下三种,即R145-32.768kHz,R26-32.768kHz和R38-32.768kHz。但在具体仿真过程中,我们发现无论采用哪个模型,何种电路结构都无法得到32kHz左右的振荡频率信号。人们已经在Multisim软件各个版本使用过程中发现过此软件的问题和不足[8],这使得我们怀疑Multisim各个版本主数据库中提供的32.768kHz晶体spice模型数据有误。为此,我们调出Multisim13(其他版本相同)中32.768kHz晶体spice模型数据(以R38-32.768kHz为例)如下:

** Design1 **

* NI Multisim to SPICE Netlist Export

* Generated by: Admin

*## Multisim Component X1 ##*

xX1 X1_OPEN_X1 X1_OPEN_X2 CRYSTAL_R38_32.768KHZ__CRYSTAL__1

.SUBCKT CRYSTAL_R38_32.768KHZ__CRYSTAL__1 1 2

* EWB Version 4 - CRYSTAL Model

* LS= 0.007 CS= 3.5e-015 RS= 18000 CO= 1.7e-012

LS 1 3 0.007

CS 3 4 3.5e-015

RS 4 2 18000

CO 1 2 1.7e-012

.ENDS

若将该模型数据中Ls、Cs、Co的值代入(3)(4)式进行计算可得其串联谐振频率fs为32.17MHz,而并联谐振频率fp为32.203MHz。显然与标称值相差千倍(其它两个模型与此相似)。用该模型是不可能构成振荡频率为32kHz左右的晶体振荡器。

3 Spice模型数据的修正

为使32kHz的晶体振荡器在Multisim13中仿真得以实现,首先是须修改元件库中32.768kHz晶振的spice模型数据。我们调出另一款常用的电子设计仿真软件OrCAD9.2中32.768kHz晶振的spice模型数据如下:

* 32768 hertz watch crystal, XY cut, series resonant, Q=81780

*

.subckt QZS32768 1 2fang

*

lqz 1 11 lmod 4448.72259 (=LS)

.model lmod ind(tc2 = 8.68e-8)

cs 11 12 5.30279780e-015 (=CS)

rqz 12 2 11.2k (=RS)

cp 1 2 1.84pf (=CO)

.ends

将该模型数据代入(3)(4)式计算得到fs=32785Hz,fp=32832Hz,与标称值32768Hz相近。依据这些模型参数把Multisim13元件库中32.768kHz晶体的spice模型数据修正如下:

** Design1 **

* NI Multisim to SPICE Netlist Export

* Generated by: Admin

*## Multisim Component X1 ##*

xX1 X1_OPEN_X1 X1_OPEN_X2 CRYSTAL_R38_32.768KHZ__CRYSTAL__1

.SUBCKT CRYSTAL_R38_32.768KHZ__CRYSTAL__1 1 2

* EWB Version 4 - CRYSTAL Model

* LS= 4448.7 CS= 5.3e-015 RS= 11200 CO= 1.84e-012

LS 1 3 4448.7

CS 3 4 5.3e-015

RS 4 2 11200

CO 1 2 1.84e-012

.ENDS

修正了参数的元件模型可存放在公共数据库(Corporate Database)或用户数据库(User Database)中[9],以备仿真电路调用。

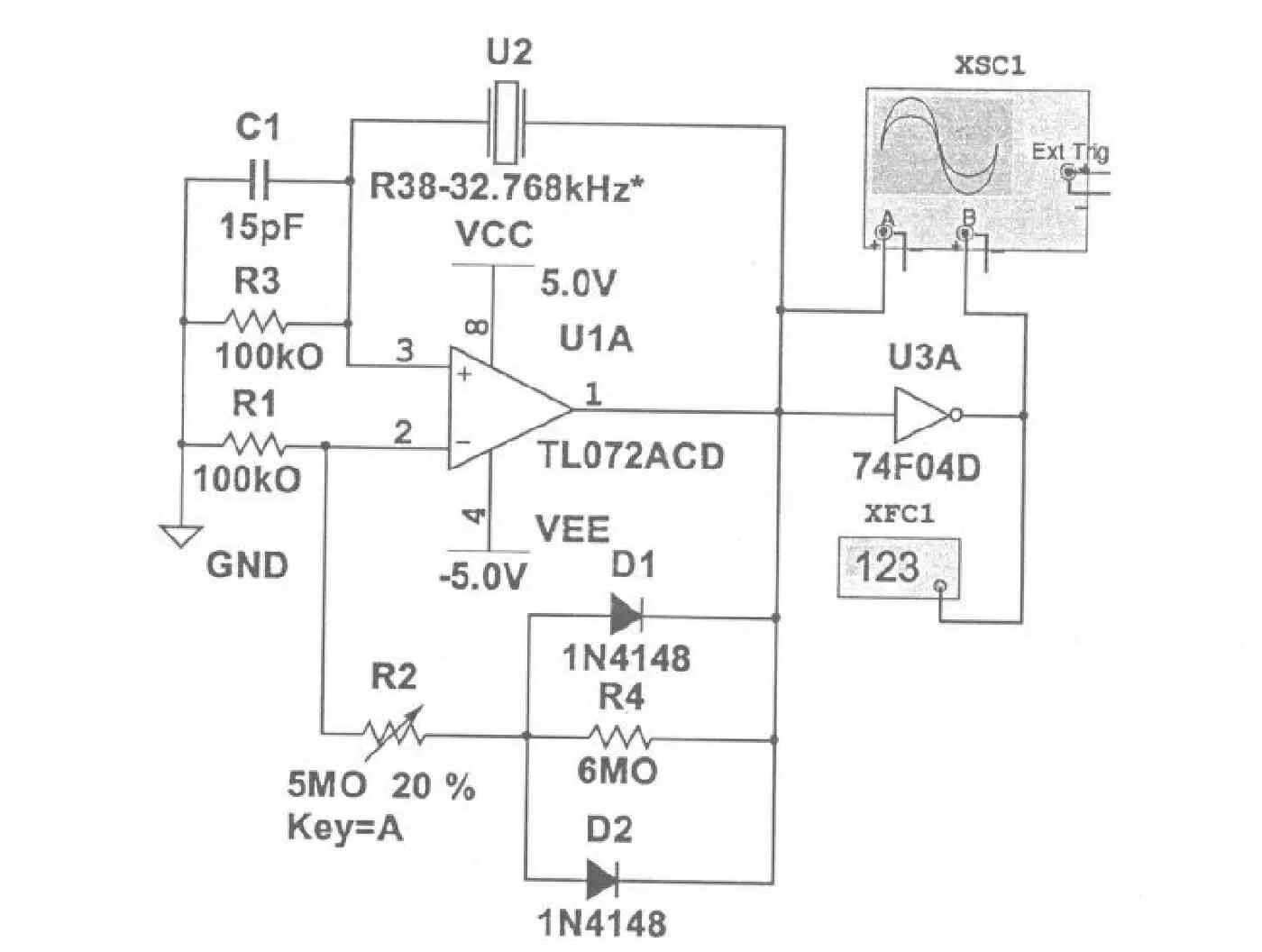

4 32.768kHz晶振仿真电路

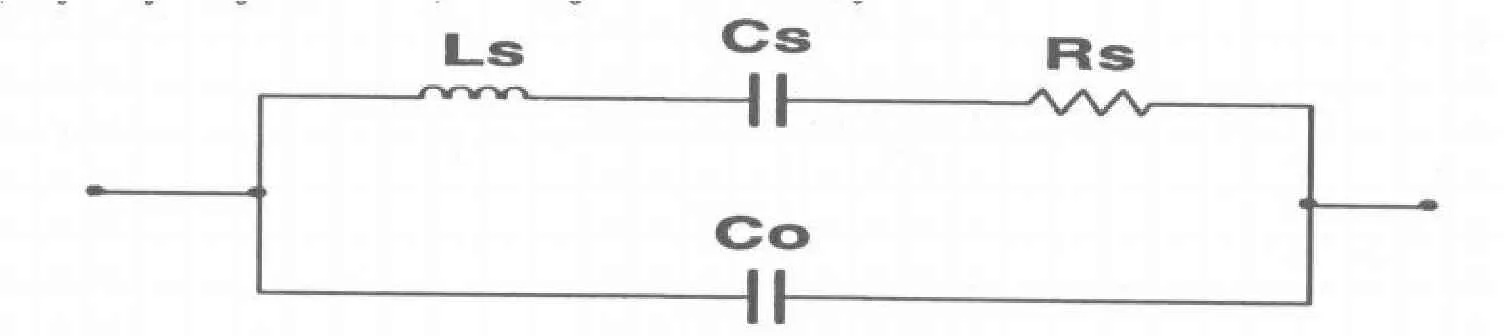

实际振荡电路中的石英晶体既可以工作在并联谐振状态,也可以工作在在串联谐振状态。工作于晶体并联谐振状态的门电路振荡器如图2所示:

图2工作于晶体并联谐振状态的门电路振荡器

图中晶体可等效为电感(晶体工作于串联谐振频率与并联谐振频率之间时呈感性),与外接的电容C1、C2构成三点式LC振荡器,通过外接的电容可对频率进行微调。电阻R1接在反相器U1A的输入与输出端,其目的是将U1A偏置在线性放大区,构成放大器[10]。在对该电路进行仿真时,我们用虚拟仪器可测到幅度为微伏数量级,频率为32kHz左右的起振信号,但该信号随振荡的持续逐渐衰减直至为零。根据这一现象可判断是仿真用放大器放大能力不足所致。为此在构建仿真电路时我们仿照RC桥式正弦波振荡器的组成,以晶体为正反馈通路(晶体工作于串联谐振状态),用JFET输入运算放大器做高增益放大器。仿真电路如图3所示。

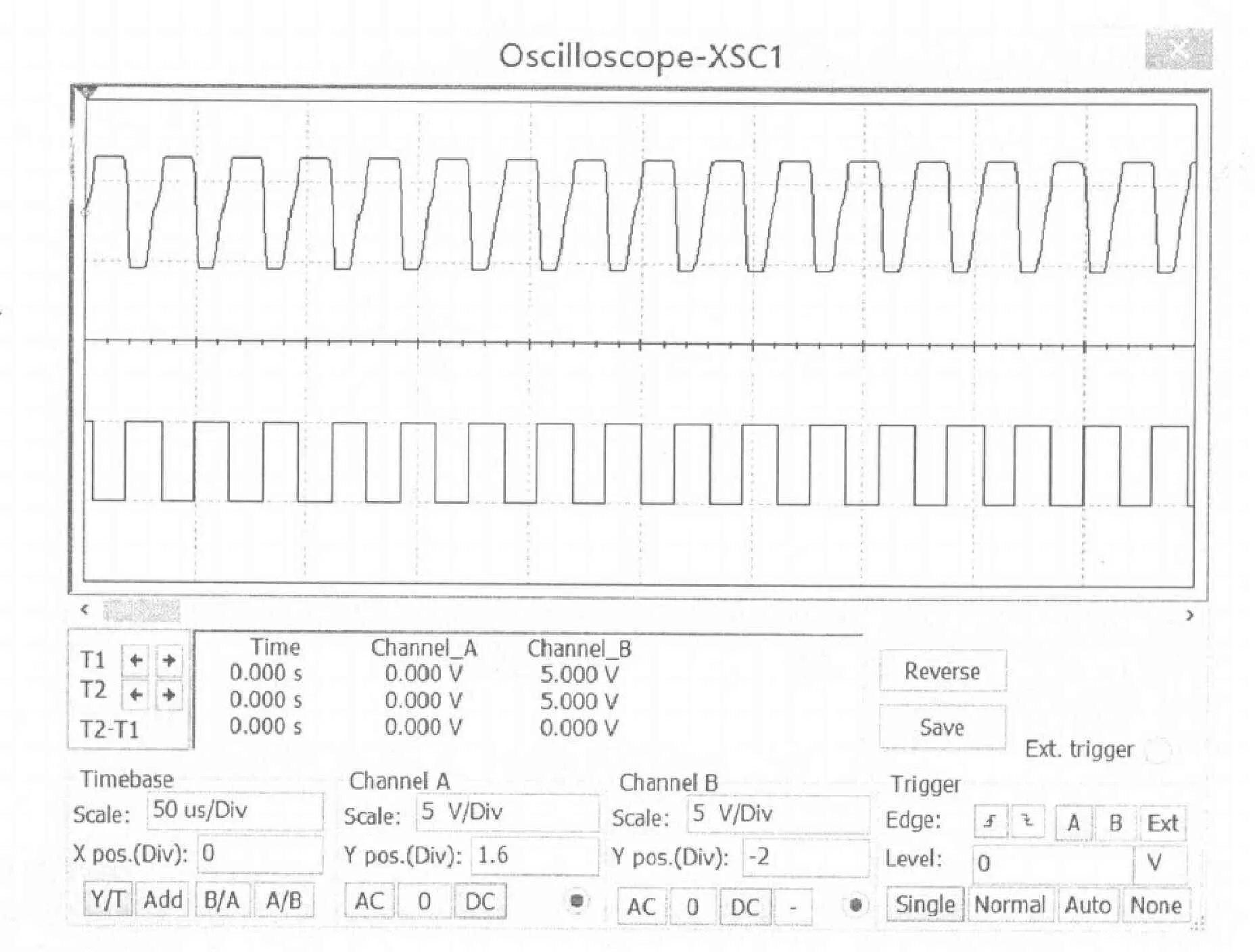

图3 晶体振荡仿真电路

图4晶体振荡电路的输出波形

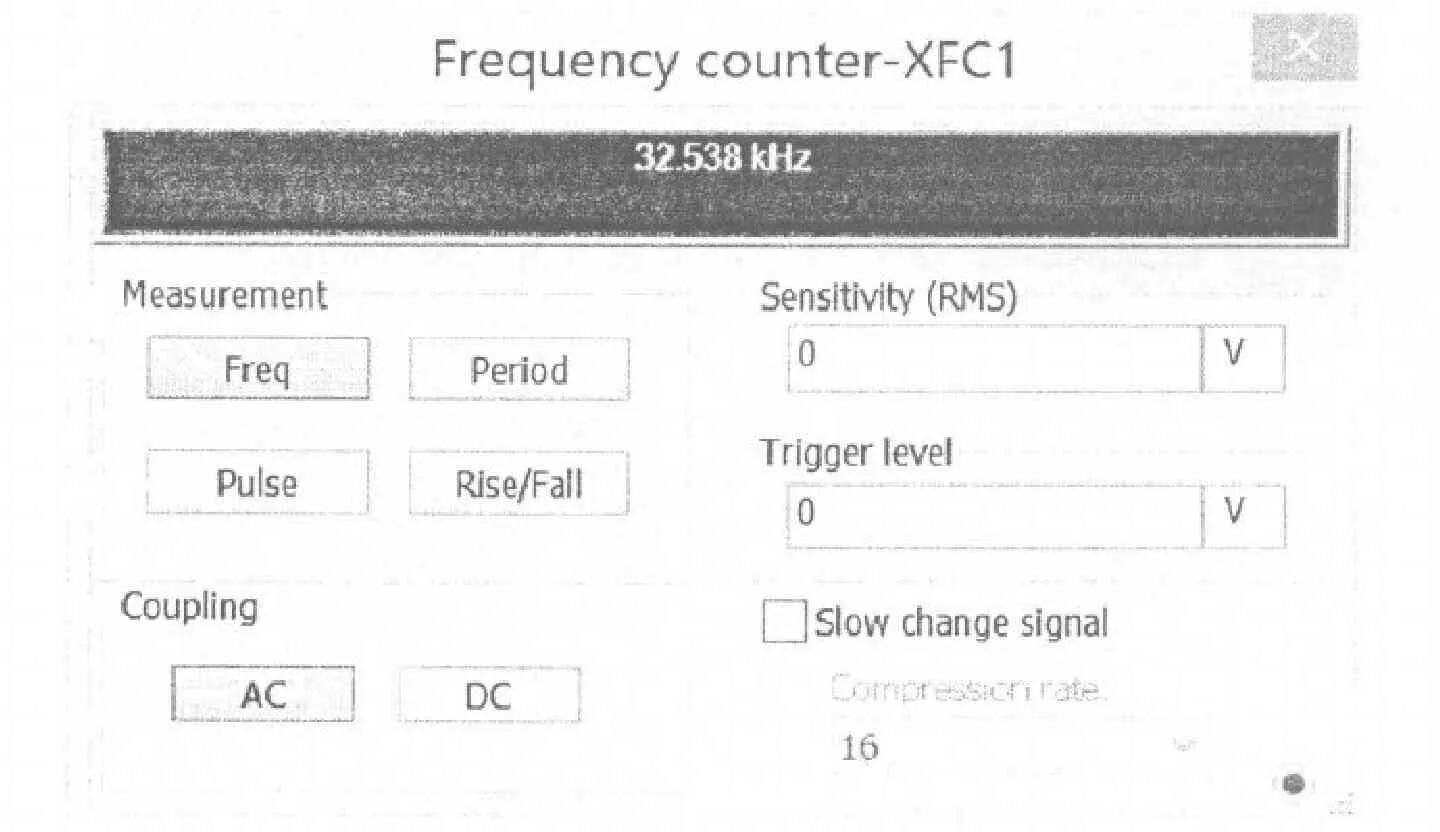

仿真时先将R2调至最大(100%),振荡稳定后再减小R2使运放输出接近于正弦波。图中C1用于消除仿真时出现的寄生振荡。电路中反相器作整形用,以便输出矩形脉冲。输出波形和频率见图4和图5。其输出频率32.615kHz已非常接近标称值,仿真效果比较理想。另外,仿真时也可以将电路中的负反馈支路(R2、R4、D1和D2)去掉,运放接成过零比较器,此时运放直接输出矩形脉冲[11]。由于spice模型中电容的容量数据很小,图3中正反馈支路的仿真起动电流也就很微弱,因而造成仿真过程从起振到输出稳定需要较长时间(与其他类型仿真电路相比)。

图5晶体振荡电路的输出频率

5 结束语

通过修正元件库中32.768kHz晶体的spice模型数据,使得在Multisim13中32.768kHz晶振电路的仿真得以实现。在对晶振电路仿真过程中有个普遍现象值得注意,即起振时间都较长。图3电路从起振到稳定输出,仿真计时通常需要0.4S左右,这与实际32.768kHz晶振电路的起振时间相仿,但会给实时仿真带来一些影响。

参考文献:

[1] 李德昌. 晶体振荡器 [J]. 国外电子测量技术, 2004,(2):19-22.

[2] 张卫丰, 王瑞春, 潘晓宁,等. 基于Multisim的数字钟电路仿真研究 [J]. 通信电源技术, 2010,27(6):28-29.

[3] 赵兵文, 毛莉萍. 基于multisim的多功能数字钟设计与仿真 [J]. 数字技术与应用, 2014,(6):135-136.

[4] 徐连成. 基于NI MULTISIM 11.0软件的数字钟设计与仿真 [J]. 电子技术, 2012,(8):60-62.

[5] 程曦. 数字钟设计与仿真——基于Multisim7仿真软件 [J]. 机电信息, 2009,246(36):114-115.

[6] 王尔申,李鹏,郑丹,等. Multisim仿真在电工及工业电子学中的应用[J]. 实验室研究与探索,2013,32(2):99-102.

[7] 熊熙烈, 涂虬. 基于Multisim12的多谐振荡器仿真研究 [J]. 上饶师范学院学报, 2013,33(6):26-30.

[8] 周宦银, 吕子勇, 马桂珍. EWB仿真软件中的几个错误 [J]. 实验技术与管理, 2007,24(2):94-96.

[9] 唐赣,吴翔,苏建峰. Multisim 10 & Ultiboard 10原理图仿真与PCB设计 [M]. 北京:电子工业出版社,2008.

[10] 杨颂华,冯毛官,孙万蓉,等. 数字电子技术基础 [M]. 西安:西安电子科技大学出版社,2009.

[11] 程雯,戎蒙恬,李萍.用于实时时钟的32.768kHz晶振电路分析与设计[J].信息技术,2009,(1):15-17,86.