基于Xilinx Vivado HLS 的小型无人机平衡仪设计

张 展,崔晋伟,陆 炯

(西安电子科技大学 电子工程学院,陕西 西安 710071)

小型无人机在航拍、灾害救援、森林防火等领域得到了广泛应用[1],但是无人机操作复杂,尤其是控制飞行姿态平稳、航线准确和降落平滑,对地面人员的操作水平要求较高。操作问题容易造成无人机的飞行事故,严重时会损坏飞机机体及机上设备,也会危害对地面人员及财产安全。因此,需要平衡仪辅助地面操作人员控制飞机的姿态和航迹。

FPGA 对数据并行处理,使用相同算法时与CPU相比,计算速度高,响应速度快,适合数据密集、重复性高的工作[2]。FPGA 在逻辑上具有高度灵活性,对各种通信协议具有良好的兼容性,也可根据各种控制系统制定数据输出格式。FPGA 架构飞控具有较大优势,但由于FPGA 设计难度较高,开发流程繁琐,开发周期长,影响FPGA 架构飞控的应用和普及。本文针对上述问题提出了一种基于Xilinx Vivado HLS 工具的FPGA 架构飞控的快速开发方法,并将该方法应用于四旋翼飞行器平衡仪的设计上。

1 平衡仪介绍

平衡仪用于提高无人机飞行的稳定性。无人机的稳定性包括横向稳定性、纵向稳定性和航向稳定性,分别表示无人机在横滚、俯仰和航向上恢复原始状态的能力[3]。通过使用平衡仪辅助地面人员操纵无人机,可精确控制无人机的飞行姿态。

本平衡仪包括惯性测量单元:使用三轴加速度计、三轴陀螺仪和三轴磁力计测量无人机物理运动状态[4];数据处理单元:平衡仪系统的核心,用来计算无人机当前姿态并控制控制机械执行结构调整无人机姿态。平衡仪结构如图1 所示。

图1 平衡仪结构图

本平衡仪算法分为姿态解算算法和控制算法。姿态解算算法用于得到当前无人机飞行姿态,当前姿态用俯仰角Pitch、横滚角Roll 和方向角Yaw 表示[5],姿态解算算法的核心为四元数法[6]。平衡仪软件流程如图2 所示,系统上电后对处理器和传感器进行初始化,计算出初始姿态角,推演出初始四元数,完成系统初始化。使用加速度计补偿陀螺仪的漂移,进行数据融合得到误差四元数,计算得到当前四元数后,计算得到当前姿态角。对遥控信号解码后可得到目标姿态角,与当前姿态角一起通过PID 算法得到控制量输出[7]。

图2 平衡仪算法流程图

2 Xilinx Vivado HLS 介绍

当今无线、医疗、军用产品和消费类产品应用中使用的高级算法比以往更加复杂,加上紧迫的开发和验证计划,即使最有经验的RTL 开发团队都感到极具挑战。Vivado Design Suite、Vivado 高层次综合可将C、C++和System C 规范直接引入Xilinx All Programmable器件,无需手动创建RTL,从而加速了IP 创建。Vivado高层次综合支持ISE 和Vivado 设计环境,使系统工程师和设计架构师能以更快速的方式创建IP[8]。

在探索了具有不同设计需求的多种微架构后,Vivado HLS(High-Level Synthesis)能直接将C、C++和System C 转换为VHDL 或Verilog 的RTL 级,从而加速了设计的实现和验证。功能仿真可以通过C 语言执行,这相比VHDL 或Verilog 仿真加速超过了一个数量级。Vivado HLS 提供给设计人员和架构师一个更快、更可靠的方法进行高品质设计[9-10]。

3 设计思路

通过上述分析,使用Xilinx Vivado HLS 套件时需要以已有C 语言实现或仿真的飞控核心代码为基础,整合为Xilinx Vivado HLS 套件所需结构,完成功能仿真后,通过高级综合工具转换为对应IP 核,在EDK 套件中配置后生成对应比特流文件。

3.1 C 语言代码调整

C 语言平台调试方便,可通过在线调试查看变量数值,对数据格式支持性好,代码编译速度较快,可使用ARM 对飞控算法框架做功能仿真。飞控框架验证合理后,需要对C 语言代码做调整,包括以下几个方面:(1)整理飞控算法的程序结构。平衡仪核心代码主要分为传感器数据的预处理、姿态角解算、控制量计算等部分。将这些功能整合到一个函数FC 中,使用统一的输入输出变量。(2)整理飞控算法的输入输出变量。根据HLS 工具对数据格式的要求,输入变量使用值传递方法,输出变量和输入输出变量使用指针传递方法。此处输入变量包括传感器数据、遥控信号值和控制参数。输出信号包括对飞机的控制信号、姿态角和一部分状态值。输入输出信号包括一些模式状态变量。(3)调整非关键信号的数据格式。目前Xilinx Zynq 系列芯片普遍有对浮点数处理的专用DSP 单元,对浮点数有良好的支持。但DSP 单元数量有限,对于对响应时间具有苛刻要求的系统中,可采用部分浮点数运算部分定点运算的方法。对于精度要求高的变量或者关键变量,如四元数,采用浮点数计算;对于对要求不高且对系统影响不大的信号,如遥控信号值,采用定点运算的方法。

3.2 HLS 使用

在HLS 中建立工程,选择正确的目标芯片,添加所有的C 语言文件,在工程的Top Function 中填写算法的顶层函数名称,本例中为FC。运行C Synthesis,调试提示的警告和错误。可通过添加Testbench 软件仿真飞控算法的C 语言程序。

例如测试姿态解算功能时,需要使用预先采样的传感器数值验证算法计算得到的姿态值是否准确、响应是否及时。建立Testbench 文件,定义预先存储的传感器实验数据和FC 函数对应的输入输出变量,在main 函数中按照传感器采样顺序和数据格式将传感器数据依次送入FC 函数,使用C Simulation 工具仿真验证实验结果。

使用C Synthesis 工具对FC 函数进行综合,综合后可查看综合报表,包括各种资源的预计使用情况。例如在设计中发现LUT 预计使用量超过实际数量或使用率过高,查看是在何处使用了大量的LUT,可试图采用模块分时复用的方法解决问题。打开此函数对应的C 文件,在Directive 栏中选择对应函数,点击右键选择Insert Directive 在弹出的对话框中Directive 项选为INLINE。也可通过输入脚本“set_directive_inline 函数名”,再次运行C 语言的综合,查看资源使用情况。

代码调试完成后使用Export RTL,选择Pcore for EDK 格式,生成飞控核心算法对应的IP 核。

3.3 EDK 配置

在EDK 中添加生成的飞控核心算法IP 核路径,并将此IP 核添加至相应的工程中。编写配置相应的输入输出IP 核,在平衡仪设计中,需要编写配置以下模块:

机械执行机构控制驱动模块:目前小型无人机电机和舵机控制多以脉宽调制信号为主,此模块功能为将飞控核心模块计算出的油门、升降、横滚和方向等控制量转换为对应的控制信号,并通过芯片管脚输出。将此模块添加至EDK 工程中后,编写对应的MPD 文件,配置对应的输入输出端口,如配置由飞控核心模块传入的信号端口为输入,宽度为32 位;输出到机械控制机构的信号端口为输出,默认为1 位。MPD 文件配置完成后在Ports 标签中将此模块的端口与飞控核心模块对应的信号连接。

遥控接收机信号解码模块:此平衡仪中使用的遥控接收机信号采用6 通道脉宽调制信号,周期约为22 ms,脉宽从1 ~2 ms 分别代表该通道信号从最小到最大的信号量。将此模块添加至EDK 工程中后,编写对应的MPD 文件,配置对应的输入输出端口,6 个通道信号定义为输入,宽度默认为1;解码后的6 路信号定义为输出,信号宽度为32。MPD 文件配置完成后在Ports 标签中将此模块的端口与飞控核心模块对应的信号连接。

传感器读写模块:此平衡仪例子中使用的传感器接口均为I2C 总线,可共用一组总线接口。此模块功能为通过I2C 总线初始化传感器并按照一定采样时间读取传感器数据。将此模块添加至EDK 工程中后,编写对应的MPD 文件,具体过程同上一模块类似。其中I2C 总线的SDA 线为输入输出类型,编写MPD 文件时注意使用输入、输出和门控的形式表示输入输出口。MPD 文件配置完成后在Ports 标签中将此模块的端口与飞控核心模块对应的信号连接。

4 实现与结果

在完成代码编写和仿真调试后,生成比特流文件。为验证此方法生成IP 核的有效性,将其应用到基于Xilinx ZynqTM-7000 扩展式处理平台(EPP)的ZedBoard 中。

为了直观比较数据准确性,添加了串口IP 核将传感器数据和解算的姿态角打印到PC 端。将传感器数据送入原始C 语言实现的核心代码中,将仿真得到的姿态角与FPGA 中计算得到的姿态角对照发现姿态角计算准确,响应较高。

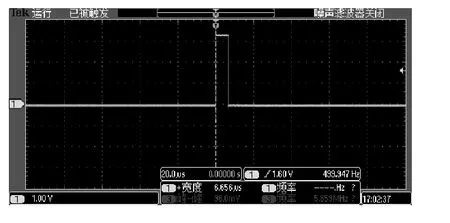

为了直观比较运算时间,配置FPGA 一个管脚输出Busy 信号表示实际运算的时间。每次运算开始时Busy 管脚置高电平,运算结束后置低电平。在ARM平台中实现的飞控系统也配置一个类似管脚用于输出飞控实际运算的时间。比较两个管脚输出信号高电平的宽度,如图3 所示,ARM 平台实现此算法需要超过1 ms的时间,而FPGA 平台实现此算法仅需约7 μs,如图4 所示,硬件加速超过了两个数量级,具有较大优势。

图3 ARM 平台运算时间

图4 FPGA 平台运算时间

为验证此方法的可靠性,将此系统应用在一个四旋翼飞行器中。经过实际飞行测试,如图5 所示,飞行器飞行稳定,适合完成多种目视范围飞行任务,该飞控系统具有较高的可靠性。

图5 实际飞行测试

5 结束语

本文介绍了一种基于FPGA 的小型无人机飞控系统的开发方法,借助Xilinx Vivado HLS 工具,将已有C语言平台的飞控核心代码转换为FPGA 平台的IP 核。此方法的特点是开发难度低、流程简便、周期短,生成的IP 核运行速度与ARM 平台相比提高了两个数量级,且精度没有降低。本文以算法较简单的平衡仪为例验证了此方法的可行性,在处理更加复杂的导航算法和控制算法时,FPGA 平台更将凸显出其处理速度快的优势,此方法可在基于FPGA 的飞控系统开发过程中得到广泛应用。在后续的改进方法中,将更加注重资源的使用情况,合理利用逻辑资源。

[1] 崔新宇.关于无人机在森林防火监测方面的探究[J].科技与创新,2014(7):128-130.

[2] 喻少林.基于DSP+FPGA 的微小型无人机飞控计算机研究[D].杭州:浙江大学,2011.

[3] 张鹏翼.红外传感器在无人机姿态平衡系统中的应用[J].电光与控制,2007,14(6):170-172.

[4] 张天光.捷联惯性导航技术[M].北京:国防工业出版社,2007.

[5] 徐玉.微小型无人机飞控平台与姿态融合算法研究[D].杭州:浙江大学,2008.

[6] 秦永元.惯性导航[M].北京:科学出版社,2006.

[7] 胡寿松.自动控制原理[M].北京:科学出版社,2001.

[8] Xilinx.Vivado design suite user guide[M].San Jose:Xilinx,2013.

[9] Xilinx.Vivado design suite tutorial[M].San Jose:Xilinx,2013.

[10]何宾.Xilinx FPGA 设计权威指南Vivado 集成设计环境[M].北京:清华大学出版社,2014.