一种积累型槽栅超势垒二极管

许 琬,张 昕,章文通,乔 明

(电子科技大学电子薄膜与集成器件国家重点实验室,成都 610054)

1 引言

二极管是最早使用和最基础的电子器件,目前商业化的功率二极管以PIN功率二极管和肖特基势垒功率二极管(Schottky Barrier Diode)为主。PIN二极管有着高耐压、大导通电流、低反向泄漏电流和低导通损耗等优点,但PIN二极管内建电势较高,约为0.7 V,电导调制效应在漂移区中产生的大量少数载流子降低了器件的关断速度,限制了二极管向高频化方向发展[1]。肖特基二极管正向开启电压小,且没有少子存储效应,开关频率高,但是反向泄漏电流大,且漂移区电阻与器件耐压成2.5次方的矛盾关系[2],阻碍其在高压大电流范围的应用[3]。

为解决此问题,已提出了沟道二极管技术[4~7],但是此技术与肖特基二极管相比优势不大。因此Vladimir Rodov等人提出了一种超势垒功率二极管[8],降低了二极管的开启电压。但是这些结构利用的是增强型的MOSFET,工作电压至少要达到MOS管的阈值电压时,器件才能开启,器件的开启电压相对较高。

本文针对传统二极管开启电压高、泄漏电流大等问题,提出了一种积累型槽栅超势垒二极管。从原理上解释器件开启电压较低的原因,用仿真软件分析不同N-宽度和浓度对开启电压和泄漏电流的影响,以及不同N型外延层浓度和厚度对开启电压和击穿电压的影响,并与PIN二极管和肖特基二极管的开启电压和泄漏电流作对比。

2 理论分析

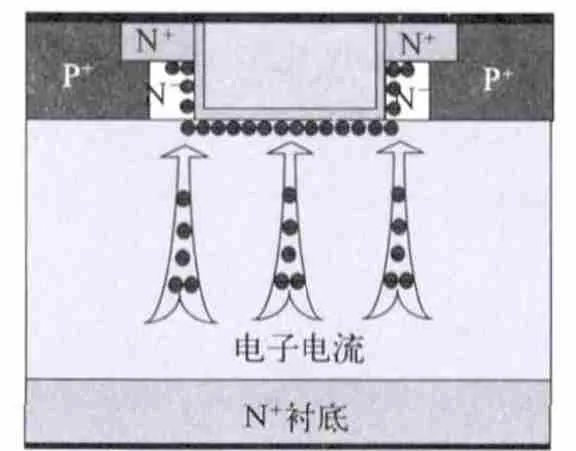

图1(a)是积累型槽栅超势垒二极管的结构示意图,相比于常规超势垒二极管,N-区为电流提供通道,沟道长度由N+区和N外延区间的N-区长度决定,易于控制。N+区、N-区、N外延区与N+衬底形成N型积累型MOSFET的电子通路。P+区与N外延区和N+衬底形成PIN二极管结构 。图1(b)是超势垒二极管的等效电路图,可等效为一个N型积累型MOSFET和PN结并联,该N型积累型MOSFET的漏极和多晶硅栅极短接,共同构成超势垒二极管的阳极,N+衬底构成超势垒二极管的阴极。N型积累型MOSFET的体区、漏极、栅极和源极分别对应于图1(a)中的P+区、N+重掺杂区、多晶硅栅和N+衬底。

积累型槽栅超势垒二极管的开启电压VF由N型积累型MOSFET的阈值电压决定。当金属阳极加很小的正压、金属阴极接地时,N+区和N外延区形成导电沟道。N型积累型MOSFET的体区接高电位,源区接低电位,体源电压VBS为正,由体效应可知,阈值电压绝对值相比于体源电压VBS为零时大,积累型沟道内的电荷变多,导通电流增加[9~11]。如图2所示,在两个N+区下方及栅氧化层底部与N外延层界面处形成电子积累的薄层,这有利于进一步降低器件的开启电压。即当正向偏置小于P+区和N+区之间的寄生PN结的势垒电压时,N型积累型MOSFET也会开启,器件处于正向导通状态,所以超势垒二极管所需的开启电压比较低。

图1 积累型槽栅超势垒二极管的结构示意与等效电路图

P+区、N外延区和N+衬底分别构成PIN二极管的P区、I区、N区,随着外加电压的增大,PIN结构中的P区与N区之间的电势大于PIN二极管的内建电势,P+区向N-外延区注入空穴,同时N-外延区向P+区注入电子,PIN二极管中有大量电流流过。N型积累型MOSFET的体效应和PIN二极管流过的大电流共同作用使得二极管正向压降大大降低。

图2 正向时积累型槽栅超势垒二极管电子电流和耗尽区示意图

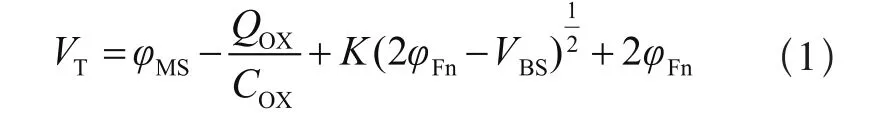

考虑到体效应后,N沟道MOSFET阈值电压为:

由式(1)可以看出,体源电压VBS越大,阈值电压VT越小。漏极电流增大,器件在更小的电压下即可开启。

当外加反向偏置时,金属阳极和阴极之间存在电势差,由P+区和N外延构成的PN结开始耗尽。P+区的掺杂浓度远大于N外延层的掺杂浓度,反偏耗尽层主要向N外延层扩展, PN结快速耗尽,承受反偏电压,积累型槽栅超势垒二极管的反向泄漏电流由PN结决定,相比于肖特基二极管,反向泄漏电流大大减小。

3 结果与讨论

采用二维器件模拟软件MEDICI进行仿真。具体器件参数为:N-区的宽度为0.12 μm,浓度为2.5×1015cm-3,深度为1.8 μm;作为欧姆接触的N+区的宽度为0.2 μm,浓度为1×1020cm-3,深度为1.8 μm;顶部P+区的宽度为0.6 μm,浓度为1×1020cm-3,深度为1.8 μm;N型外延层厚度为10,浓度为2.5×1015cm-3;N+衬底厚度为2.0 μm,浓度为1×1020cm-3;氧化层厚度为0.04 μm;槽栅宽度为0.6 μm,深度为1.96 μm;浓度为1×1022cm-3;器件宽度为2.28 μm。

开启电压VF随N-区宽度变化而变化。图3为开启电压和泄漏电流与N-区宽度和浓度的关系。在相同N-区浓度下,增加N-区宽度,开启电压降低,这是由于N-区宽度越大,沟道区域面积也越大,从而积累的电子越多,器件达到开启时所需的电压就越小。另外,从图3中可知,在相同N-区宽度下,N-区浓度越高,提供的负电荷更多,更小的电压就可以使器件获得较大的电流,因此开启电压VF更低。仿真中N-的深度和P+相同,实际中,可根据耐压和开启电压的不同要求适当调整N-的深度。

图3 开启电压和泄漏电流与N-区宽度和浓度的关系

但是,泄漏电流与N-区浓度和宽度成正比,考虑到开启电压和泄漏电流的矛盾关系,N-区宽度和浓度要折中。最佳参数如下:N-区浓度为2.5×1015cm-3,N-区的宽度为0.12 μm,N外延层浓度为2.5×1015cm-3。此参数下的开启电压约为0.22 V,泄漏电流约为1×10-12A·μm-1。

在此条件下改变N型外延层厚度和浓度,得到开启电压和击穿电压与N型外延层厚度和浓度的关系,如图4。从图4中可知,在相同N型外延层浓度下,外延层浓度越深,外延层的电阻越大,器件开启电压相对增大,由于N-区是影响击穿电压的主要因素,所以外延层厚度对击穿电压影响不大。N型外延层浓度越高,提供的电子越多,器件越易开启。积累型槽栅超势垒二极管的N型外延层承担主要耐压,外延层浓度越低,越易耗尽,导通电阻越大,器件的开启电压也越高。

图4 开启电压和击穿电压与N型外延层深度和浓度的关系

由于开启电压和击穿电压是一对矛盾关系,在设计器件时,N外延层的浓度和厚度要折中,最佳参数如下:N-区浓度为2.5×1015cm-3,N外延层浓度为2.5×1015cm-3,N-区的深度为10 μm,N-区的宽度为0.12 μm。此参数下的开启电压约为0.22 V,泄漏电流约为1×10-12A·μm-1。

图5是积累型槽栅超势垒二极管与PIN二极管和肖特基二极管在相同N外延浓度(2.5×1015cm-3)和厚度(10 μm)下正向电压的比较图。由于N-区形成积累型沟道,在外加很小的阳极电压时,器件就有很大的电流通过。从图中可以看出,积累型槽栅超势垒二极管的开启电压约为0.23 V,比肖特基二极管的开启电压降低30%,比普通PIN二极管开启电压降低65%。

图6是积累型槽栅超势垒二极管与PIN二极管和肖特基二极管在相同外延浓度(2.5×1015cm-3)和厚度(10 μm)下泄漏电流的比较。从图6中可以看出,积累型槽栅超势垒二极管、肖特基二极管和PIN二极管的击穿电压相差不大,但是泄漏电流不同,这是由于积累型槽栅超势垒二极管在反向工作时,P+区和N外延层形成的PN结承担反偏电压,所以反向泄漏电流大大减小,比肖特基二极管降低约50倍。

图5 相同N外延浓度(2.5×1015 cm-3)和厚度(10 μm)下,积累型槽栅超势垒二极管与PIN二极管和肖特基二极管正向电压比较

图6 相同外延浓度(2.5×1015 cm-3)和厚度(10 μm)下,积累型槽栅超势垒二极管与PIN二极管和肖特基二极管反向泄漏电流的比较

4 结论

本文提出了一种积累型槽栅超势垒二极管,采用N型积累型MOSFET,通过MOSFET的体效应作用降低二极管势垒。通过仿真可知,N-区宽度和浓度增加,开启电压降低,泄漏电流增大。N型外延层的厚度减薄和浓度增加,开启电压也会略微降低。另外,器件的击穿电压与N型外延层浓度成反比,与N型外延层的厚度成正比,所以在具体设计中要对各种影响因素折中考虑。本文提出的积累型槽栅超势垒二极管的开启电压仅有0.23 V左右,并且远小于肖特基二极管的泄漏电流,大大提高了器件性能。

[1] Jubadi W M, Noor S N M. Simulations of variable I-layer thickness effects on sillcon PIN diode I-V characteristics[M]. Industrial Electronics & Applications, 2010. 428-432.

[2] XingBi Chen. Optimization of the specific On-Resistance of the COOLMOS [J]. IEEE Transactions on Electron Device, 2001, 48(2).

[3] Chang H R, Gupta R N. Comparison of 1 200 V silicon carbide Schottky diodes and sillicon power diodes [J].IECEC, 2000, 1: 174-179.

[4] H P Yee, P O Lauritzen, S S Yee. Channel diode, a new power diode [C]. Proc. ISPSD, 1992. 72-79.

[5] S M Sze. Physics of Semiconductor Device [M]. New York:Wiley. 1983.

[6] Q Huang, G A J Amaratunga. MOS contronlled diode, a new power diode [J]. Solid State Electron, 1995, 38:977-980.

[7] Muck, M Becker. Use of super Schottky diodes in a cryogenic radio frequency superconduting quantum interference device readout [Z]. Digital Object Identifier,1995. 376-378.

[8] Gokirmak Ali, Tiwari, Sandip. Accumulated body ultranarrow channel sillicon transistor with extreme threshold voltage tenability [J]. Applied Physics Letters,2007, 24(91).

[9] Vladimir Rodov, Alexei L. Ankoudinov, Taufik. Super barrier Rectifier, a new generation of power diode [J]. IEEE Transactions on Industry Applications, 2008, 44(1).

[10] Baishya S, Abhijit Mallik, Sarkar C K. A threshold voltage modiel for DMG-MOS transistors taking into account the varying depth of channel depletion layers around the source and drain [J]. Industrial and Information Systems, 2007.

[11] Salcedo J A, Ortiz-Conde A. New approach for defining the threshold voltage of MOSFETs [J]. Electron Devices,2001, 48: 809-813.