基于SOI工艺集成电路ESD保护网络分析与设计

胡永强,周晓彬

(中国电子科技集团公司第58研究所,江苏 无锡 214035)

1 概述

SOI工艺采用绝缘的氧化物进行全介质隔离技术,可以彻底消除体硅工艺的闩锁效应,并具有寄生电容小、工作速度快,集成度高、抗辐照能力强等优势,因而在空间辐射环境电子系统中得到重点应用。

SOI工艺一般采用很薄的硅膜进行制备,这与体硅工艺存在很大的不同。器件下方的埋氧是热的不良导体,大约比硅小两个数量级,严重影响ESD保护器件的散热。国外曾对SOI NMOS器件和体硅NMOS器件进行过对比研究,通过特殊处理方法将两个尺寸、版图布局完全相同的SOI NMOS器件和体硅NMOS器件制备在同一硅衬底材料上,评价结果显示SOI器件对ESD的承受能力远小于体硅器件[1]。因而SOI电路的ESD保护设计已成为设计者面临的一项严重挑战。

ESD保护网络中一般将电源地供电网络的金属布线作为ESD泄放通路的总线(ESD BUS)。信号端口或其他电源地端口通过相应的ESD保护器件将ESD电流导入到ESD BUS上,将端口之间的ESD应力泄放到地。需要注意的是由于SOI材料不具备体硅材料的硅-衬底,不同电源域的地线之间也需要设计ESD泄放通路。由此可见,ESD保护设计不仅需要设计高效、稳定而且强壮的ESD保护器件,还需要构建完备的能将各端口之间ESD电流泄放的ESD网络。

本文阐述了一款基于0.5 μm部分耗尽SOI(PD SOI)工艺的数字信号处理电路(DSP)ESD设计理念和方法,并通过ESD测试、TLP分析等方法对其ESD保护网络进行分析,找出ESD网络设计的薄弱环节。通过对ESD器件与保护网络的设计优化,并经过流片验证,将电路的ESD保护能力由1 000 V(HBM)提高到2 500 V(HBM)。

2 ESD网络设计

文献资料显示栅控二极管相对于NMOS器件具有更有效的空间效率,可以达到4 kV(HBM)的ESD保护水平[2],因此在此款数字信号处理电路(DSP)的ESD网络设计中,更多采用了栅控二极管作为主要ESD保护器件。

该数字信号处理电路(DSP)采用数字电路设计流程,使用自主设计的基于部分耗尽SOI(PD SOI)工艺的标准单元库,其供电系统分为内核供电和IO端口供电两部分,因此IO端口分为输入端口、输出端口、双向端口、内核电源地端口和IO电源地端口等类型。电路的ESD保护网络采用上述单元的ESD保护器件进行构建。

图1是输入端口的ESD保护结构示意图。从图中可以看出输入端口采用了两级ESD保护。由于栅控二极管(SDN、SDP)的反向击穿电压低于被保护MOS的栅氧击穿电压,因而当ESD事件发生时可以将电平钳位在安全范围内。

图1 输入端口ESD保护结构示意图

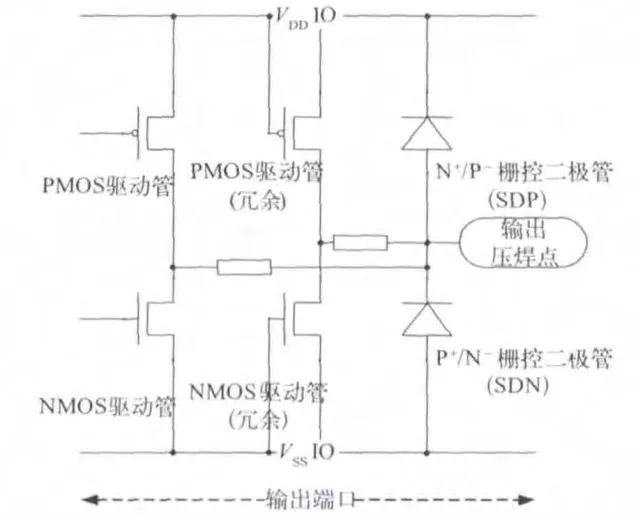

图2是输出端口的ESD保护结构示意图。基于该SOI工艺流片的设计经验,NMOS驱动管自身承受能力不够强,在进入Snapback后很容易失效,因此需要并联接入额外的栅控二极管(SDN、SDP)作为ESD保护器件。但是,由于栅控二极管的反向击穿电压接近甚至高于SOI器件击穿电压,输出驱动管仍有可能被触发进入Snapback,所以为了降低ESD应力对NMOS驱动管的冲击,我们采用了实用新型专利技术,在输出驱动管的输出端加入一个电阻进行降压、限流[3],降低ESD电流对NMOS驱动管的冲击。

图2 输出端口ESD保护结构示意图

双向端口将输入端口和输出端口合二为一。其ESD保护结构示意图如图3所示。

图3 双向端口ESD保护结构示意图

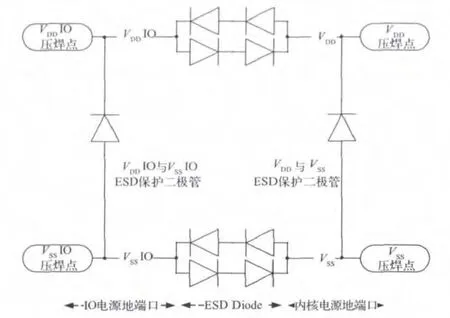

图4是内核电源地端口以及IO电源地端口的ESD保护结构示意图。由于栅控二极管的反向击穿电压接近甚至高于SOI器件击穿电压,有可能发生内部单元在ESD应力下已经发生结击穿而栅控二极管由于反向击穿电压高而未开始工作的情况。根据实践经验,我们通过增加栅控二极管的周长并通过用工艺优化手段调节栅控二极管N-阱掺杂浓度来降低其反向击穿电压,可以避免发生上述情况。同电位的电源与电源之间、地与地之间采用正反双向二级串联的栅控二极管对(ESD Diode)构建ESD电流泄放通路,同时也可以降低端口噪声对内核单元的影响。

图4 电源地端口ESD结构示意图

由上述端口单元ESD保护器件构建的全芯片ESD保护网络如图5所示。

3 ESD网络分析

该数字信号处理电路(DSP)流片后进行可靠性测试,发现其ESD性能不佳,仅达到1 000 V。在进行1 500 V测试时出现双向端口ESD失效,表现为被测试信号端口对IO地端口短路。ESD试验样片重新进行参数测试发现样片电路的静态电流偏大,失效的测试信号端口接触测试异常,端口对地短路。

失效的样片经过EMMI分析,得到典型的失效点分析结果如图6所示。出现的EMMI亮斑即漏电的位置位于NMOS驱动管附近,即存在信号端口对IO地端口的短路。冗余NMOS驱动管和栅控二极管位置没有出现亮斑。这与ESD试验的结果相一致。

图5 全芯片ESD保护网络示意图

图6 失效点EMMI分析结果

另外对与该数字信号处理电路(DSP)一起搭版流片的ESD结构测试芯片进行TLP扫描发现,图4中经过工艺优化的电源地之间的栅控二极管的反向击穿电压高于9 V,偏离了设定的原值(7~8 V),而未经过工艺优化的栅控二极管的反向击穿电压为14 V左右。对PCM的监测发现用于限流的电阻方块阻值低于设定的原值(45 Ω·□-1),仅为34 Ω·□-1。

由于双向端口是由输入端口和输出端口合并而成,因此分析双向端口ESD失效机理时如图5所示的全芯片ESD保护网络可以调整为图7来进行分析。

双向端口的输入输出压焊点与IO地端口的VSSIO压焊点之间的ESD泄放路径可能为图中示意的几种:

(1)路径1:ESD电流经过P+/N-栅控二极管(SDN)泄放到VSSIO;

(2)路径2:ESD电流经过限流电阻和二级保护的P+/N-栅控二极管(SDN)泄放到VSSIO;

(3)路径3:ESD电流经过N+/P-栅控二极管到达VDDIO再经过VDDIO与VSSIO的ESD保护二极管(经过工艺优化的栅控二极管,反向击穿电压高于9 V)泄放到VSSIO;

(4)路径4:ESD电流经过限流电阻和被触发进入Snapback模式的冗余NMOS驱动管(栅极接地的ggNMOS)泄放到VSSIO;

(5)路径5:ESD电流经过限流电阻和被触发进入Snapback模式的NMOS驱动管(栅极由前级反相器驱动)泄放到VSSIO。

双向端口ESD结构的设计原意是通过路径1泄放ESD电流,通过路径2电阻和栅控二极管的分压钳位保护下一级的MOS栅氧。但是由于未经工艺优化调整的栅控二极管的反向击穿电压为14 V,接近甚至高于NMOS的结击穿电压,而用于限流、降压保护NMOS驱动管的电阻由于方块阻值较设定原值小,因而不能确保路径1先于路径5导通泄放ESD电流。国外文献[2]发现栅极电位浮空的NMOS管的抗ESD能力小于同等宽长比的ggNMOS,相差约几百伏,因此失效的是位于路径5上的驱动NMOS而非位于路径4的冗余NMOS。

另外路径3中VDDIO与VSSIO的ESD保护二极管的反向击穿电压高于9 V,高于设定的原值(7~8 V),因此路径3也不能及时泄放ESD电流。

综上所述,原ESD网络设计容易造成用于驱动的NMOS受到损伤,出现对IO地端口的短路。输出端口虽然存在与双向端口类似的路径1与路径5的ESD泄放通路,但是由于该数字信号处理电路(DSP)多数IO端口为双向端口,却只有3个IO端口为单纯的输出端口,所以输出端口的ESD失效问题没有显现出来。

图7 双向端口ESD失效分析示意图

4 ESD保护网络优化

通过对ESD保护网络的分析以及ESD失效机理,我们制定的ESD网络优化方案包含以下内容:

(1)信号端口的P+/N-栅控二极管(SDN)增加掩模版,调整其反向击穿电压为10 V±5%。

通过增加掩模版进行工艺优化来降低P+/N-栅控二极管(SDN)的反向击穿电压可以使栅控二极管先于NMOS驱动管导通泄放ESD电流,但是栅控二极管N-阱掺杂浓度的调整会使PN结反向漏电流增大。经过权衡,我们将栅控二极管的反向击穿电压设定为10 V±5%。

(2)增加NMOS驱动管的限流电阻方块数,增加NMOS驱动管栅长。

由于工艺制备的限流电阻的方块电阻较小,因此增加其方块数提高电阻值可以进一步保证栅控二极管先于NMOS驱动管导通泄放ESD电流。增加NMOS驱动管栅长也可以使NMOS更难以触发进入Snapback。但是这两处改动会造成端口驱动能力的下降,因此需要重新设计端口的驱动管尺寸。

(3)通过继续进行工艺优化,将电源地之间栅控二极管的反向击穿电压调整到7~8 V。

在ESD保护网络中电源地布线一般会用作ESD BUS,因此电源地之间ESD电流泄放通路的可靠性将会影响全芯片的ESD保护性能。所以需要继续进行工艺优化,将电源地之间栅控二极管的反向击穿电压调整到设定原值7~8 V。

采用上述优化方案,对该数字信号处理电路(DSP)进行设计优化后再次投产流片,经过可靠性测试其ESD防护能力由1 000 V(HBM)提高到了2 500 V(HBM)。

5 小结

本文所阐述的ESD保护网络的原始设计,对双向端口的ESD电流泄放通路的考虑有所欠缺,又因工艺控制的偏差,造成了该数字信号处理电路(DSP)的ESD保护性能不佳,通过对整个ESD保护网络的系统分析,找出薄弱环节并进行了设计优化,才能从整体上提高电路的ESD保护性能。由此可以说明,进行全芯片的ESD网络设计时,不能够简单地将已有的ESD保护器件生搬硬套到新的ESD保护网络中,即使是经过流片验证的保护结构和器件。应该将全芯片ESD保护网络作为一个有机的整体进行设计,保证网络中的每一个器件都能够正常发挥自己的作用,同时不影响其他器件的正常工作。这种设计思路和理念,不仅可以应用于SOI电路ESD保护网络的设计,即使扩展到体硅电路,也具有良好的参考意义。

[1] Mansun Chan, Selina S Yuen, ZhiJian Ma, et a1.Comparison of ESD Protection Capability of SOI and BULK CMOS output Buffers [J]. IEEE/IRPS, 1994:292-298.

[2] S Voldman, R Schulz, J Howard, et a1. CMOS-on-SOI ESD Protection networks [J]. EOS/ESD Symp, 1998: 333-350.

[3] 罗静,颜燕,罗晟. 抗辐照SOI 256kB只读存储器的ESD设计[J]. 电子与封装,2011, 11(9): 27-31.