基于FPGA技术的多通道符合计数器研制

叶 惠,张安宁,王亿芳,刘 延

(湖南师范大学物理与信息科学学院,中国 长沙 410081)

基于FPGA技术的多通道符合计数器研制

叶 惠,张安宁*,王亿芳,刘 延

(湖南师范大学物理与信息科学学院,中国 长沙 410081)

设计了基于FPGA的多通道符合计数器,此设计将符合窗口时间的设定集成于FPGA器件中,因此集成度更高,并且通过实验进行了模拟单光子探测器脉冲信号的符合测量,计数误差为0.02%,能用于对纠缠光子对的判定.

符合计数;纠缠光子对;FPGA

符合测量最早由物理学家博思(Walth Bothe)用于判断在光子和电子的碰撞中,能量和动量守恒定律是否在每一次碰撞中均有效[1].博思由此获得1954年诺贝尔物理学奖.符合计数技术在核物理与宇宙射线的研究领域被广泛运用.随着符合计数技术不断的发展,如今符合计数技术也被应用于量子信息科学中多光子纠缠的测量和判定[2-3].

简单的符合计数系统可以用简单的门电路或乘法器来实现[4].但是随着符合计数器复杂程度的增加,当用于多通道符合测量时,电路的复杂程度与成本将会随之上升,此时信号在经过门电路后产生的延迟将是无法控制的,很有可能影响到符合测量最终的结果[5].得益于数字电子技术的飞速发展[6-8],市场上商品化的符合计数器大多数是用专用集成电路(ASIC)完成的,这些计数器的测量能精确到PS一级,并且有些还可实现符合窗口的随意可调.只是用ASIC实现符合计数器对仪器要求很高,且价格昂贵.但随着现场可编程门阵列(FPGA)的快速发展[9],FPGA具有更多的门电路,体积更小成本更低,并且方便随时修改设计直至满足实验要求.本文设计了基于FPGA的多通道符合计数器,此设计将符合窗口时间的设定集成于FPGA器件中,因此集成度更高,并且通过实验进行了模拟单光子探测器脉冲信号的符合测量.

1 基本结构

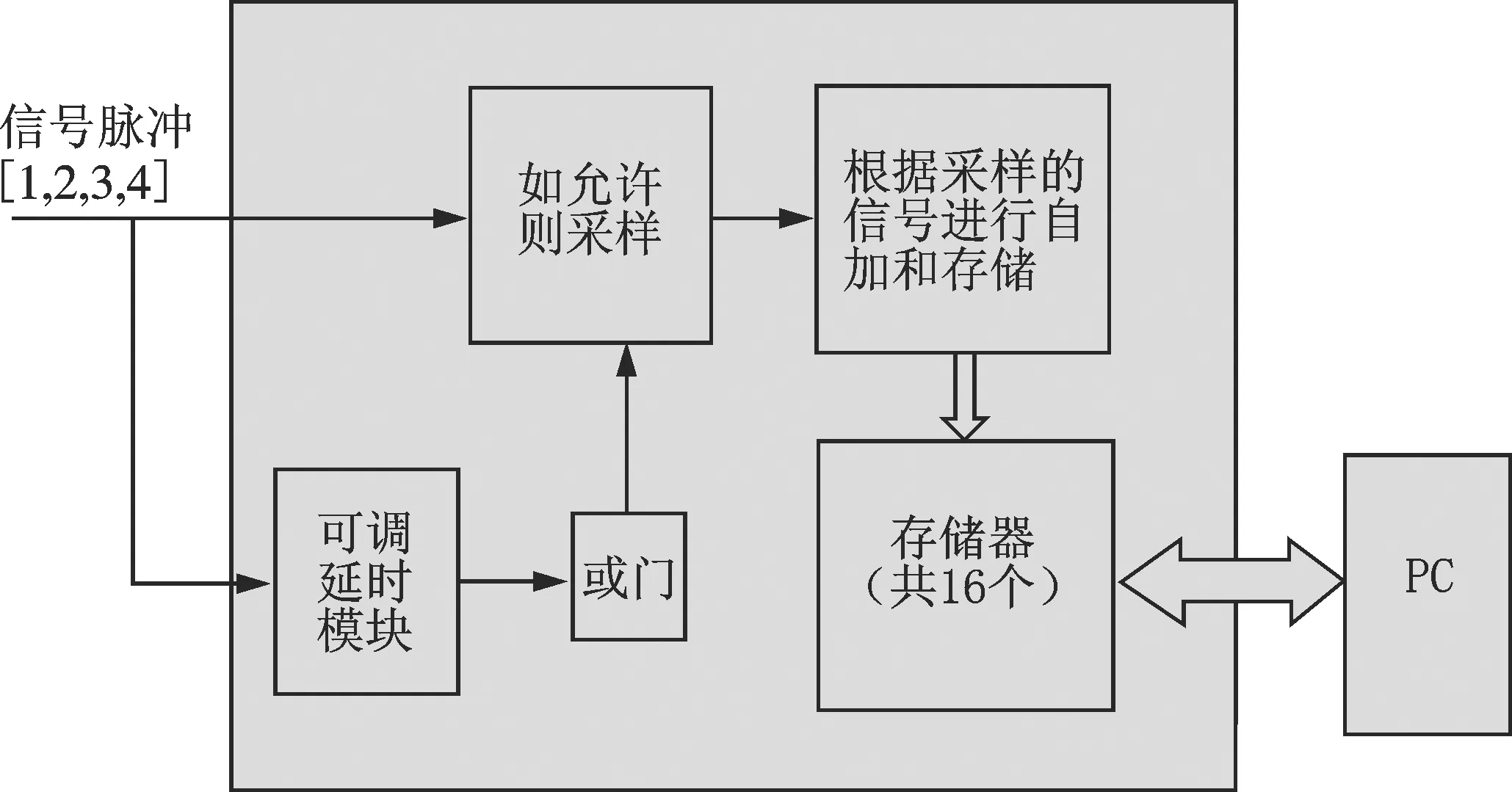

实验要求对纠缠光子对进行判定[10-11],在设计上只需要对在一个符合要求的固定的时间窗口内的符合事件发生的次数进行计数,并不需要具体知道两个信号之间的时间间隔.所以本实验最重要的设计要求是记录下符合事件发生的次数.符合计数时间窗口,也称为符合分辨时间,为两路脉冲能发生符合的最大间隔时间,它是判断符合计数器性能的重要依据.所以符合窗口的大小决定了整个实验数据的准确性.大部分的符合计数器都是采用可编程延迟线来进行符合时间窗口的设定,现一般可编程延迟线可提供精度为纳秒量级的从纳秒到微秒范围的符合时间,例如多伦多大学的Alan Stummer所设计的11通道符合计数器就采用了这种方法.而作者的设计不采用可编程延迟线的方法来进行符合时间窗口的设定,而是将可调整的延时模块内置于FPGA器件中,在实现相同功能的前提下,使得设计集成度更高,且成本降低.

图1 通过或门后所产生的符合时间窗口Fig.1 The coincident time window produced by through the or gate

设计思路如下:监视四路输入,当任何一路有上升沿输入的时候采样,如用现场可编程门阵列(FPGA)来实现的话,则是把四路信号分为另外同样的四路信号取或之后(简称为四路或),只要监视这四路或信号是否有上升沿输入.如有,则表示四路信号中至少有一路是有上升沿输入的,而信号通过或门时肯定会有一定延时的(逻辑器件都有其延时,FPGA也不例外,并且不同器件延时时间不同,一般加上线路延时不超过5 ns).那么正好得到信号输入时刻与采样时刻的一个延时(如图1).而这个延时正是一个或门与传输线延时的总和,这正是作者所需要的符合时间窗口.经过测量,作者所使用FPGA器件中或门延时为1~3 ns,符合实验的精度要求.值得注意的是,要求输入信号的持续时间要大于此延时才能正常取样.而在本实验中,单光子探测器的信号是12 ns宽,满足这个前提条件.

符合计数器采样时,如果采到两路或者更多路有高电平信号,就表示在这段延时里出现了这几路信号.可认为在该符合时间的精度下,这几路信号是同时发生的,并且它的符合分辨时间就是此延时.在该符合计数器中,实测或门加上线延时的总延时时间为1 ns,满足本实验要求.在多光子纠缠领域的实际应用中,符合时间窗口常为3 ns到5 ns间,所以作者在或门之前加入可调延时模块,在或门延时过小时增大符合时间窗口,使实验更加灵活.使用时只需把采集到的相应信号存储下来,就可得到符合信号的计数统计信息.这与初始的设计思想相吻合.接下来只要把有用信号存储并交与PC显示即可.符合计数过程如图2.

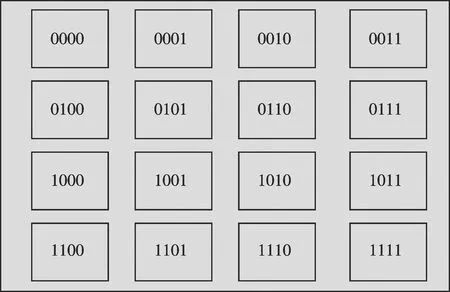

在取样随后的存储和与PC交互的过程中,四路输入的信号脉冲将被做为FPGA中的随机存储器的地址信号进行存储,四路信号不同的电平将代表不同的地址,即存储单元.四路输入可以测量的符合情况有16种,不同符合情况下的计数统计将存储在RAM内16个不同的存储单元中(如图3所示).当第一路有脉冲信号输入时,RAM的地址为0001,此时0001所对应的存储单元中的数据会进行加1.

图2 基于FPGA的符合计数过程Fig.2 The coincidence counting process based on FPGA

图3 RAM中16个不同的存储单元Fig.3 The 16 different storage units in RAM

当在符合时间窗口内,第一路和第三路有信号脉冲上升沿发生,则RAM的地址为0101,相对应的存储单元也会进行加1.本程序所设计的为每1 s进行一次计数显示,也就是在采样开始之后,FPGA不断地进行符合情况的统计计数,并且将统计存储在RAM中,然后通过串口与PC进行计数结果的传输,在PC上每1 s显示一次计数结果,这样使用者就能知道在这1 s之内,有哪些符合情况发生及发生的次数,从而对纠缠光子对进行判定.

2 FPGA中主要模块设计

2.1 Coindetected模块

此模块分为两块:第一部分实现四路或信号的延时.这个模块利用apd_dly <=apd[0]| apd[1]| apd[2]| apd[3](这里的逻辑或可以提供一个信号通过或门的延时)得到apd_dly信号相对于四路原始信号的一个延时.如果延时不够,还可以用线的复用:apd_dly1 =apd_dly,来实现线的延时.这个线的延时可以根据需求设置2级甚至更多.

延时信号主要用来判断采样的时机.即该模块的第二部分:采样并发送数据给下一个模块让其能做出相应的动作.采样时机的关键判断如下:

always @(posedge clk or negedge rst_)

if(!rst_)

coin_detected_buf <=3′b0;

else

coin_detected_buf <={coin_detected_buf[1:0],pe_apd_latch_dly};

assign coin_detected =(coin_detected_buf[2:0] ==3′b001) &RunEn;

如此即得出一个模拟的符合窗口.

2.2 存储模块与自加模块

该模块的主要功能是进行数据统计与存储.通过设置16个存储器以此对应四路信号可能发生符合的每一种状况.分别是0000、0001、…、1110、1111.只要在coindetected模块中采样到了任意一种,这个模块都会在对应的存储器上进行数值的自加,并且把自加完的数据继续存于这个存储器中.

2.3 串口输出模块

为了便于更好地观察实验数据,本实验采用了串口协议来实现人机交互.串口的传输速率虽然比其他协议慢,但是可以满足输出数据的要求.并且串口协议是最简洁的协议,不管是输入还是输出都容易实现.

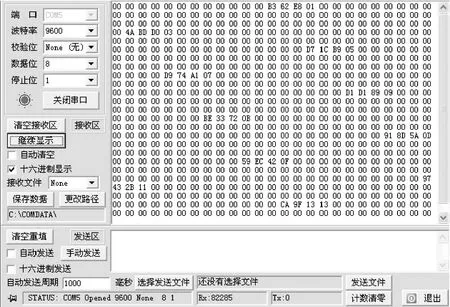

作者在程序中设定一个固定的时间T.每过一个T时间,FPGA定期地把存储模块中各个存储器的数据发往串口,通过终端的串口小助手,就可得到每个存储器的数据.进而,也得到了有纠缠光子的次数.此外,还增加了一个功能:从计算机上接收指令,FPGA会根据指令重启.

3 实验结果及分析验证

现以作者所设计的符合计数器进行实验,FPGA选用了ALTERA公司的CycloneⅡEP2C8Q208N,通过Verilog HDL语言进行功能程序编写[12].工作频率为100 MHz,通过USB-串口进行数据传输,并且利用串口助手在PC上进行计数显示.单光子探测器所发出的脉冲信号脉宽为12 ns,作者将利用信号发生器制造脉冲信号(32 MHz脉冲信号,脉宽为15.62 ns)来模拟单光子探测器所发出的电脉冲信号[13].在本设计中,每隔1 s,依次显示16种情况的计数(第一种为0000,第二种为0001,一直到第十六种为1111).每一种情况的计数结果将依次通过八位16进制的数进行显示.清零后第一秒计数结果显示后,将紧接着显示前两秒钟的计数结果,后面每一秒钟增加一次,也就是第N秒钟显示的计数结果将是前面N秒钟总共的计数.图4为截取的第一路和第二路同时输入同样的32 MHz脉冲信号时,清零后第一秒测得的数据,计数情况为0011,计数结果为第四种情况处所显示的8位16进制数8′h1E862B3,转化为十进制为32 006 835.

图4 清零后0011信号输入时第一秒计数结果显示Fig.4 The first seconds counting results show when the input signal is 0011 after the reset

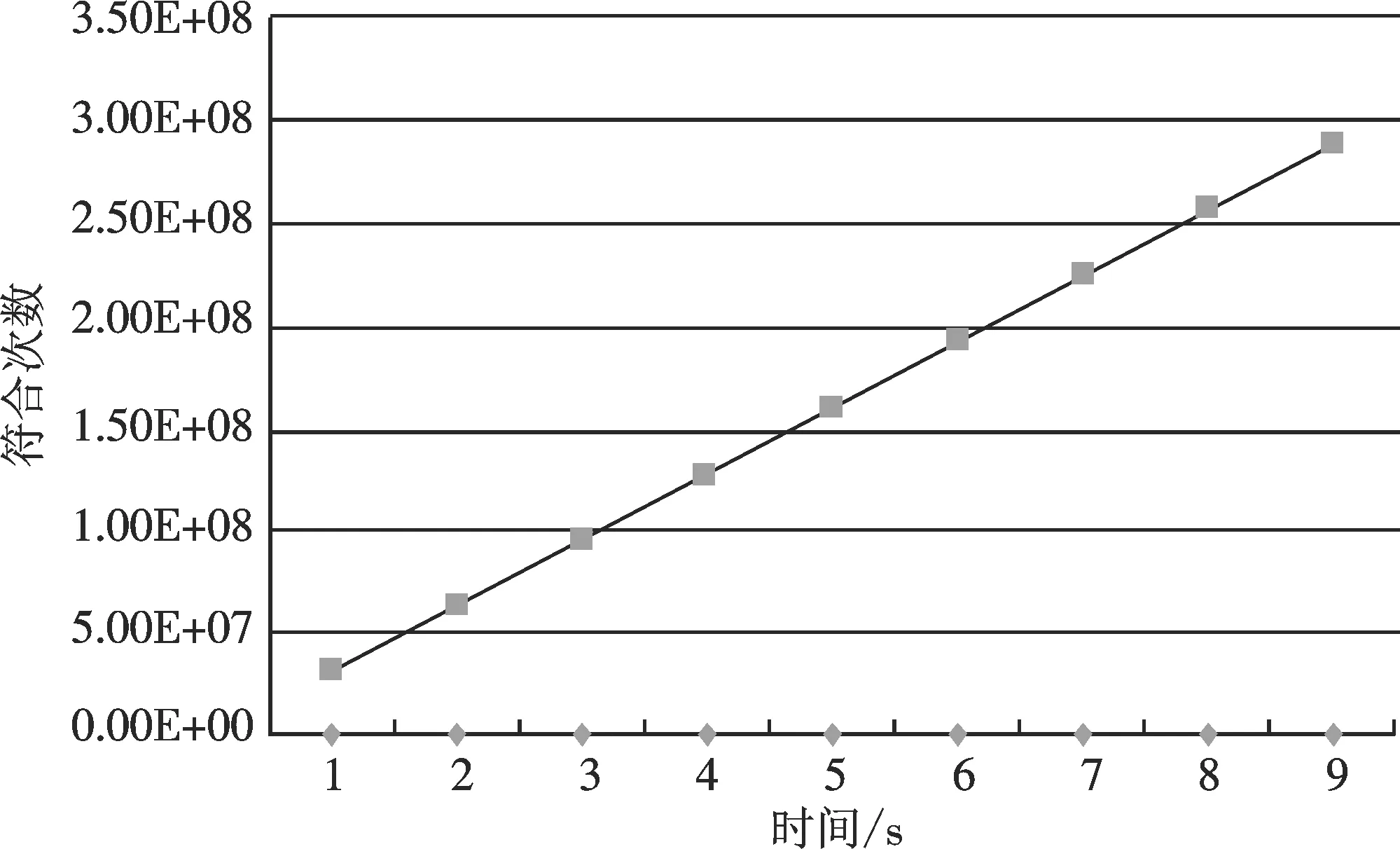

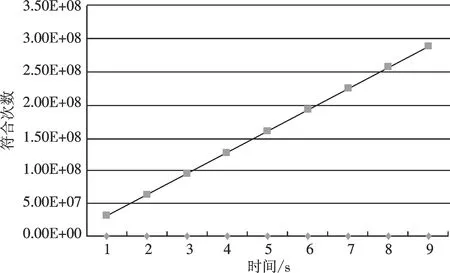

图5为作者给第一路和第二路同时输入同样的32 MHz脉冲信号时测得的数据,因为是同时输入相同的脉冲信号,并且在50 MHz晶振通过FPGA倍频达到100 MHz的时钟频率情况下,所以不管符合窗口时间设置为多少(此时符合时间窗口为或门延时,即本系统最短符合时间窗口),清零后第一秒内所发生的符合情况的次数都应该与输入信号频率大小相差无几.第二秒发生的次数则是频率大小的两倍.

图5 0011信号输入时计数结果显示Fig.5 Counting results show when the input signal is 0011

由图5可知,在第三个八位16进制数的符合情况处有数据进行统计,因为作者是从计数系统清零后开始工作,所以在第一秒的符合计数中,所发生的符合情况为0011,将16进制转换为十进制可知此符合情况的的次数为32 006 835,第二秒统计次数转换为十进制为64 011 594,计数误差为0.02%,可知此设计基本满足实验要求.

图6与图7分别为输入0101信号与输入1111信号时的符合计数情况.因为同时输入频率为32 MHz脉冲,各种不同输入情况所测得的计数结果应该相差无几,由图6与图7可知,测试结果正确.

图6 0101信号输入时符合计数情况Fig.6 Counting results show when the input signal is 0101

图7 1111信号输入时符合计数情况Fig.7 Counting results show when the input signal is 1111

4 结论

设计了基于FPGA的多通道符合计数器,利用信号发生器模拟单光子探测器发出的信号,测量了几种不同情况信号输入时的符合计数情况,计数误差为0.02%,证明该符合计数器能用于对纠缠光子对进行判定.相比于其他符合计数器,该设计具有三大优势.第一,相比于ASIC,利用FPGA进行设计价格更便宜,体积更小.其开发难度较小,开发周期较短.并且当需要更多路数据采集时,FPGA器件更容易扩展,基本不会增加成本.第二,由于FPGA可以方便地多次重复程序配置的特性,在该设计中可将调整延迟模块内置于FPGA中,通过对FPGA程序调整可任意改变符合时间窗口,满足不同实验要求.因此该设计相比于其他基于FPGA的符合计数器集成度更高,更加简洁.第三,相比于TAC(时间-幅度转换器)[13],该设计系统更加简洁.TAC不仅记录符合事件发生的次数,同时还测量发生符合的两信号脉冲的时间间隔.因此TAC更多用于与时间相关的单光子计数等测量实验中.而该设计只记录符合事件发生的次数,专为多光子纠缠研究所研制.

[1] HUO Q, ZHANG J. Multi-channel coincidence counter for coincidence measurement[J]. Acta Sinica Quantum Optica, 2011,17(2):135-140.

[2] THORN J J, NEAL M S, DONATO V W,etal. Observing the quantum behavior of light in an undergraduate laboratory [J]. Am J Phys, 2004,72:1210-1219.

[3] CARLSON J A, OLMSTEAD M D, BECK M. Quantum mysteries tested: an experiment implementing hardy’s test of local realism [J]. Am J Phys, 2006,74:180-186.

[4] BRANNING D, BHANDARI S, BECK M. Low-cost coincidence-counting electronics for undergraduate quantum optics [J]. Am J Phys, 2009,77:667-670.

[5] BARONTI F, LAZZERI A, RONCELLA R,etal. FPGA/DSP-based Implementation of a high-performance multi-channel counter [J]. J Syst Arc, 2009,55(5-6):310-316.

[6] ZAPPA F, GULINATTI A, MACCAGNANI P,etal. SPADA: single-photon avalanche diode arrays[J]. Photo Tech Lett IEEE, 2005,17(3):657-659.

[7] 薛 辉,邓 军,叶柏龙,等.分布式数据交换平台在电子政务中设计与实现[J].湖南师范大学自然科学学报, 2012,35(6):44-47.

[8] NICLASS C, GERSBACH M, HENDERSON R,etal. A single-photon avalanche diode implemented in 130 nm CMOS technology [J]. J Sel Top Quantum Electron, 2007,13(4):863-869.

[9] 夏宇闻.Verilog数字系统设计教程[M].北京:北京航空航天大学出版社, 2008.

[10] KWIAT P G, MATTLE K, WEINFURTER H,etal. New high intensity source of polarization entangled photon pairs [J]. Phys Rev Lett, 1995,75(24):4337-4341.

[11] JENNEWEIN T, SIMON C, WEIHS G,etal. Quantum cryptography with entangled photons[J]. Phys Rev Lett, 2000,84(20):4729-4732.

[12] 周润景,苏良碧.基于Quartus II的数字系统Verilog HDL设计实例详解[M].北京:电子工业出版社, 2010.

[13] 李 勇,苏 弘,千 奕,等.多道时间幅度变换电路的设计[J].核电子学与探测技术, 2006,26(4):454-457.

(编辑 陈笑梅)

Design of the Multi-Channel Coincidence Counter Based on FPGA

YEHui,ZHANGAn-ning*,WANGYi-fang,LIUYan

(Institute of Physics and Information Science, Hunan Normal University, Changsha 410081, China)

Based on FPGA a multi-channel coincidence counter is designed, in which the setting of window time is integrated in FPGA in order to improve the integration of the system. Furthermore, the coincidence counting experiment is conducted by using signal generator to simulate the pulse signal produced by single photo detector. Results show that the error of measurement is 0.02%, and it can be used to judge the entangled photon pairs.

coincidence counting; entangled photon pairs; FPGA

2013-11-19

国家自然科学基金青年基金资助项目(60907031); 教育部留学人员科研启动基金资助项目((2010)1174)

*

,E-mailanzhang@hunnu.edu.cn

O431.2

A

1000-2537(2014)01-0053-05