5.8 GHz 0.18 μmCMOS低噪声放大器的设计

周洪敏,张 瑛,丁可柯

南京邮电大学 电子科学与工程学院,南京 210046

5.8 GHz 0.18 μmCMOS低噪声放大器的设计

周洪敏,张 瑛,丁可柯

南京邮电大学 电子科学与工程学院,南京 210046

1 引言

近些年来,随着无线通信技术的迅猛发展,高集成度、小型化和低功耗成为了无线通信的重要特征和需要。由于CMOS器件具有功耗低且集成度高的优点,CMOS技术正越来越多地应用于无线射频收发芯片的设计。低噪声放大器(LNA)是无线接收机前端的关键模块,它需要满足以下要求:具有低的噪声系数以提高接收机的灵敏度;具有足够的增益以抑制后级电路的噪声对系统的影响;要求有一定的线性度,以保证接收到的射频信号不失真;为了避免能量损失和对天线的反射干扰,LNA的输入阻抗应该与前端源阻抗匹配;具有较低的功耗[1]。在实际设计中,这些性能指标会相互牵制相互影响,所以在设计过程中要对这些性能指标进行折衷处理[2]。

2 电路设计与优化

2.1 电路结构分析

基于CMOS工艺的低噪声放大器设计一般采用经典的共源共栅源级电感负反馈结构[3],基于这种结构本文设计了一种工作频率为5.8 GHz的CMOS低噪声放大器如图1所示,M1是放大管,Lg、Ls与放大管一起实现输入阻抗匹配,并将输入功率信号转化为电流信号,利用源级电感Ls来得到一个具有正实部的输入阻抗,并可以在功耗受限的情况下得到较优的噪声性能。M2是Cascode管,用于减少共源管M1的Miller效应和有限输出阻抗对放大器性能的影响,并提供良好的反向隔离性[4]。

图1 5.8 GHzLNA拓扑结构

2.2 功耗约束下的噪声分析及最佳MOS管宽度选择

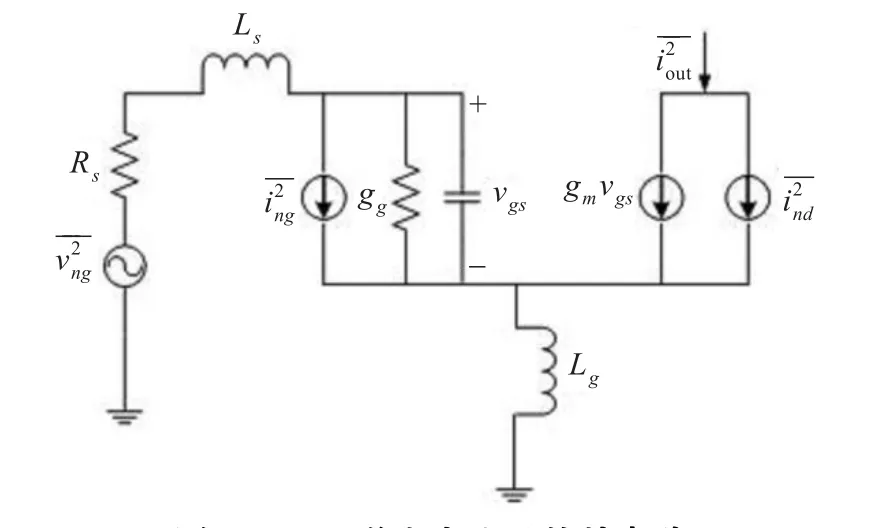

此结构LNA的噪声主要来源于输入回路放大管M1的高频噪声,而对于MOSFET噪声模型主要包含两个噪声源,即漏极电流噪声和栅极电流噪声[5]。NMOS LNA输入回路的噪声模型如图2所示。

图2 LNA噪声小信号等效电路

其中均方漏电流噪声为:

栅电流噪声为:

式中:

这两种噪声电流之间存在一定的相关性,其相关系数c如式(4)所示:

由经典的噪声理论可推导出噪声系数的表达式为[6]:

在式(1)~(9)中,k是波尔兹曼常数,T 是绝对温度,gd0表示漏源电压为零时的导纳,ωT为MOS管的截止频率,ω为工作频率,δ和γ是与工艺相关的噪声参数,且δ=2γ。在TSMC 0.18 μm射频工艺中 γ约为1.68。

2.3 输入匹配电路设计

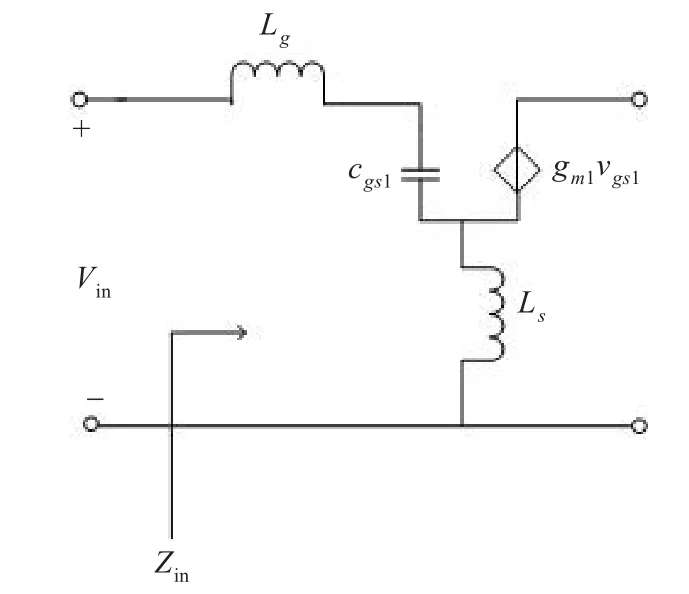

由图1可知,该结构的共源级电路小信号模型如图3所示。

图3 共源级电路小信号模型

由图3可知,该结构的输入阻抗为[7]:

输入电路谐振时:

在一定的偏置和器件尺寸条件下,选取适当的Ls使得输入阻抗50 Ω,即可实现输入端的阻抗匹配。

2.4 级间匹配电路设计

在图1所示的电路中,电感Lm和电容Cm用于完成级间的阻抗匹配。从图1可知,如果在M1管和M2管之间不加电感Lm和电容Cm,让M1管的漏极与M2管的源级直接相连,那么晶体管M1的输出等效阻抗为:

由此可见,M1的输出阻抗和M2的输入阻抗都是呈现容性[8],两级之间没有形成共轭匹配,为了达到最大的功率传输和最优的噪声系数,文献[8]在两级之间串联了一个电感,但是电感值通常都是非常大的。为了减小芯片面积,还有一种方法是使用一个并联的LC网络来代替大电感[9]。图4是LC并联网络及其等效电路,为推导的方便将电感模型等效为一个理想的电感Lm和理想电阻Rm的串联。这个LC并联网络的等效阻抗为:

式中ωm是LC并联网络的谐振频率,ω为电路的工作频率,从 L1和 R1的表达式可知,当 0<1-(ω/ωm)2<1时,这个小的LC并联网络可以产生一个大的电感。

图4 LC并联网络及其等效电路

2.5 稳定性分析

稳定性是LNA的一个重要的性能指标。在放大器的设计中,必须保证放大器的稳定性,否则放大器在一定条件的激励下有可能会出现自激现象。对一个放大器的二端口网络来说,绝对稳定条件用稳定因子K来描述[10]:

要使得LNA绝对稳定,必须保证K大于1。

3 电路实现与仿真结果

3.1 电路实现及关键参数的选取

基于以上分析所完成的LNA电路如图1所示。M3和R2组成LNA的偏置电路,电源电压、电阻 R1和 M3的栅源电压决定了M3的工作电流,晶体管M3与M1形成电流镜。为了使偏置电路的附加功耗减到最小,将M3的栅宽取为M1栅宽的十分之一。电阻R2选择得足够大,以减少偏置电路对交流信号通路的影响。

由以上分析可知,在有功耗约束的情况下,晶体管的最优器件宽度的计算公式如式(8)所示,首先利用公式(8)计算出晶体管的最优器件宽度。然后根据公式(11)、(12)可计算出 Ls和 Lg的值。

在完成上述关键参数的选取后,再对Lm和Cm进行优化。在进行Lm和Cm的优化过程中,主要围绕获得最大正向功率增益和最小噪声系数进行选取。由于密勒效应的影响,输入匹配会受到级间匹配元件的影响,所以需要反复调整各元器件的值以达到良好的匹配。

3.2 仿真结果

设计采用TSMC0.18 μmCMOS射频工艺,在Cadence软件环境下完成电路各项性能指标的仿真。在1.5 V工作电压下,电路的静态功耗为12.7 mW,中心工作频率为5.8 GHz。仿真结果如下。

(1)S参数:S参数随频率的变化如图5所示。在中心频率5.8 GHz处,输入反射系数S11=-12.15 dB,输出反射系数S22=-20.03 dB,说明实现了比较好的输入输出匹配,功率增益S21=10.3 dB,具有足够的增益,反向隔离度S12=-16 dB,具有比较好的隔离度。

图5 LNA的S参数特性

(2)噪声性能分析:噪声系数和最小噪声系数随频率的变化如图6所示,在中心频率5.8 GHz处,噪声系数NF=2.312 dB,具有较低的噪声系数。

(3)线性度:由图7可知,在中心频率5.8 GHz处,该LNA的输入1 dB压缩点为-12.522 5 dBm,具有较好的线性度。

(4)稳定性:本文对放大器的稳定因子Kf进行了仿真,如图8所示,由仿真结果可以看出Kf始终大于1, LNA处于无条件稳定。

图6 LNA的噪声系数特性

图7 1 dB压缩点

图8 稳定性

表1给出了本文设计的LNA电路的性能指标,并与已发表的文献中的LNA电路进行了比较。可以看出,在相同的工艺和相应的频率下,本文设计实现了增益、噪声系数和线性度间的折衷。

表1 LNA性能比较

4 总结

基于0.18 μmCMOS工艺设计了一个频率为5.8 GHz的LNA,从噪声系数、阻抗匹配以及级间匹配等方面对电路的性能进行了优化。与传统的共源共栅结构相比,该电路在两级之间增加了级间匹配网络,获得了良好的增益、噪声系数以及线性度。

[1]刘萌萌,张盛,王硕,等.一种CMOS超宽带LNA的优化设计方法[J].电子学报,2009,37(5):1082-1086.

[2]Goo J S,Ahn H T,Ladwig D J,et al.A noise optimization technique forintegrated low noise amplifiers[J]. IEEE Journal of Solid State Circuits,2002,37(8):994-1002.

[3]Shaeffer D K,Lee T H.A 1.5 V 1.5 GHz CMOS low noise amplifier[J].IEEE Journal of Solid State Circuits,1997,32(5):745-759.

[4]Ismail A,Abidi A.A 3 to 10 GHz LNA using a wideband LC-ladder matching network[J].IEEE Journal of Solid State Circuits,2004,39(12):2269-2277.

[5]迟保勇,余志平,石秉学.CMOS射频集成电路分析与设计[M].北京:清华大学出版社,2006.

[6]Lee T H.CMOS射频集成电路设计[M].余志平,译.北京:电子工业出版社,2006.

[7]Shameli A,Heydari P.Ultra-low power RFIC design using moderately inverted MOSFETs’:an analytical/experimental study[C]//Proceedings of the IEEE Radio Frequency Integrated Circuits Symposium(RFIC’06),2006.

[8]Zhang C,Huang D Q,Lou D W.Optimizations of cascode MOS low noise amplifier using inter-stage matching network[C]//IEEE Conf Elec Dev and Sol Sta Circ,Hong Kong,China,2003:465-468.

[9]Mou S X,Ma J G,Seng Y K,et al.A modified architecture used for input matching in CMOS low noise amplifiers[J].IEEE Transactions on Circuits and Systems,2005,52(11):784-788.

[10]Radic J,Djugova A.Videnovic-Misic M.A 2.4 GHz highgain low noise amplifier[C]//InternationalSymposium on Signals,Circuits and Systems.Iasi:IEEE,2009:1-4.

[11]杨波,周盛华,王科平,等.应用于802.11a的5.8 GHz CMOS LNA设计[J].长春理工大学学报:自然科学版,2008,31(4):91-93.

[12]Li X,Shekhar S,Allstot D J.Gm-boosted common-gate LNA and differential colpitts VCO/QVCO in 0.18 μm CMOS[J].IEEE Journal of Solid-State Circuits,2005,40(12):2609-2619.

[13]El-Gamal M N,Lee K H,Tsang T K.Very low-voltage(0.8 V)CMOS receiver frontend for 5 GHz RF applications[J].IEE Proceedings of Circuits Devices Systems,2002,149(56):355-362.

[14]Wang Y S,Lu L H.5.7-GHz low-power variable gain LNA in 0.18 μm CMOS[J].Electronics Letters,2005,41(2):66-68.

[15]艾学松,孙玲,施佺.应用于DSRC系统的5.8 GHz CMOS LNA设计[J].电路与系统报,2012,17(3):134-138.

ZHOU Hongmin,ZHANG Ying,DING Keke

College of Electronics Science and Engineering,Nanjing University of Posts and Telecommunications,Nanjing 210046,China

Based on TSMC 0.18 μm CMOS technology,a novel circuit topology for a CMOS Low-Noise-Amplifier(LNA)is presented in this paper.In this circuit,a cascode topology with inter-stage matching network is designed at the frequency of 5.8 GHz.Choosing a inter-stage matching network presents lower power dissipation while achieving reasonable power gain.In order to save the chip area,a LC network is used instead of the large inductor.The simulation results show the forward gain(S21)is about 10.3 dB,as well as less than - 16 dB isolation(S12)while operating at 5.8 GHz.The input impedance(S11)and the output impedance(S22)also represent good performance.In addition,the minimum noise figure and signal linearity performance are quite good.It consumes only 12.7 mW under a 1.5 V voltage supply.

low noise amplifier;CMOS;noise figure;linearity

基于0.18 μm CMOS工艺,设计了一个新型的低噪声放大器。在该放大器中,采用带有级间匹配的共源共栅结构。采用级间匹配结构实现了低功耗高增益。为了降低芯片面积,使用LC并联网络代替传统的大电感。仿真结果表明,在5.8 GHz的工作频率下,功率增益大约为10.3 dB,而反向隔离度低于-16 dB。同时具有比较好的输入输出匹配。除此之外,还获得了比较小的最小噪声系数和比较好的线性度。在1.5 V的供电电压下,电路的静态功耗为12.7 mW。

低噪声放大器;CMOS;噪声系数;线性度

A

TN4

10.3778/j.issn.1002-8331.1312-0173

ZHOU Hongmin,ZHANG Ying,DING Keke.Design of 5.8 GHz 0.18 μm CMOS low noise amplifier.Computer Engineering and Applications,2014,50(23):61-64.

国家自然科学基金青年科学基金(No.61106021);江苏省高校自然科学基金(No.11KJB510019);南京邮电大学青蓝工程基金(No.NY210037)。

周洪敏(1978—),女,讲师,研究方向为射频集成电路设计。E-mail:zhouhm@njupt.edu.cn

2013-12-13

2014-03-18

1002-8331(2014)23-0061-04

CNKI网络优先出版:2014-04-29,http://www.cnki.net/kcms/doi/10.3778/j.issn.1002-8331.1312-0173.html