基于FPGA和USB的GNSS中频信号采集器设计∗

赵 琳, 王 野, 丁继成

(哈尔滨工程大学自动化学院 哈尔滨 150001)

基于FPGA和USB的GNSS中频信号采集器设计∗

赵 琳, 王 野, 丁继成

(哈尔滨工程大学自动化学院 哈尔滨 150001)

以FPGA+DSP经典高速数据采集平台为核心,应用MAX2769射频芯片,实现了通用GNSS中频数据采集器的设计。采集器可以接收各GNSS系统卫星的中频信号并转换成数字中频数据,通过编写USB设备控制程序和上位机人机交互程序,实现中频数据的高速采集、传输和保存,并应用接收到的数据完成频谱分析和信号捕获。实验结果表明,研制的GNSS中频数据采集器能够正确、完整地保存数据,并且数据满足定位要求。

GNSS; 中频数据; FPGA; USB

引言

随着各种全球导航卫星系统GNSS(Global Navigation Satellite System)的建成与完善,卫星导航定位接收机的研究与应用日渐广泛。当前GNSS接收机已经融合了软件无线电的概念,逐渐由架构固定的硬件接收机过渡到了软件GNSS接收机研究阶段,它以多系统组合导航为目标,是目前研究最多、最有可能先与其他系统集成实现GNSS组合导航的接收机平台[1]。

GNSS中频信号采集器接收GNSS高频信号并将其转换为中频数据,它是GNSS软件接收机研制过程中的关键环节[1]。目前,市场上有Accord公司的GPS(Global Positioning System)L1和L2信号的中频信号采样器,北京东方联星科技有限公司的GPS L1信号的中频信号采样器。这些产品价格昂贵,且内部结构不公开,使得软件接收机的开发受到了很大的限制。基于该现状,本文以FPGA+DSP经典高速数据采集平台为核心,应用MAX2769射频芯片,设计了一种多系统通用GNSS中频信号采集器[2]。

1 系统硬件设计

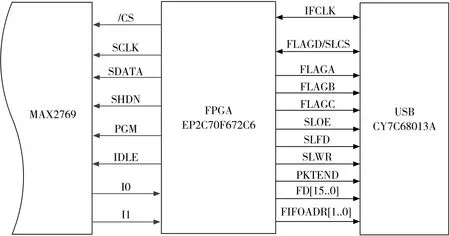

GNSS中频信号采集器的硬件分为三个部分:GNSS射频前端,FPGA控制与数据转存模块,USB (Universal Serial Bus)数据传输模块。其系统的硬件架构如图1所示。

1.1 GNSS射频前端

射频前端采用美信半导体公司生产的MAX2769芯片,此芯片适用于GPS/GLONASS/Galileo接收机,同时也可以通过配置寄存器实现北斗导航卫星信号的接收,该芯片不仅可以实现单频卫星导航接收机功能,也可实现多体制卫星导航系统的组合。

图1 系统硬件架构图

芯片内部集成设计了包括双输入低噪声放大器、混频器、抑制镜像滤波器、可N分频的频率合成器、增益控制放大器、压控振荡器、晶体振荡器以及多位ADC的完整接收机功能单元,总噪声系数低达1.4dB。片内集成的Σ-ΔN分频合成器方便中频编程实现,精度可达±40Hz,有利于与系统全局时钟频率进行有效的配合工作。芯片内部独特设计的ADC输出既可以为I、Q支路输出一个或两个量化位,又能为I支路输出三个量化位。它支持CMOS和有限差分逻辑电平两种输出数据格式。

1.2 FPGA控制与数据转存模块

FPGA选择Altera公司主打的Cyclone II市场化产品EP2C70F672C6 FPGA芯片,实现MAX2769射频前端的控制与中频数据信号的接收,并控制CY7C68013A USB芯片,构成主从FIFO结构,实现数据的高速传输。芯片内部集成了68416个逻辑资源,能够设计实现大量功能单元,主要有内嵌式18bit×18bit乘法器、可扩展专用存储器外部接口电路、4Kbit内置存储模块、锁相环模块和高速差分I/O线,资源相当丰富。FPGA部分整体的设计方案如图2所示[3]。

图2中与射频相连部分,PGM为工作状态选择:高电平时为高低电平配置工作状态,低电平时为串行配置工作状态。SCLK(串行时钟)、CS(芯片选择)和SDATA(串行数据)为射频工作模式配置接口,既可以通过电平实现8种预配置工作,也可以经SPI协议实现射频内寄存器的串行配置。

图2中与USB相连部分,IFCLK为48MHz接口时钟,由芯片内部产生;CT2FLAG(A-C)为FIFO标志位,反映FIFO当前的空满状态;CS为从属FIFO片选信号;FD[15:0]为16位数据总线;FIFOADR[1:0]用于选择内部4个缓冲区之一(EP2,EP4,EP6,EP8);SLOE是数据总线FD的输出使能信号;PKTEND用于末尾数据处理,被激活时,表示向USB提交IN包,不考虑包的长度。

图2 FPGA硬件连接图

1.3 USB部分

本文选用Cypress公司EZ-USB FX2LP系列芯片中的CY7C68013A,它完全支持USB2.0标准,集成度高,且其具有以下结构特点:①具有1个智能串行接口引擎和1个8051处理器,在执行所有基本的USB功能的同时,保证了持续高速有效的数据传输;②4KB大容量FIFO数据缓冲区,有效支持USB接口的从属FIFO和GPIF(General Programmable Interface)两种工作模式;③固件软配置功能,可将固件程序由主机控制,方便在不修改硬件的情况下修改固件[4]。USB接口电路设计见图2。

2 系统软件设计

采集器系统的软件包括FPGA控制射频前端和USB、数据串并转换的Verilog程序、USB内部固件程序和上位机程序三个部分,系统的整体软件结构如图3所示。

图3 卫星信号接收系统数据接收方案

2.1 FPGA程序设计

首先,FPGA对射频前端进行配置。然后,FPGA将从射频前端接收的中频信号由2位串行数据转换成8位并行数据并送入缓冲,同时控制USB接口芯片工作,将该并行数据传送到USB接口芯片的端点FIFO中,供上位机完成端点FIFO中数据的接收、存储和处理。

FPGA程序开发环境为QUARTUSII,按照自顶向下的设计方式,先根据整体设计方案定义顶层功能块,分析构成顶层模块的必要的子模块,即将系统分为MAX2769射频模块、数据转存模块和USB数据传输控制模块三个子模块;然后进一步对各子模块进行分解,得到无法进一步分解的数据发生模块、串行外设接口SPI(Serial Peripheral Interface)模块、数据转存模块、PLL模块和USB控制模块五个底层功能块,分块之后的结构如图4所示。分块完成后采用Verilog HDL语言编写底层功能块,将底层功能块生成原理图,最后整个程序采用原理图方法进行综合设计。

图4 自顶向下分块结构图

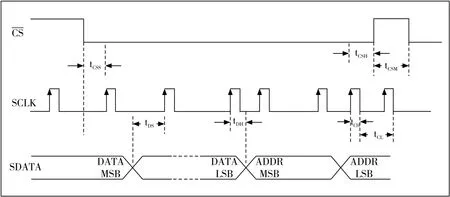

FPGA的软件工作:①首先通过SCLK、CS和SDATA三个接口对射频前端进行配置,可以应用电平配置实现GPS/GLONASS/Galileo卫星信号的接收或经过SPI协议串行配置接收北斗卫星信号,完成多种GNSS系统的中频数据接收。MAX2769的串行配置时序如图5所示。②将接收到的2位串行数据经缓存转换成16位并行数据传输到USB的16位并行数据总线,实现输入输出数据速度的匹配。③USB的控制同样由FPGA完成,采用Slave FIFO从机方式实现FPGA对USB芯片的控制。异步Slave FIFO写FPGA控制进程如下:

IDLE:当写事件发生时转到状态1。

状态1:指向端点2,激活FIFO ADR[1:O],转向状态2。

状态2:如果FIFO满标志为“假”(FIFO不满),则转向状态3,否则停留在状态2。

状态3:传送总线驱动数据。为一个IFCLK激活SLWR,转向状态4。

状态4:如果有更多的数据要写,则转向状态2,否则转向IDLE。

USB的异步写状态机如图6所示。

2.2 USB固件程序

图5 MAX2769串行配置的时序图

图6 状态机设计:异步FIFO写

固件程序主要是指配置接收机数据传输系统的微控制器的程序。对于开发的不同固件程序,接收机数据传输系统的传输方式、传输带宽甚至对应的上位机应用程序都可以不同。固件程序本身只负责配置硬件的工作方式,例如设备描述符信息、设备类别、接口配置、对于特定终端的响应函数等等。上位机在设备枚举时获取设备描述符,进而获得设备的配置信息和相关的驱动信息。用户可以通过修改固件描述符来改变设备特性[5]。

Cypress公司为FX2系列产品提供了固件框架和固件库,它们是由Keil C51 C编写的。固件框架和固件库提供了能够完成USB设备基本功能需求的参数和函数,如宏、框架函数、常量、USB数据结构等等,主要包含设备初始化、处理标准的USB设备请求以及USB挂起时的电源管理等基本功能,用户利用该框架提供的结构函数,可以完善各函数的功能,开发出适合于设计需求专用的USB设备。

本设计中,采用FPGA作为外部主控制器与USB芯片进行通信,并工作于从属FIFO模式。选用高速传输端点EP6,USB芯片在复位后,它的I/O引脚配置在“端口”模式下,而不是Slave FIFO模式。为将引脚配置为Slave FIFO模式,IFCONFIG寄存器的IFCFG[1:0]必须设置为11,因为USB芯片的FIFO工作在异步方式下,ASYNC位必须设置为1。选择EP6与FD总线连接,在对该端点的设置上选择块传输,4倍缓存,端点缓冲区大小为512字节,所以EP6CFG设置为0xe0,端点FIFO每512字节会自动打包上传,那么EP6FIFOCFG设置为0x0d。为了对数据传输进行控制,需要对该端点的标志位进行设置,通过FPGA向EP6的端点FIFO写数据,FLAGB变低电平就表示FIFO为满,此时不能再往里面写数据了[6]。

数据包的大小为512字节,需要设置EP6AUTOINLENH=0x02,EP6AUTOINLENL=0x00。通过上位机软件可以读取USB端点FIFO数据,然后保存到硬盘文件中,供后续处理。

2.3 上位机程序

应用程序不仅要能实现系统的既定功能,还要简洁和美观。本论文中的上位机应用程序采用VC6.0软件,基于MFC界面设计,调用Cypress公司的CyAPI.lib封装库编写的基于对话框的单线程程序。上位机主要是完成数据的传输以及校验,确保数据传输过程正确无误,同时还要实现传输的即时性、灵活性以及简单明了的界面信息显示。目前上位机可以即时传输数据,通过设置实现任意时间长度的数据传输。它还具有校验功能,如果数据传输过程出现了错误,则停止传输并发出警告。同时,它还可以实现USB设备的设备描述信息以及传输模式、传输大小、传输方式等具体信息的捕获显示。

上位机程序通过I/O控制调用来访问EZUSB通用驱动程序。上位机程序首先通过调用Win32函数CreateFile()来获得设备驱动程序的句柄,然后使用Win32函数DeviceIoCont rol(),通过CreateFile()函数返回的句柄,将I/O控制代码和相关的输入输出缓冲区提交到驱动程序。图7为整个数据采集和处理过程的流程图。

图7 数据采集和处理过程流程图

3 实验与验证

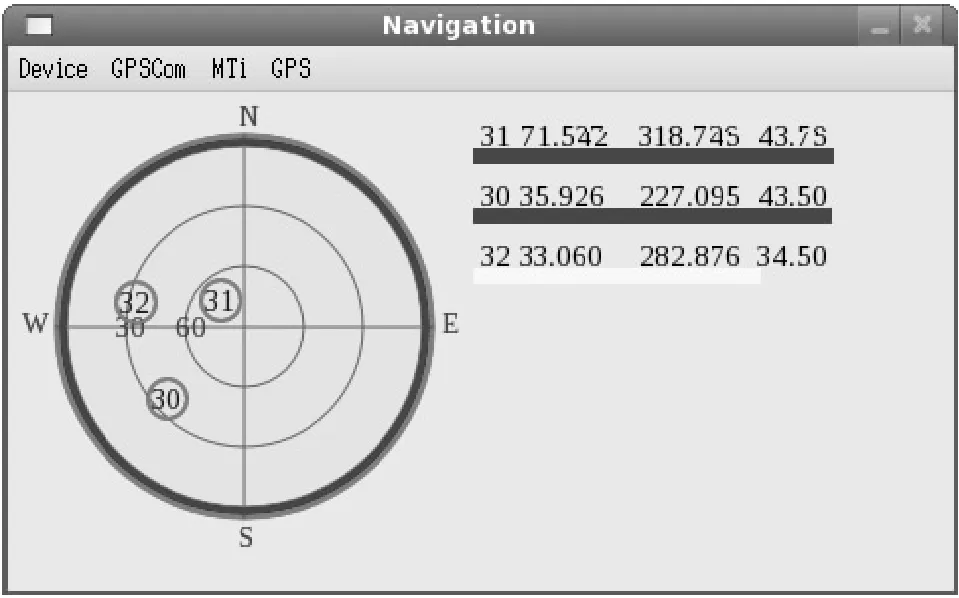

为了验证本文系统的功能,在哈尔滨工程大学三乙实验楼接收了GPS信号,并对其做了初步处理,应用MATLAB对中频信号的频谱和功率谱做了分析,同时进行了捕获验证,捕获方法为串行捕获[7,8]。得到的结果如图8所示。图9为NovAtel SS3-1CPT OEM(Original Equipment Manufacturer)版接收机在同一时间同一地点检测到的结果。经过对比,本文系统检测到的GPS卫星数量及卫星号与NovAtel SS3-1CPT的捕获结果一致,分析频谱和功率谱可以看出可捕获信号强度足够,说明该GNSS中频信号采集器采集的数据能够满足后续信号处理要求。

图8 实时GPS信号接收与后处理验证

图9 NovAtel SS3-1CPT检测结果图

4 结束语

本文设计的GNSS中频信号采集器实现了导航卫星信号的中频信号接收、传输和保存等功能,完整保存了GNSS中频数据,且数据质量满足后续信号处理的要求,为GNSS中频信号捕获和跟踪算法的研究提供了可靠的原始数据,为推动卫星导航接收机技术的发展和多系统兼容接收机的实现奠定了基础。

[1] 王 轲.单频GPS软件接收机通用硬件平台的设计与验证[D].武汉理工大学,2010,11~29.

[2] 胡 辉.基于USB2.0的GPS中频数据采集器研制[J].河南师范大学学报(自然科学版),2012,(5):56~57.

[3] 贺 喆.USB2.0 GNSS软件接收机设计与实现[D].上海交通大学,2009.

[4] 严 伟.GPS中频信号采集与捕获技术研究[J].东南大学学报,2009,(6):76~78.

[5] 赵 琳,丁继成,马雪飞.卫星导航原理及应用[M].西安:西北工业大学出版社,2011.

[6] 谢 钢.GPS原理与接收机设计[M].北京:电子工业出版社,2009.

[7] Tsui,J ames Bao-Yen.Fundamentals of Global Positioning System Receivers:a Software Approach[M].John Wiley&Sons,Inc.,2000,573~576.

[8] Soon Lim,Deok Won Lim,Meilin Liu,Seung Wook Moon,Chansik Park,Sang Jeong Lee.Design of a Software-based Multi-channel GNSS IF Signal Generator[J].Control,Automation and Systems,ICCAS,2008,754~758.

Design of GNSS IF Signal Collection Platform Based on FPGA and USB

Zhao Lin, Wang Ye, Ding Jicheng

The general GNSS IF data collection is designed with MAX2769 RF chip and classic high-speed data acquisition platform of FPGA+DSP as the core.The IF signal of GNSS satellites can be received and converted into digital IF data.By writing the control programs of USB device and man-machine interface programs in PC,the high-speed data acquisition,transmission and saving of IF data are achieved.The frequency spectrum is analyzed and the signal is captured with the received data.The experimental results show that the GNSS IF data can be saved correctly and completely by using the IF data collection developed in this paper.And the data can satisfy the positioning requirement.

GNSS; IF data; FPGA; USB

V249.32

A

CN11-1780(2014)02-0019-06

赵 琳 1968年生,工学博士,教授,博士生导师,研究方向为惯性导航技术、卫星导航技术、组合导航技术、信息处理与计算机仿真。

国家自然科学基金资助(编号:61273081,61304234)

2013-12-03

王 野 1988年生,在读工学学士,硕士研究生,研究方向为卫星无线电导航技术,组合导航技术。