基于TDR的测试系统管脚时间同步测量方法*

(武汉数字工程研究所 武汉 430074)

基于TDR的测试系统管脚时间同步测量方法*

顾翼石坚

(武汉数字工程研究所 武汉 430074)

随着数字电路测试系统测试速度的不断提高,测试周期越来越短,测试系统本身各种时间参量上的指标也随之不断提高。高端系统的边沿置放精度已经能达到百皮秒级。为了更准确地评估测试系统时间参量上的性能,分析了数字集成电路测试系统管脚时间同步误差形成的原因,并介绍了一种以时域反射技术(TDR)为基础的解决方法。

管脚时间同步精度;时域反射技术;传输延迟

ClassNumberTP20

1 引言

随着集成电路行业快速发展,芯片的集成规模不断扩大,工作速度也不断提高。芯片工作速度的提高要求芯片的时间参量上的误差减小。而对于数字电路测试系统,随着时钟频率即工作频率的不断提高,其时间定位精度也要提高。提高数字集成电路测试系统的时钟主频一方面能满足DUT(Device Under Test,待测芯片)不断提高的工作速度的要求,另一方面能缩短芯片测试所需耗费的时间,提高测试效率。一般情况下,数字集成电路测试系统主时钟在100MHz我们都称其为高速系统。例如泰瑞达公司的J750EX集成电路测试系统,时钟主频100MHz,测试频率最高可达200MHz。安捷伦的V93000SOC集成电路测试系统时钟主频高达800MHz,工作速度能达到3.2Gbps[1]。工作速度的提高意味着测试图形有着更短的上升时间和下降时间,同时单个测试向量周期减小。J750EX为例,实测其1.5V阶跃信号的上升时间为1ns,在最高速下向量周期为5ns。低速测试系统中向量周期往往在50ns或者100ns,有充足的时间等待测试通道的测试信号达到稳态,可以忽略通道内部信号传输的过程和信号建立的暂态过程。然而在高速系统中,我们要考虑两个方面的时间问题:信号完整性和时间同步性[2]。本文所讨论的就是如何解决时间同步的问题。

2 管脚时间同步精度(pins time synchronization accuracy,PTSA)

2.1 管脚时间同步精度的概念

如同数字集成电路在时序逻辑设计的时候要考虑门延迟以避免竞争和冒险一样,数字集成电路测试系统也要考虑加载到DUT上每个pin(管脚)的测试向量的时间同步问题。如果pin和pin之间的时间同步性很差,比如,本应在同一时间到达pin的两个信号由于时间不同步,最后到达时间相差了5ns,这有可能使DUT出现错误的逻辑输出,导致DUT测试失败[3]。

我们对管脚时间同步精度作如下定义:

数字集成电路测试系统的所有通道在t0时刻同时发送某一相同信号,每个通道信号到达pin上的时间总会有先后。假设信号最早到达pin的通道其到达时间ts1,最晚到达pin的通道为ts2;然后DUT所有的pin在t0时刻同时发出同一信号,假设各个对应通道中收到信号最早的通道测得信号时间为tr1,最晚为tr2,那么max{|ts2-t0+tr2-t0|,|ts1-t0+tr1-t0|}就是数字集成电路测试系统的管脚时间同步精度。

管脚时间同步精度作为一个时间参数,是对数字集成电路测试系统进行检测校准时的一个重要指标。其主要要素体现在三个方面:系统所有通道发送信号到达pin的一致性,每个通道测得pin上同一信号时间上的等时性,以及通道在信号发送和接收之间的及时性。

一致性要求所有的通道同一时刻发出的信号能同一时刻到达pin。

等时性指的是每个通道测得同一时间由pin上发出的信号的时间值是相等的。

海康威视是领先的视频产品和内容服务提供商,面向全球提供领先的视频产品、专业的行业解决方案与内容服务。海康威视是全球视频监控数字化、网络化和高清智能化的见证者、践行者和重要推动者。

及时性反映的是任意两个通道在pin端互联,在减去pin与pin之间的连线的延迟的情况下,一通道发信号另一通道收,收信号的通道测得信号的时间值就是信号在另一通道发出时的时间值。

2.2 管脚时间不同步所导致的问题

管脚时间不同步最直观的表现就是在测芯片的时候,每个通道同一时间发出的信号到达DUT上的时间总是不一样,总不能按照预期的时间到达。而且有时候会在正确的测试程序下出现错误的逻辑,但又不是芯片的原因。并且在用不同的通道测同一个DUT某一管脚的输出信号的时间也不一样。这些现象都是前面所说的一致性和等时性、及时性的问题。

国外高端测试系统生产商对于管脚时间同步精度问题研究相对来说比较成熟,有完整的理论和可靠地技术从内到外很好地解决这个问题。在国内,在这一领域的研究较少。

2.3 管脚时间不同步的原因

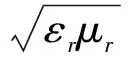

对于不同的数字集成电路测试系统来说,其结构可能有细微区别,但测试通道模型均可如图1所示。

图1 测试通道模型

控制信号到达通道的发送端,发送端开始发出测试信号,测试信号通过传输通道和DIB(Device Interface Board,器件接口板)最后到达DUT。但是控制信号从控制模块发出到达各通道发送端的路径不一样,其在到达信号发送端之前所耗费的传输时间也不相同,导致控制信号并不是在同一时间到达通道的信号发送端。也就是说测试信号在从发送端发出的时候就不是同时的。对于信号的接收,虽然原理上与信号的发送有很大不同,但不影响我们也认为其同发送信号具有相似的问题。即当所有信号同一时间到达接收端时,接收端得出的结论并不是在同一时间收到的信号。这些都是由控制信号和测试信号在传输过程中所耗费的传输延迟造成的。换句话说:如果信号传输过程不需要时间,就没有这些问题。

考虑到这些传输时间延迟不可避免,因此生产商往往都把大量的信号产生,信号测量,数据处理等电路都集中在离DUT最近的测试头中。测试程序写好后要先导入到测试头中的存储器,所测的DUT的数据也是在测试头中第一时间处理。计算机只是作为一个人机界面用作编写程序和显示结果。并不像其在其它设备中那样往往扮演很重要的角色。大量的功能电路都集中在一起最直接的问题就是电磁兼容和散热的问题,还有成本的上升,这些都是高速测试系统必须付出的代价。尽管如此,仍不能根本消除测试通道的传输延迟以及延迟差异。

3 TDR技术及解决方案

3.1 TDR技术

TDR技术全称时域反射技术(Time Domain Reflectometry),是一门在时间域上通过对发射信号和反射信号的评估而确定被测系统的状态的一种技术[7],类似于雷达定位技术。

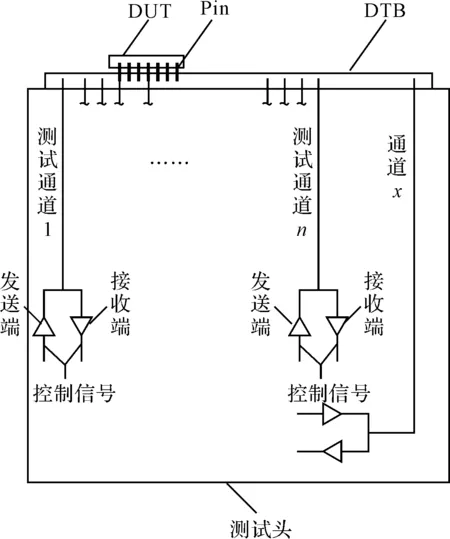

沿介质传播的能量遇到阻抗变化的界面时,一部分能量会被反射回去,其中反射能量的大小是入射能量和阻抗变化大小的函数;反射回来所用的时间是距离和传播速度的函数。因此,只要通过对照反射波和入射波形状的变化,并根据相应的理论就可以确定出待测系统的状态。这是TDR技术的基本思路。当阻抗变大的时候反射信号会是正值,与原信号叠加后回来的信号是一个大于原信号的值;当阻抗变小的时候反射信号会是负值,与原信号叠加后回来的信号是一个小于原信号的值。比较极端的两种情况:1)终端开路,阻抗无穷大,反射信号为原来两倍。2)终端短路,阻抗为0,反射信号与原信号抵消[8~9]。

图2[10]是TDR测试的原理,阶跃信号发生器向被测系统产生一个正向的阶跃信号。该信号沿着传输线向前传输。如果负载阻抗等于传输线的特性阻抗,将没有信号反射,示波器上能看到的只有发送的阶跃信号。假如负载存在失配,将有部分的输入信号被反射,示波器上将出现反射信号和输入信号的叠加[11]。

图2 TDR测试原理简图

3.2 基于TDR技术的时间同步测量方法

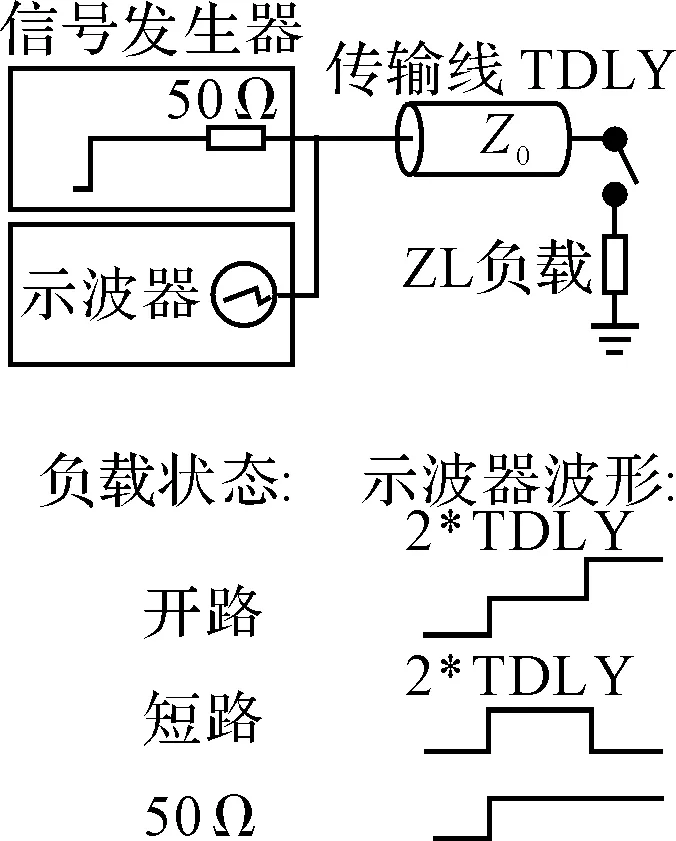

测试通道组成结构如图3所示。多数数字电路测试系统每个通道在距离信号收发端都有一个Relay,或称之为开关,其作用是在收发信号和PPMU(Per Pin Parametric Measurement Units,精密测量单元)之间切换,以完成不同的功能。一旦Relay处于OPEN状态,其开路特征明显,阻抗为无穷大,同时与所在通道上传输线50Ω特性阻抗失配,是一个很明显的信号反射点。当测试系统发送阶跃信号沿着传输通道传播,到达处于OPEN状态的Relay位置时会有一个相同幅度的阶跃信号反射。反射的阶跃信号与原信号叠加会产生一个幅度为原信号两倍的阶跃信号向原信号相反的方向传播,最后到信号返回到发送端被接收时的时间间隔就是该通道的双倍传输延迟。这就是利用TDR技术测延迟,每一个测试通道都具有这种TDR测延迟的能力。

图3 测试通道结构

Relay的存在对于时间同步测量的另一个好处是测试通道以Relay为界将通道传输延迟分为两部分:信号发送端、接收端到开关的传输延迟和Relay到DUT的传输延迟。前一段延迟固定不变,将会在测试系统的周期校准的时候进行校准,平时使用的过程中不需要校准,我们可称其为固定传输延迟。而后一段延迟会因使用者测试需要更换不同的DUT夹具或者更换DIB而产生变化,这段延迟可以根据需要在任何时候进行延迟校准,我们称其为可变传输延迟。

首先我们对固定传输延迟进行测量。我们需要将参差不齐的通道发送信号时间基准以某一通道X作为参考进行基准对齐。这个通道X一般是一个额外通道,独立于测试通道之外的,专门用于自校准的通道。对于没有独立通道x的测试系统理论上也可用某一测试通道代替独立通道x。通道x同普通的测试通道一样具有TDR测通道传输延迟的能力。通道x根据需要连接待测通道n,通道x发阶跃信号,待校通道n收信号,收到信号的时间为tnr。通道x再利用TDR技术测量通道x到待测通道n上的Relay之间的传输延迟tnp。得出待测通道n接收信号的一个修正值-(tnr-tnp)。将该值修正到待测通道n的接受信号时间里面,就意味着以通道x为参考,待测通道n能无延迟地收到通过待测通道n的Relay的信号。简而言之就是只要信号到达通道n的Relay的时候通道n就立刻收到了信号,因为在时间上消除了通道n的Relay到信号接收端的时间延迟。对其它每个通道都按照通道n的方法,将所有通道上的Relay到通道信号接收端的延迟消去之后,同时到达任意通道上Relay的信号都能被所在通道同时接收,所测时间相等。

测试通道信号发送端到Relay的延迟可能与信号接收端到Relay的延迟数值上有细小差别,但是测量原理完全相同,只是将通道x发信号改成了收信号,待测通道n收信号改成发信号。

这两部分工作完成以后就完成了固定传输延迟的测量。如前所述,这些工作主要是在测试系统校准时完成的。一旦该工作完成,这部分延迟的数据在下一个周期校准之前不会更改,也没有必要更改。

然后我们对可变传输延迟进行测量,也就是Relay到DUT上pin这一段的传输延迟。测量这段延迟的时候我们需要使测试通道没有加载DUT,目的是让通道末端处于开路高阻状态从而有利于形成明显的测试信号反射点。测试通道n发送阶跃信号,遇到终端开路的反射点之后沿原路返回,这一去一回的时间为2tnd,tnd即为通道n的可变传输延迟。根据测得tnd,对各通道n发送信号时间进行提前tnd,对收到信号的时间修正-tnd即可以消去通道n的可变传输延迟。其它通道测量方法均相同。

如之前所述,可变传输延迟的值tnd会因更换DUT夹具或DIB而改变,因此该延迟可以根据使用者需要随时进行测量修正。

以上所有工作完成以后,相当于将各通道的收发端移到DIB上的通道末端了。基本实现了信号到达DUT时间无滞后,DUT上的输出信号无延迟的被通道接收。这里所说的“发送信号无滞后”,“接收信号无延迟”并不是说信号传输过程不存在了。固有的传输延迟依然存在,但是通过对DUT发送信号的时间进行提前,接收信号的时间进行修正,使得在DUT看来信号总是无延迟的到来,DUT的输出信号又是及时的被收到。

4 结语

还有一种解决时间同步性问题的方法,可以称其为外部校准法,在国内厂商生产的数字集成电路测试系统上应用很广。其主要思路是从外部着手,而不管系统内部各通道之间的各种差异。利用外部辅助测量设备直接在DIB上测量所有pin上本应同时到达脉冲信号的真实到达时间差异,将其差异一次性修正到测试通道信号发送端。同样的各通道测量同一时间发出信号的时间差异也是一次性修正到测试通道信号接收端。这种测量方式耗时多,工作量大,所以这些修正值一旦写入系统后一般不会更改。且不说各测试通道自身传输延迟是否经过测量修正,即使是修正了,但由于其忽略了可变传输延迟的可变性,一旦使用者根据测试需要更换了DUT夹具或者DIB,将会导致各通道之间的传输延迟引入新的差异。这个差异会以误差的形式引入到测量结果中,降低测试的可信度。所以该方法具有明显的局限性。

反观TDR技术修正传输延迟解决时间同步性的方法,是根据测试系统内部结构利用测试系统部分电路结合TDR技术从系统内部开始,由内到外修正传输延迟解决时间同步的问题。由于不需要外部设备测量,且方法简单有效,耗时很少,测量效率明显高于外部校准法。另外还可以根据使用者需要,随时进行时间同步的校准工作,从而有效地保证了在不同的环境下测试系统的时间同步性。

对于测试系统利用TDR技术测量传输延迟的精度问题,笔者曾用一根长约1m的同轴传输线做实验。首先用泰克TDS8200带有TDR模块的示波器对同轴传输线进行TDR技术测延迟,测得其信号传输延迟值为4.8ns,可认为该值可信。然后再在J750EX数字集成电路测试系统上对该同轴传输线进行TDR技术测延迟,其结果为4.85ns,并且多次测量结果具有很好的重复性。

[1]沈森祖,韩红星,刘文捷,等.微电子计量测试技术[M].西安:西北工业大学出版社,2009:133.

[2]严简.借助时域反射技术检测集成电路的连通性[J].电子测试,2001,12(1):194-196.

[3]竹本浩志.Method For Calibrating TDR Timing of IC Test Apparatus[P].日本专利:2000009801,2000-1-14.

[4]陈伟.TDR探头设计及含水量和干密度的联合监测技术[D].杭州:浙江大学,2011.

[5]彭丽娟.时域反射仪的仿真研究与土壤介电特性的标定[D].武汉:武汉理工大学,2010.

[6]何小艇.高速脉冲技术[M].杭州:浙江大学出版社,1990:360.

[7]D. A. Robinson, S. B. Jones. A Review of Advances in Dielectric and Electrical Conductivity Measurement in Soils Using Time Domain Reflectometry[J]. Vadose Zone,2003,11(4):444-475.

[8]唐亮,赵春宇.时域反射(TDR)测试问题分析[J].电子测量技术,2008,31(5):42-44.

[9]David E. Dodds, Muhammad Shafique, Bernardo Celaya. TDR and FDR identification of bad splices in telephone cables[C]//IEEE CCECE/CCGEI, Ottawa,2006,5:838-841.

[10]Bernard Hyland.利用时域反射计测量传输延时[J].电子技术应用,2010(6):107-110.

[11]胡静,李新平,瞿伟廉.时域反射技术监测信号的复合小波函数分析[J].武汉理工大学学报,2008,30(6):88-90.

MeasurementofPinsTimeSynchronizationAccuracyatSemiconductorTestSystemBasedonTDR

GU Yi SHI Jian

(Wuhan Digital Engineering Institute, Wuhan 430074)

As semiconductor test system’s working speed increases, the test period becomes shorter, and the system performance indexs related to the time specs is lifted to a higher level. The time deviation of edge placement can be in 100 ps. In order to evaluate the capability of system’s time specs precisely, the sources of the error on pins time synchronization accuracy at semiconductor test system have been analyzed, and a measuring method based on Time Domain Reflectometry(TDR)has been introduced in this paper.

pins time synchronization accuracy, TDR, transmission delay

2013年11月9日,

:2013年12月24日

顾翼,男,硕士研究生,研究方向:微电子计量测试。石坚,研究员,硕士生导师,研究方向:微电子计量测试。

TP20DOI:10.3969/j.issn1672-9730.2014.05.034