并行缓冲控制器的模块级数据流结构设计

吴 将,朱志宇

(江苏科技大学 电子信息学院,江苏 镇江 212003)

并行缓冲控制器的模块级数据流结构设计

吴 将,朱志宇

(江苏科技大学 电子信息学院,江苏 镇江 212003)

针对并行缓冲控制器硬件实现困难的问题,在研究缓冲控制器结构的基础上,本文提出了一种粗粒度并行处理的可重构缓冲控制器的数据流结构设计方法,控制器由模块级流水线和传统的细粒度流水线合并组成,通过缓冲区实现了控制器与控制逻辑之间的隔离,因此,当正交全局信号对控制器进行局部配置时简化了系统集成度。

缓冲控制器;并行执行;流水线;模块级;数据流

模块级流水线是数据流模型的一种硬件实现方法[1-2],该方法的主要操作是在关联的控制器之间插入一个缓冲区,引入缓冲区的目的是为了减小缓冲控制器连接的模块之间的延迟和速率差等参数。应用模块级数据流可以实现以下3个要求:1)可以维持各个模块之间的并并行性,同时还确保各个模块之间同步执行准确性[3]。2)由控制信号、数据和时钟都是局部的,在保持性能的前提下,通过最小化时钟偏差和数据路由,使得硬件实现更容易。任何逻辑的改变只会影响其缓冲配置和控制器,因此可重构设计是可以实现的[4]。3)整个设计是围绕缓冲区的,因此,可以最小化内存和逻辑之间性能不匹配问题,本文主要是对缓冲控制器的生成和结构设计进行详细的阐述。

1 缓冲控制器设计

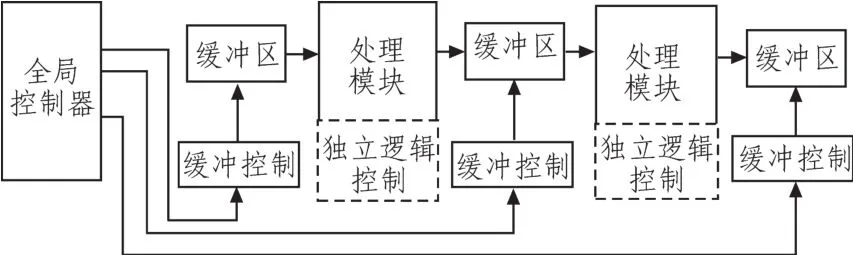

缓冲区(BUF)作为基本模块级流水线元素,这些缓冲区的读/写访问在同一时间进行,但是访问的位置不同,不同的读/写地址通过数据流的数据依赖关系进行确定。尽管读/写操作的位置不同,但是不存在地址冲突[5],同时还能保证模块间的并行性[6]。整体操作在逻辑上被视为只是缓冲区到缓冲区操作,通过引入处理模块逻辑实现的延迟来将各个模块进行隔离。数据路径是可循环的,如图1所示,通过逻辑操作隔离两个缓冲区引入延迟L后,BUFS的数据重新写入BUF1中。

图1 模块级数据流结构Fig. 1 Block-level pipelining structure

决定控制器结构的基本参数分别是逻辑延迟(Li)、地址偏移量(nri)和模块的大小(Mi)。Li是指进行处理的模块的延迟,该延迟是为了确保数据有效保存,Li的范围是0≤Li≤Lmaxi,其中Lmaxi是数据生成模块的维度。nri是写入缓冲区和读取缓冲区之间的偏移量,这个值实际上代表的是数据生成模块和数据使用模块之间的数据依赖关系。双向缓冲区[7]的nri值是指读写缓冲区之间的差异。Mi是指处理模块生成数据和处理数据的大小,这也决定了最大存储需求,最小缓冲区的大小为nri。在设计的初始阶段这3个参数生成静态数据流,实际的参数依赖于粗粒度处理模块和所使用的缓冲区的数量。全局控制和缓冲控制之间的相互作用的整体控制方案图如图2所示。

图2 控制器之间的相互作用Fig. 2 Interaction of the controllers

图3 缓冲控制器模块图Fig. 3 Block diagram of buffer controller

如图3所示为缓冲控制器的模块结构图,由图中可以看出缓冲控制器由以下一组关键信号控制:Clk,Reset,Enable,load,Lmaxi,Mi,nri。读写地址,读写缓冲区的使能信号和信号output都是缓冲控制器的输出,同时信号output还用于内部缓冲区控制。全局控制器通过start来启动每个缓冲区的操作,缓冲控制器基本上有3个计数器组成,它们分别提供读操作地址、写操作地址和nri。读、nri和写计数器的逻辑结构如图4所示,最初每个计数器装载的数值是计数器可达到的最大计算值(maxcount)。对于读和写计数器,有maxcount=Mi;而对于 计数器,有maxcount=nri。

图4 计数器逻辑结构Fig. 4 The logic structure of counters

2 特殊功能

由处理模块引入的用于缓冲控制器的延迟需要确保数据的时效性,如果不能确保时效性,数据流阶段无效的数据将会用于处理模块。从控制的角度来看,缓冲控制器需要知道无效数据的实际延迟Li(Li≤Lmaxi)。延迟处理模块的结构如图5所示。

虚拟缓冲区(VB)[8]在功能和结构上与缓冲区相似,但是其大小比缓冲区要小。当对一个大型复杂处理模块进行划分时,可以将VB用作流水线元素。在这种情况下,由于读写是分隔开来进行的,所以有nri=1。保持虚拟缓冲控制器和缓冲控制器结构相似,但是为了实现异步操作,需要使用独立的时钟实现读写操作。虚拟缓冲控制器的结构如图6所示。

图5 延迟处理模块结构Fig. 5 Structure of latency handler

图6 虚拟缓冲控制器结构Fig. 6 Structure of virtual buffer control

3 结 论

文中提出了一种粗粒缓冲控制器的数据流结构生成方法,同时还提出了并行处理的缓冲控制器的可重构模块级数据流设计方法,该控制器能够对本文提出的模块级流水线和传统的细粒度流水线进行合并,该方法还能够对控制器的缓冲区和控制逻辑进行隔离。尽管控制器是由局部信息生成的,但是该方法能够简化控制器的系统集成度。

[1]李浪.一种数据流异常并行挖掘算法[J].科学技术与工程,2008,8(23):6368-6375.

LI Lang. Outlier flow of data parallel mining algorithms[J].Science Technology and Engineering,2008,8(23):6368-6375.

[2]Guang R.Gao,Rene Tio.Instruction set architecture of an efficient pipelined dataflow architecture[J].IEEE,1989:385-392.

[3]Hyunuk Jung, Kangnyoung Lee,Soonhoi Ha. Efficient Hardware Controller Synthesis for Synchronous Dataflow Graph in System Level Design[J].IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 2002,4(10):423-428.

[4]E.A,Lee D.G. Messerschmitt.Synchoronous data flow[M].Proceedings of IEEE,1987.

[5]肖凌,李之棠,王美珍.一种解决VPN应用中内部地址冲突的机制[J].计算机工程与科学,2010,7(32):8-12.

XIAO Ling,LI Zhi-tang,WANG Mei-zhen.A method for Resolveing the Collision of the Intranet IP Addresses in the VPN Applications[J]. Computer Engineering &Science,2010,7(32):8-12.

[6]周滨,谢晓霞,傅其祥,等.基于多DSP的高速通用并行处理系统研究与设计[J].电子设计工程,2012,17(20):175-179.

ZHOU Bin,XIE Xiao-xia,Fu Qixian,et al.Design of high-speed general parallel processing system based on multi-DSP[J].Electronic Design Engineering,2012,20(17):175-179.

[7]高王军,彭认灿,陈轶,等. 双向缓冲区算法及其在海图线状要素综合中的应用研究[J].测绘科学,2009,2(34):187-190.

GAO Wang-jun,PENG Ren-can,CHEN Yi,et al.The research of the double direction buffering algorithm and its application on the generalizing of chart linear feature[J].Science of Surveying and Mapping,2009,34(2):187-190.

[8]李杰,赵乘骥,赵乘麟.码率控制中的虚拟缓冲区自适应控制方法:中国, CN101568025[P].2009-10-28.

The block level pipelined dataf l ow design of parallel buffer controller structure

WU Jiang, ZHU Zhi-yu

(School of Electronics and Information,Jiangsu University of Science and Technology,Zhenjiang212003,China)

Based on the study of buffer controller structure and the problem of implementation for parallel buffer controller. This paper presents a new data flow design method of buffer controller with reconfigurable, coarse-grained parallel processing features. The controller which consists of the module-level pipeline and the traditional fine-grained pipeline, realizes the isolation of the control logic through using the buffer. Therefore, while the controllers are locally configured from orthogonal global information, the degree of system integration is simplified.

buffer controller; parallel execution; pipelining; block-level; data flow

TN911.7

A

1674-6236(2014)07-0054-03

2013-08-01稿件编号201308002

吴 将(1988—),男,安徽安庆人,硕士研究生。研究方向:系统仿真。