基于FPGA和以太网数据采集系统的设计及实现

李凛威,梅教旭,汪 磊,谈 图,高晓明

(中国科学院 安徽光学精密机械研究所 大气物理化学研究室,安徽 合肥 230031)

基于FPGA和以太网数据采集系统的设计及实现

李凛威,梅教旭,汪 磊,谈 图,高晓明

(中国科学院 安徽光学精密机械研究所 大气物理化学研究室,安徽 合肥 230031)

为了满足网络传输、可触发控制和多路信号采集的需求,设计和实现了基于FPGA和以太网接口的数据采集系统,其中以FPGA为核心,实现了AD驱动、触发控制、串并转换、FIFO缓冲和MAC配置。实验结果表明系统设计合理,可以达到预期功能,这对同类数据采集系统有一定的参考价值。

数据采集;触发控制;FPGA;以太网

近年来,基于近红外可调谐二极管激光吸收光谱技术的气体传感器得到快速的发展。在很多实际应用中[1],特别是对应于车载或机载应用环境,为保证较高的空间分辨率,需要连续实时地采集分析数据。人们通常利用普通商用采集卡连续采集光谱信号,然后再寻找特征吸收峰的位置。采用这种方式一方面相对耗时,影响采集速率,无法胜任长时间、不间断的应用环境;另一方面不停地寻找吸收峰位置,在弱吸收信号的情况下,会造成较大的测量误差,由于采集卡的连续采集,每次采集卡内存溢出,这会造成一定的数据丢失。利用触发控制信号提供采集信号的起始点,不仅保证采集数据的稳定,同时还能保证有选择地采集数据[2]。

目前商用的数据采集系统难以满足较高频率触发采集的需求,普通的商用采集卡很难达到100Hz的触发频率,导致丢失大量数据,影响探测仪器的准确性。目前市场上能够具有高速触发采集的采集卡很少,并且价格昂贵,难以及时做到维护和升级。

文中以FPGA为核心,设计了基于以太网接口的可触发控制的数据采集系统。FPGA具有高集成度,高速度和高可靠性等特点,时钟延时可达ns级,完全适用于数据采集系统的

实时性与可靠性要求;FPGA具有丰富的内嵌IP核,可以重复开发,降低设计难度,缩短开发周期,具有较低的开发成本;FPGA可现场编程,易于修改,可根据实际应用进行升级维护[3]。以太网传输技术相对于传统的传输技术,成本低廉,具有灵活性和较强的兼容性,利用双绞线或光纤作为传输介质可实现长距离高速传输。

1 总体设计

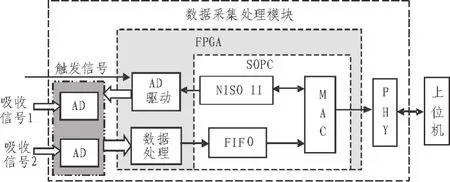

总体设计如图1所示,根据吸收峰的位置,在吸收峰到来之前给出触发信号。数据采集系统在触发信号上升沿到来时,启动两路AD同时对两路模拟信号进行采集,转换后进入FPGA,FPGA对数据进行处理并计数,然后进入FIFO缓冲,当采集固定点数的数据(包含吸收峰以及附近的一段数据),FPGA停止接收数据,等待下一次有效触发信号的到来。当FIFO缓冲的数据达到半满状态,取出数据并加入UDP协议后经MAC通过PHY将数据发送给上位机。如果置触发信号有效,并将计数功能关闭,可实现两路信号连续实时采集。

数据采集系统以FPGA为核心,设计采用的FPGA是Altera公司Cyclone III系列的EP3C10E144C8N。具有10 kbit逻辑单元、424 kbit存储器、23个18X18乘法器、专用外部存储器接口电路、锁相环(PLL)以及高速差分I/O等。Cyclone III 系列FPGA系列前所未有地同时实现了低功耗、低成本和高性能,进一步扩展了FPGA在成本敏感领域中的应用。AD器件采用的是TI公司的采样速率为250kSPS、16位精度串行输出的ADS8326。以太网收发器采用的DM9161CEP是一款完全集成的和符合成本效益单芯片快速以太网PHY

2 AD驱动与数据处理模块

ADS8326工作时序如图2所示。CS信号出现下降沿的时候,DCLOCK必须为低电平,同时CS下降沿距离DCLOCK上升沿至少为20 ns。CS信号下降沿到来时,经过5个DCLOCK的采样,在第7个DCLOCK上升沿,AD开始从最高位开始串行输出数据,转换完成后经过几个DCLOCK的Power Down,开始进行下一次转换。系统嵌入了32位的Nios II处理器,将两路1bit X 16串行信号转换成32 bit X 1的一路并行信号有利于数据的传输处理。同时对串并转换后的数据计数,保证触发控制的准确性。32位并行信号需要进入FIFO缓冲,因此还需要为FIFO提供使能信号以及时钟信号。用Verilog HDL硬件语言编写了AD驱动及处理模块,仿真时序如图3所示。

图1 数据采集处理系统Fig. 1 Data acquisition system

图2 ADS8326工作时序Fig. 2 ADS8326 timing information

图3 AD驱动及串并转换仿真时序Fig. 3 Driver and serial to parallel conversion timing simulation

其中clk为系统输入时钟,tr为外部触发信号,din0和din1为AD转换后的串行信号。wrreq和s_clk为FIFO的控制信号和时钟信号,dout为串并转换后的数据。从时序仿真图来看,时序和逻辑都符合设计思路,可以达到预期要求。

3 SOPC模块设计

在SOPC开发环境中可以方便的添加32位Nios II处理器、丰富的IP核以及用户逻辑等,并用Avalon总线将这些模块连接起来,同时还可以按地址访问以及添加中断。灵活易用的处理器和丰富的IP核简化系统设计,降低成本,缩短开发时间[4]。硬件主要包括Nios II处理器、存储器、异步FIFO、MAC模块和通用IO等。添加并连接好的SOPC系统如图4所示。

Nios II处理器内核是一个32位的RISC处理器,它具有共享的通用指令集结构,专门针对Altera的主流FPGA系列进行了优化。处理器负责数据和网络协议的处理。

On-Chip Memory是一块片上RAM,onchip_mem用于程序执行和数据存储,descriptor_mem用于SG-DMA的描述符存储器。

MAC(介质访问控制层)主要负责控制与链接物理层的物理介质,MAC模块调用了Triple-Speed Ethernet IP核,发送和接收用的是Avalon-ST接口,用户需要通过此接口对MAC内的接收FIFO和发送FIFO读写操作。MAC与外部PHY 使用MII/GMII接口进行连接,同时该模块可提供MDIO/MDC接口,对PHY管理[5]。

图4 SOPC硬件连接图Fig. 4 Hardware connection diagram

Scatter-Gather DMA可根据描述符命令,将非连续的内存空间的数据传输合并到连续的存储空间。SG-DMA支持数据流到存储器,存储器到数据流以及存储器之间的传输。Avalon总线采用的是Avalon-MM接口,与MAC的Avalon-ST接口不能直接连接,采用了sgdma_tx作为MAC发送通道,sgdma-rx作为接收通道。SG-DMA在完成当前任务后,会根据描述符命令自动提取命令字开始新的任务,减少了CPU占用[6]。

DATAin是用户逻辑,让AD转换后的数据进入SOPC。

异步FIFO用于存储和缓冲数据,同时可为DATAin提供Avalon-ST接口。

此外还添加了JTAG-UART、SYSID等。

4 软件设计

在Nios II IDE集成开发环境中可以用C语言完成Nios II处理器的软件设计。软件设计流程如下,首先对个模块初始化,上位机发送采集控制信号,系统开始信号采集。数据处理模块将处理后的32位数据送入异步FIFO中,当FIFO半满时产生中断,将数据取出并加入UDP协议,并启动SG-DMA将数据传送到MAC中,最后经以太网发送至上位机处理。

图5 Nios II主程序流程图Fig. 5 Main program flow chart of Niso II

UDP协议并不提供反馈检测,因此UDP协议并不可靠,需要其他手段保证传输的可靠性。但正是由于UDP不建立连接、撤销连接、确认报文等开销,保证了数据传输的实时性和高效性,这也是它在实际网络尤其是实时数据传输网络中广泛应用的主要原因[7]。在误差允许范围内,UDP可以满足实时传输的要求,本设计采用UDP/IP协议作为以太网传输协议。

5 系统测试

数据采集系统设计完成后,还需实际测试来验证可行性。数据采集系统通过以太网接口将数据发送至上位机,PC机利用Labview编写的程序对数据进行存储和显示。

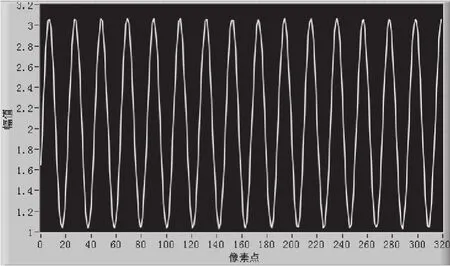

连续实时采集模式。函数信号发生器产生10 K的正弦波作输入信号,采集系统采样频率为208 K。根据采样定理,采集系统可以完整恢复正弦信号,一个周期平均应该采样20.8个点。实际采集图像如图7所示,与预期结果一致。

图6 连续实时采集图Fig. 6 Continuous real-time acquisition waveforms

图7 外部触发控制采集Fig. 7 External trigger control data acquisition

开启触发采集功能,利用函数信号发生器提供方波信号和正弦信号作为测试信号,正弦信号和方波信号具有相同的频率和固定的相位差,如图7(a)所示。方波信号频率为200 Hz,模拟触发信号,标记信号采集的起始点,表明后面的信号是需要采集的信号。触发信号上升沿时开始采集,采集320点后停止采集,将采集到的数据打包发送到上位机,等待下一次触发信号上升沿继续采集。上位机显示波形如图7 (b)所示,是一个稳定的波形。同时利用Wireshark网络抓包工具对数据包进行分析,测试时间3 300 s,获得数据657 545帧,平均每秒199.26帧数据,与200 Hz的触发频率基本吻合。实验结果与预期一致。

6 结 论

基于FPGA[8]和以太网[9]两种技术,设计了两路信号的可触发同步采集以及连续实时采集系统,解决了其它采集系统难以有效触发采集的问题,同时采用了通用的以太网接口传输数据。系统测试结果表明该采集系统可以达到200 Hz的双路触发采集,表明设计的合理性与准确性。此数据采集系统还可根据实际应用进行升级维护,具有广泛的应用前景。

[1]汪磊,谈图,曹振松,等. 车载天然气管道泄漏遥感探测技术的研究[J]. 光谱学与光谱分析,2010,(8):2192-2195.

WANG Lei,TAN Tu,CAO Zhen-song, et al.Research on Vehicle-Based Remote Sensing of Natural Gas Pipeline Leakage[J].Spectroscopy and Spectral Analysis,2010,(8):2192-2195.

[2]毕韬. 基于ARM和FPGA的高速数据采集卡的设计与实现[D].长春:长春工业大学,2010.

[3]吴继华,王诚. Altera FPGA/CPLD 设计 [M]. 北京 : 人民邮电出版社,2005.

[4]陈长胜,李大鹏,王建宇. 基于Altera SOPC技术的嵌入式以太网终端设计[J]. 航空计算技术,2008,(5):81-84.

CHEN Chang-sheng, LI Da-peng, WANG Jian-yu. Design of Embedded Ethernet Node Based on Altera SOPC Technology[J].Aeronautical Computing Technique, 2008,(5):81-84.

[5]韦宏,付友涛,孔凡鹏,等. 基于FPGA的千兆以太网设计[J].现代电子技术,2012(18):56-59.

WEI Hong,FU You-tao, KONG Fan-peng, et al. Design of gigabit Ethernet system based on FPGA[J]. Modern Electronics Technique, 2012(18):56-59.

[6]梁艺,周卫星. 基于SoPC的视频监视器千兆网显示接口设计[J].电子技术应用,2009(8):12-15.

LIANG Yi, ZHOU Wei-xing. The design of video monitor Gigabit Ethernet display interface based on SoPC[J].Application of Electronic Technique,2009(8):12-15.

[7]龚少波. 基于FPGA的网络传输设计与实现[D].哈尔滨:哈尔滨工程:大学,2012.

[8]陈亮,刘金学.基于DSP和FPGA的导航计算机系统设计[J].现代电子技术,2012(2):1-3,6.

CHEN Liang,LIU Jin-xue.Design of navigation computer system based on DSP and FPGA[J].Modern Electronics Technique,2012(2):1-3,6.

[9]沈豪敏,张 涛,王 健.基于DM9000A的DSP以太网接口设计与实现[J].现代电子技术,2013(24):140-143.

SHEN Hao-min,ZHANG tao,WANG Jian.Design and implementation of DSP Ethernet interface based on the DM9000A[J].Modern Electronics Technique,2013(24):140-143.

Design and implementation of a data acquisition system based on FPGA and Ethernet

LI Lin-wei, MEI Jiao-xu, WANG Lei, TAN Tu, GAO Xiao-ming

(Laboratory of Atmospheric Physico-Chemistry,Anhui Institute of Optics & Fine Mechanics,Chinese Academy of Sciences, Hefei230031,China)

A data acquisition system based on FPGA and Ethernet to achieve network transmission, trigger control,and multi-channel signal acquisition has been designed and implemented. This system utilizes FPGA as the core chip to complete the AD driver, trigger control, serial to parallel conversion, FIFO buffering and MAC configuration.Experimental results indicate that the data-acquisition system designed is reasonable and can reach the desired functions. This work has a certain reference value for similar data acquisition system.

data acquisition; trigger control; FPGA; Ethernet

TN-923

A

1674-6236(2014)07-0001-04

2014-01-13稿件编号201401091

国家自然科学基金(41175036);中国科学院仪器设备功能开发技术创新项目(YG2011056)

李凛威(1991—),男,安徽合肥人,硕士研究生。研究方向:数字电路设计及数据采集与处理。