宽带微波本振源研究与设计

蒋开创, 何 波, 苏 坪

(上海无线电设备研究所,上海 200090)

宽带微波本振源研究与设计

蒋开创, 何 波, 苏 坪

(上海无线电设备研究所,上海 200090)

介绍了一种工作频段从Ku波段到K波段的宽带微波本振源的设计方法。首先对宽带微波本振源的关键技术进行了研究和分析,包括宽带跳频锁相环和多通道开关滤波技术;然后,运用ADIsim PLL锁相环仿真软件、HFSS高频仿真软件进行了相关部分的设计和仿真;最后,给出了测试结果及其分析。

宽带跳频;锁相环;多通道滤波

0 引言

频率源是通信、雷达、空间电子设备和电视等电子系统的心脏,其性能好坏将直接影响系统的性能指标。频率综合技术按所经历的发展来分类,大致可分为以下几个技术阶段:直接频率合成DS、锁相间接频率合成PLL、直接数字频率合成DDS、分数频率合成NPLL以及混合式频率合成等[1]。其中,锁相间接频率合成是目前最成熟且使用最为广泛的频率合成技术之一。

在各种地面、舰载、机载以及弹载检测雷达的使用中,许多雷达设备需要具备宽频段、小步进的跳频扫频性能。因此,高性能的宽带频率源是保证雷达系统能够在宽频带范围内稳定以及高性能工作的前提。

此外,现代宽带雷达系统的射频接收前端一般采用经典的超外差结构,即第一本振采用跳频本振,使得雷达系统能够在宽频率范围内进行扫描,并将接收到的射频信号下变频到固定的第一中频。因而,宽带雷达设备的频率源部分的研制工作主要是对作为第一本振使用的宽带微波本振源的设计与实现。

1 宽带微波本振源设计

宽带微波本振源主要由锁相环、倍频放大和开关滤波三个部分组成,其原理框图如图1所示。其中,锁相环部分将产生稳定的基波振荡信号,再通过倍频放大部分实现基波频率的倍频,最后通过开关滤波组来进行频率的选择与滤波。

图1 宽带微波本振源原理框图

由于频率输出范围大,杂散及谐波成分复杂,锁相环和开关滤波两个部分的设计与实现是研制宽带微波本振源的难点。

1.1 宽带跳频锁相

锁相环(Phase Locked Loop,PLL)是一种相位比较控制系统,通过比较VCO输出频率与参考频率的相位来达到提高VCO输出频率稳定度及降低相位噪声的目的。与直接频率合成和直接数字频率合成相比,锁相环技术具有杂散低、相位噪声好、体积小、成本低等优点。因此,在满足跳频时间和频率步进要求的情况下,锁相环技术是实现机载以及弹载宽带跳频源的理想选择。

宽带微波本振源由于输出频率范围大,若采用单个锁相环进行锁定,将造成环路锁定困难。因此,采取的解决方案是将本振源频率划为两段,分别由两个不同的宽带VCO来产生所需频率,然后再通过TTL电平控制选通开关来选择输出频率及相应的锁相环路,其原理框图如图1中锁相环部分所示。

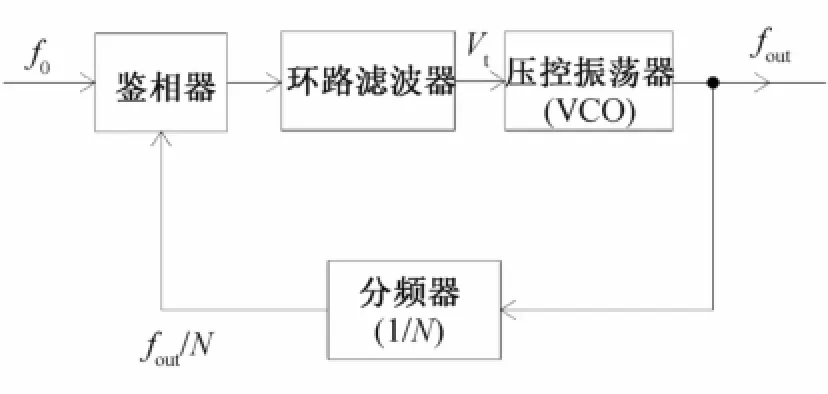

在根据TTL电平选择好锁相环路之后,本振信号的产生问题就是单个锁相环的锁定问题,因此分析方法与单锁相环电路相同。单个锁相环电路的典型结构如图2所示,含有VCO、鉴相器、环路滤波器和分频器等元件[2]。

图2 锁相环原理框图

对于常用的数字锁相环,还可以通过数字鉴相器内集成的分频器对参考频率f0进行1/R的预分频,同时对fout/N射频信号再进行M分频,这样得到的输出频率fout与参考频率f0的关系:

因此,对于采用数字鉴相器的锁相环,通过单片机输出控制字来改变鉴相器的分频系数M,就能达到改变输出频率的作用,即实现跳频的功能。

在VCO、鉴相器及分频器选定之后,为了获得稳定的VCO调谐电压,需要进行环路滤波器设计。由于环路滤波器能够起到维持环路稳定性、控制环路带内外噪声、防止VCO调谐电压突变和抑制参考信号杂散干扰等重要作用,因此环路滤波器是锁相环设计与调试的关键。

常用的三阶有源环路滤波器,其结构如图3所示。通过在三阶无源环路滤波器的基础上,加入一个起到正向放大作用的运算放大器而构成,这样就能够解决鉴相器输出电压不足的问题。

图3 三阶有源环路滤波器

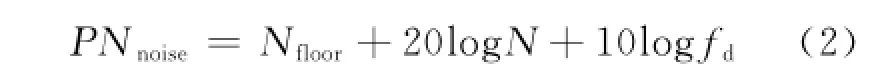

环路滤波器最重要的两个设计指标为相位裕度(Φm)和环路带宽(ωc),前者跟环路的稳定性有关,通常选取在30°~60°之间,而后者则在环路性能上有更重要的作用。选择小的环路带宽能更好地抑制鉴相频率泄露、减小调谐电压纹波以及改善近端相位噪声,环路带宽通常设定在PLL模块相位噪声和VCO相位噪声相等的频率点上来优化整个环路的相位噪声[3]。环路带宽内相位噪声的计算为

式中:Nfloor为鉴相器噪底;N为输出频率与鉴相频率的比值;fd为鉴相频率。目前常用的数字鉴相器,其归一化噪底能达到-219 d Bc/Hz。

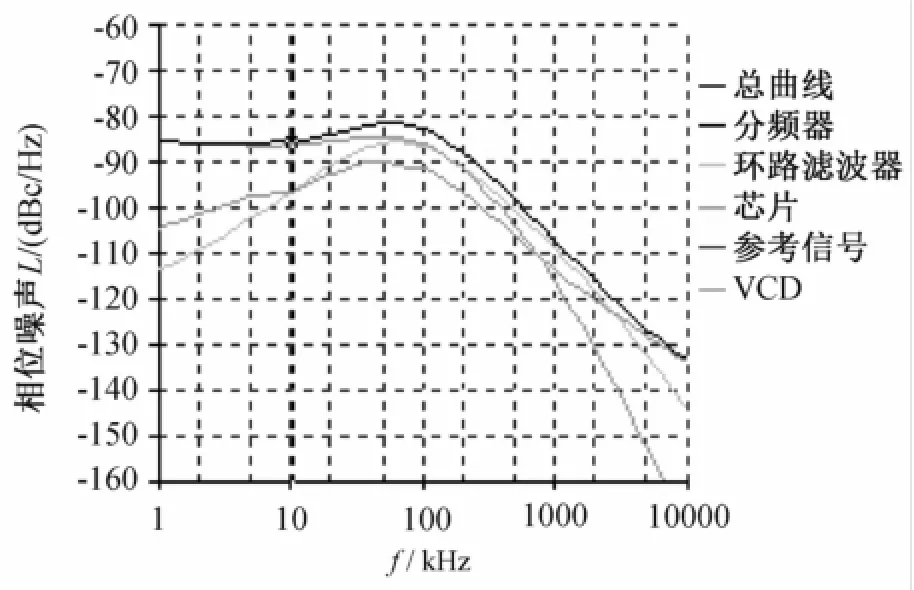

锁相环路整体的仿真采用ADI公司的ADIsim PLL软件,该软件能够根据用户选择的器件和输入的指标参数得出环路滤波器各个器件的数值及整体电路的仿真结果。由于电路结构相同,本文只介绍一路锁相环的仿真过程及结果。通过选择环路带宽(ωc)和相位裕度(Φm),并优化电容电阻参数,得到仿真结果如图4所示。

图4 锁相环相噪仿真结果

锁相环的设计中心频率为10.4 GHz,环路带宽和相位裕度分别为98 k Hz和56°。由图4仿真结果可知,在10 k Hz处的相位噪声为-85.4 dBc/ Hz。优化后的电容电阻值如表1所示。

表1 三阶有源环路滤波器电阻电容值

1.2 多通道开关滤波

由于该本振源是通过基波锁相结合倍频技术来产生所需的本振信号,而倍频器输出信号中除了二次倍频信号外,还含有基波以及三次谐波等高次谐波成分。因此,为了保证输出信号频谱的谐波及杂散满足设计指标要求,在输出本振信号前需要进行滤波。同时,由于设计频带宽,本振低端频率的高次谐波和高端频率的基波等杂散与本振信号存在频谱重叠的情况,单个滤波器无法满足整个宽带本振源信号的滤波要求。因此,需要在VCO划分频段的基础上,将倍频后的本振频率进一步划分为三个频段,前两个频段由第一个宽带VCO产生,第三个频段由第二个宽带VCO产生。

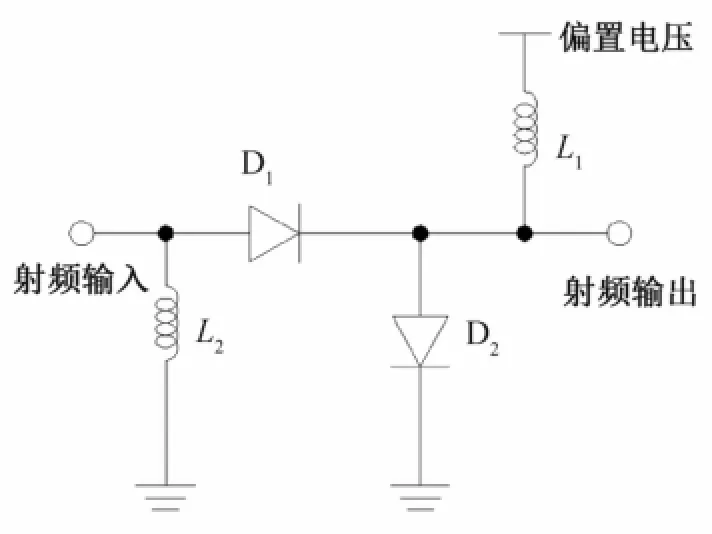

1.2.1 单刀三掷开关

开关滤波器组的研制是基于多通道滤波技术,主要包括带通滤波器和选择开关,其结构如图1所示。其中,射频开关为单刀三掷(SP3T)的串-并联结构PIN二极管开关,串-并结构能够增大开关的隔离度[4],其电路结构如图5所示。两个二极管之间的距离为λg/4,λg为射频信号波长。其工作原理:当电压偏置端加负电压时,二极管D1导通,D2截止,即开关导通;当偏置电压为正电时,D1截止,D2导通,即开关截止。

图5 串-并联PIN二极管开关结构图

1.2.2 平行耦合带通滤波器

在开关选通后,带通滤波器的性能好坏将直接影响信号频谱的纯度,因此带通滤波器的设计至关重要。其中,平行耦合微带带通滤波器由于具有插损小、矩形系数好和体积小等优点,被广泛应用在微波电路系统中。由于结构及设计方法相同,本文只介绍一路通道使用的带通滤波器的设计和仿真过程。

根据平行耦合带通滤波器的设计方法[5],首先要从归一化低通滤波原型着手,通过计算归一化频率,并根据选择的低通原型和指标要求确定滤波器的阶数;然后查表得到各元件归一化值,并计算耦合传输线的奇模、偶模特性阻抗,进而通过耦合线传输线的特性阻抗求得线宽、线长和耦合宽度等建模所需参数;最后,在仿真软件里建立模型,进行仿真优化。

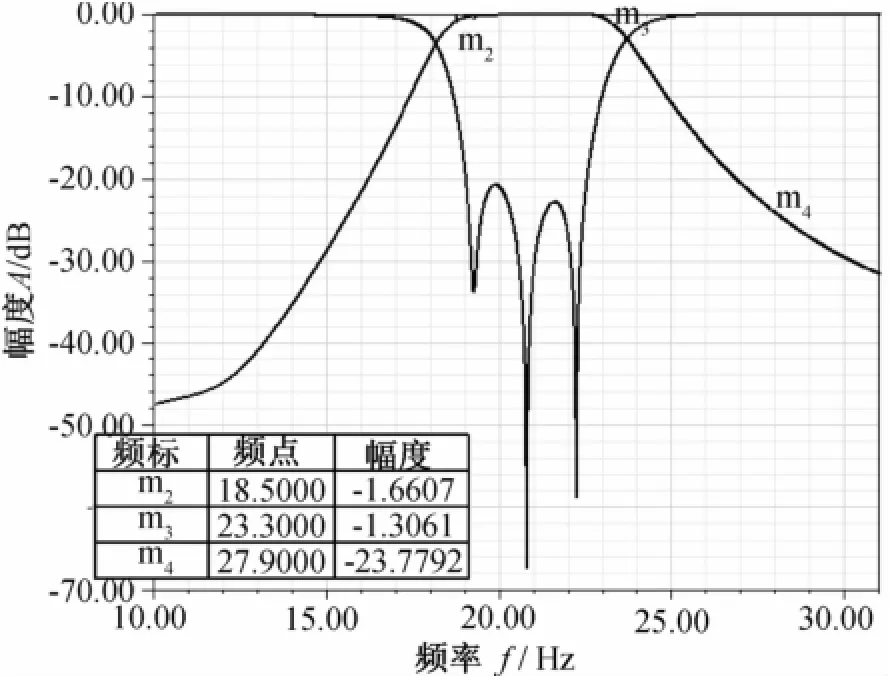

本设计中的带通滤波器,主要是为了滤除本通道内频率的基波、高次谐波分量以及低频段的杂散成分。由于离本通带最近的频率成分是三次谐波f=27.9 GHz,在设计时应保证此频率点处至少有20 dB的抑制度。因此,求得归一化频率为

式中:fc为中心频率;f为截止频率;fU为频率上边带;fL为频率下边带。

选取的低通滤波原型为具有0.5 dB带内波纹的切比雪夫滤波器,通过查询其衰减特性曲线可得,当滤波器阶数N=3时,可以满足f= 27.9 GHz处具有20 d B抑制度的要求。查表得相应的元件归一化值为g0=g4=1,g1=g3= 1.5 963,g2=1.0 967。

计算阻抗值前,首先需要求得归一化带宽BW=(fU-fL)/fc,然后根据式(4)、式(5)和式(6)分别计算奇偶模的特性阻抗值:

其中:

阻抗计算结果和对应在εr=9.8,厚度为0.38 mm陶瓷基片上的耦合微带线尺寸分别如表2和表3所示。

表2 耦合线奇偶模阻抗值

表3 平行耦合线模型初始尺寸

平行耦合带通滤波器的HFSS仿真模型及仿真优化结果分别如图6和图7所示。由仿真结果可知,在f=27.9 GHz处抑制度为23.7 dB,满足设计要求。

图6 HFSS仿真模型

2 本振源测试结果及分析

宽带微波本振源盒体采用了铝合金材料,其外形尺寸为115 mm×105 mm×20 mm。为了达到更好的电磁兼容效果,倍频放大和开关滤波两部分电路用可伐盒体进行封装。该本振源所达到的主要技术指标:

a)输出频率:Ku~K波段;

图7 HFSS仿真结果

b)频率步进:Δf=10 M Hz;

c)跳频时间:t<10 ms;

d)输出功率:P>10 d Bm;

e)杂散抑制度:ΔP>55 d Bc;

f)相位噪声:L<-68 dBc/Hz@10 k Hz。

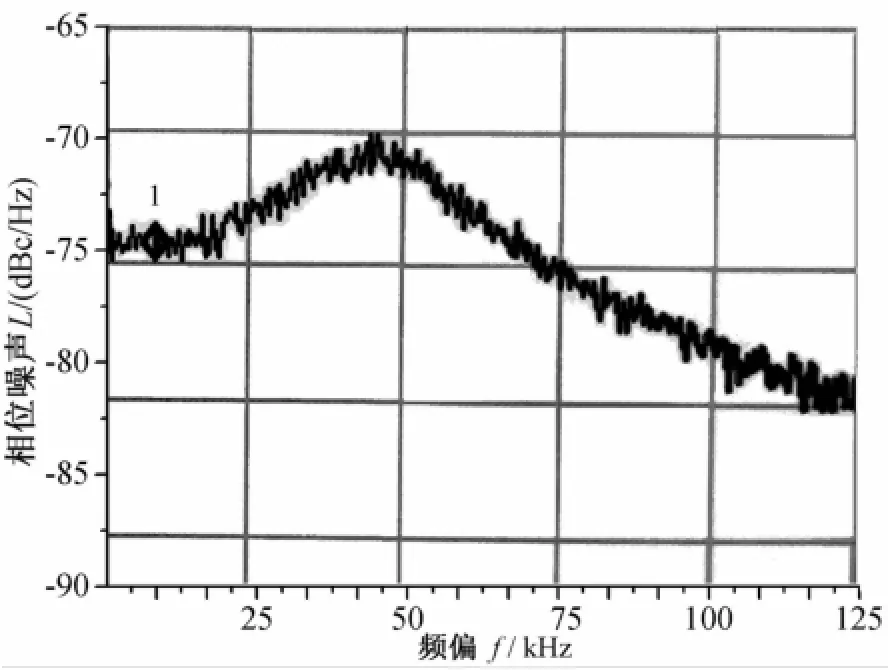

其中,典型相位噪声测试曲线如图8所示,频谱仪测试RBW=1 k Hz,所以10 k Hz处测得的相位噪声为-74.032 dBc/Hz。

3 结束语

本文介绍了一种宽带微波本振源的设计方法,通过采用基波锁相环结合倍频技术以及开关滤波技术,研制成功了一种Ku~K波段的宽带微波本振源。其性能指标满足使用要求,与同类产品相比较,该宽带本振源具有体积小、重量轻和工作稳定等特点。

图8 相位噪声测试结果

[1]何松柏,等译.频率合成原理与设计(第三版)[M].北京:电子工业出版社,2008.

[2]张厥盛,等.锁相技术[M].西安:西安电子科技大学出版社,1994.

[3]刘奡.宽带PLL环路滤波器的设计[D].南京:东南大学,2006.

[4]郑新,等译.微波固态电路设计(第二版)[M].北京:电子工业出版社,2006.

[5]陈黎,等.基于ADS的平行耦合带通滤波器设计[J].压电与声光,2012,34(3):483-486.

Research and Design of Wideband Microwave Local Oscillator

JIANG Kai-chuang, HE Bo, SU Ping

(Shanghai Radio Equipment Research Institute,Shanghai 200090,China)

A kind of design method of wideband microwave local oscillator(LO)operated from Ku band to K band is proposed in this paper.Firstly,the key technology of wideband microwave LOis studied and analyzed,including the technology of wideband frequency hopping phase locked loop(PLL)and multi-channel switched filters.Then,the design and simulation are taken placed in ADIsim PLL and HFSS.At last,the analysis and testing results are shown.

wideband frequency hopping;phase-locked loop;multi-channel filters

TN61

A

1671-0576(2014)01-0044-05

2013-03-18

蒋开创(1982-),男,工程师;何 波(1989-),男,在读研究生;苏 坪(1985-),男,助工,均从事微波电路与系统的研究。