基于FPGA的TV-VGA设计

李文联,危必波, ,吴一夫,彭新显,孙小兵

基于FPGA的TV-VGA设计

李文联1,危必波1, 2,吴一夫3,彭新显2,孙小兵2

(1. 湖北文理学院 物理与电子工程学院,湖北 襄阳 441053;2. 武汉工程大学 电气信息学院,湖北 武汉 430205;3. 利墨瑞克大学 电子计算机工程学院,爱尔兰 利墨瑞克)

基于Altera Cyclone IV E FPGA设计的TV-VGA转换控制器,采用Altera Cyclone IV E FPGA将DVD输入影像信号传输到DE2-115开发板电视译码芯片(ADV7180),经过译码转换成8位的ITU-R标准接口影像数据传输到Cyclone IV E FPGA,ITU-R 656译码器将亮度与彩度信号分开、做解交错和缩放处理,并将亮度与彩度信号转换成VGA显示的红、绿、蓝影像信号,Cyclone IV E FPGA将影像信号传输到DE2-115开发板的VGA数模转换芯片(ADV7123),最终实现通过LCD/CRT屏幕播放画面. 仿真结果表明该转换控制器设计算法是正确、有效的.

FPGA;ADV7180;ITU-R;译码器;DE2-115;ADV7123

随着多媒体技术的发展,计算机工业和消费类电子工业正不断融合成一个全新的数字化信息产业,各种类型的信息交流需求的不断增加,实现同类和异类网络间的信息交流已成为一个趋势. 在很多工作业余期间,我们希望可以通过显示器来接收电视信号,以求得到充分的放松. 但电视信号(TV)与计算机监视器的VGA信号之间存在很大的差别,使得两种设备无法通用.

本文设计了一种基于Altera Cyclone IV E FPGA的TV-VGA转换控制器,它可以将DVD播放器输入影像信号装换成VGA显示的红、绿、蓝影像信号,并送到DE2-115开发板上的VGA数模转换芯片,最后就能通过LCD/CRT上看到希望的播放画面.

1 TV-VGA转换的系统结构

TV-VGA转换的控制技术主要包括以下几个部分:I2C串行总线控制器,它主要是控制电视译码器与音频编码器芯片,对其进行相应的读写设置;TD_Detect模块,主要用来侦测电视译码芯片所解出来的水平同步和垂直同步信号是否稳定. 并且还可以简单的侦测输入影像的制式为NTSC制还是PAL制;ITU-656 Decoder,将8位ITU-R BT.656标准接口的影像数据,再译回到16位亮度与彩度分开的影像数据;Deinterlace与Scaler,主要用来解交错与缩放处理;Sdram控制器,主要用来控制sdram保存图框;YUV422-444,主要是将16位亮度与彩度分开的影像数据,再产生像素为24位的YCbCr的影像数据;YCbCr2RGB,用来将24位的YCbCr影像数据转换生成相对应的RGB信号,提供给VGA;VGA控制器,用来产生VGA显示器的水平同步与垂直同步信号;Reset_Delay,当输入的控制信号稳定时,系统的复位信号清零时,需要不同的复位信号;AUDIO_DAC,音频DAC转换模块. 在这个模块中我们可以把已经存储在SDRAM RAM FLASH 中的音频数据转换成模拟量输出[1].

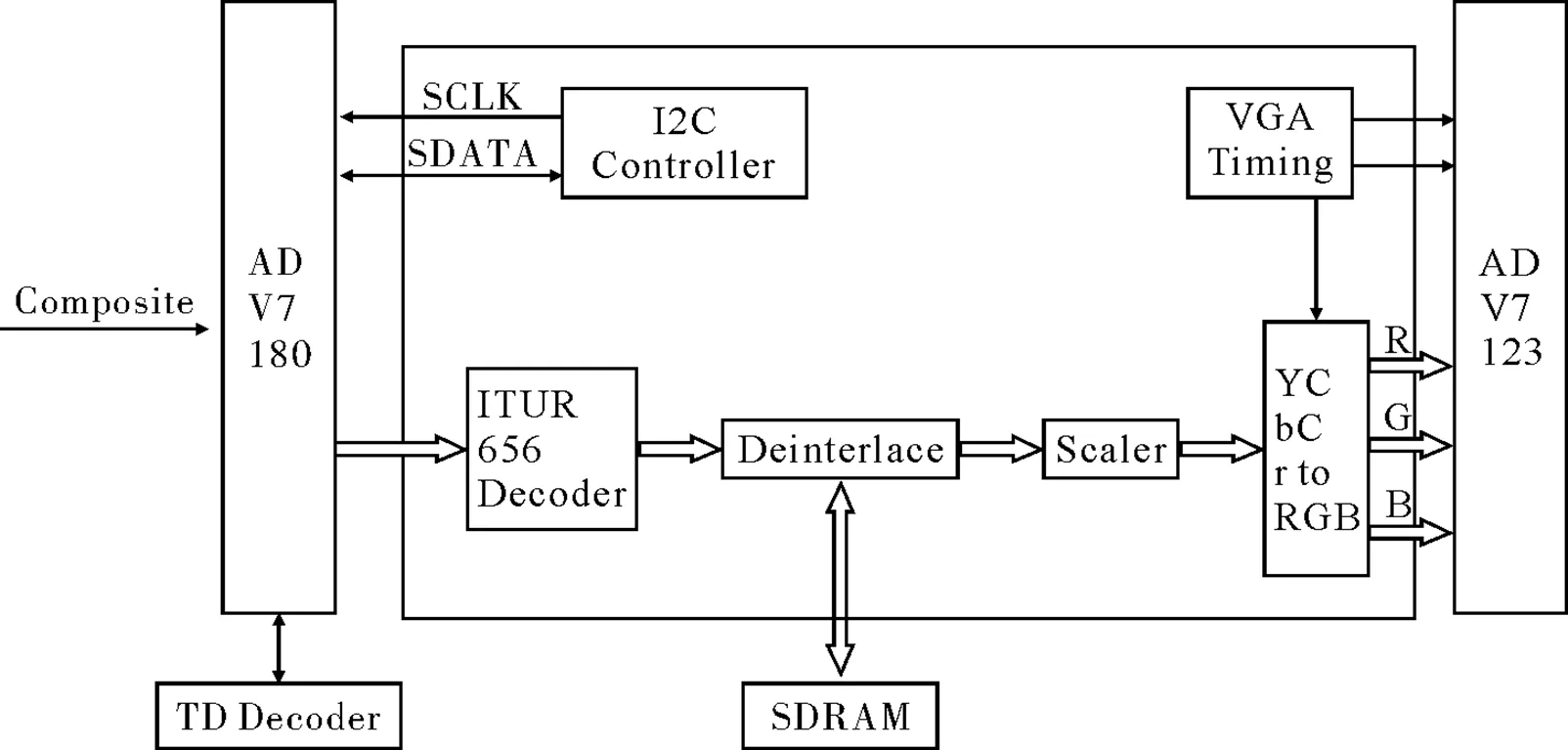

TV-VGA的系统框图如图1所示,输入的影像数据通过电视译码芯片译码之后,送给ITU-R 656 译码,得到亮度与彩度分开的信号,然后经过相应的算法操作得到VGA显示的红、绿、蓝信号,送到DE2-115的VGA数模转换芯片,实现画面播放.

图1 TV-VGA系统框图

2 TV-VGA系统各部分总体设计方案

2.1 I2C总线部分

I2C总线是一种串行通信总线,主要用途是用于连接微控制器及其外围设备. I2C只有两条双向线,分别为串行的数据(SDIN)及串行时钟(SCLK),由一个master来控制多个slave.

I2C开始条件是当SCLK(时钟脚)保持在高电平时,SDIN(数据脚)从高到低,接着会开始进行地址与数据传输;停止的条件是被定义成在SCLK为高电平时,SDIN有一个从低到高的装换.

通过I2C总线控制器我们可以对电视译码芯片(ADV7180)和音频编码器芯片(WM8731)进行相应的设置,来得到对应的译码信号[2].

2.2 TD_Detect侦测部分

该模块是用来侦测电视译码芯片所解出来的水平同步与垂直同步信号是否稳定. 另外,由于NTSC与PAL在水平同步与垂直同步的时序特性有细微的差别,在此还可以简单的侦测输入影像的制式为NTSC制还是PAL制.

NTSC与PAL都是电视广播传输与接口协议. NTSC只针对于美国,日本等国家,而PAL是中国等其他国家采用. NTSC制电视的供电频率为60Hz,场频为每秒60场,帧频为每秒30帧,扫描线为525行,图像信号带宽为6.2MHz. PAL制电视的供电频率为50Hz、场频为每秒50场、帧频为每秒25帧、扫描线为625行、图像信号带宽分别为4.2、5.5、5.6MHz等. 在本论文程序设计中在垂直消隐期间,是对行数进行计数来判断是NTSC制还是PAL制[3].

2.3 ITU-656 Decoder部分

8位的ITU-R BT.656标准接口的影像数据,要通过ITU-R 656 decoder将其译码成16位亮度与彩度分开的影像数据,也就是要得到YUV422数据. 通过上面的TD_Detect可知采用的是PAL制还是NTSC制. 并且要通过视频采集、解码及视频裁剪等三个部分才能完成译码. 本文采用PAL制式(中国采用PAL制式),由于采用PAL制式的摄像机,其视频画面的有效分辨率为720*576,即总共576行(分奇偶两场,各占288行),每行720个像素点,由于是8位串行输出,因此每行总共有1440个字节[4]. 视频解码文件完成的任务就是:通过判断SAV信号,来判断接下来的数据是否为有效视频数据. 如果是,则进一步分离出有效数据的同步信号oDVAL和有效数据Y、Cb、Cr. 视频的裁剪是可以通过一个除法器辅助完成的,主要是对每行视频数据进行裁剪,从720个像素裁剪到640像素. 除数为当前视频行的当前字节数右移1位,被除数为9. 也就是说,每9个像素中,有一个像素点被裁剪掉,即720-720/9=640. 最终得到亮度与彩度分开的信号.

2.4 Deinterlace与Scaler

Deinterlace与Scaler是用来做解交错和缩放处理的,本文在这里是使用精简方法来实现,即直接在顶层分配信号. 如果要针对两种演算法做改善,只需要分别建立Deinterlace与Scaler子模块,维护比较简单.

2.5 Sdram控制器

设计存储在SDRAM的数据采用的是1入2出的模式,即一个端口写入,2个端口读出. 在ITU-656 Decoder部分经过裁剪后的视频分辨率为640*576. 写入SDRAM中时,是将640*576个像素全部写入进去,由于是奇场数据在前,偶场数据在后,因此前640*288行数据为奇场数据,后 640*288行数据为偶场数据.

读取视频数据时,采用乒乓操作,先后读取奇偶场的数据,各240行,组成一幅完整画面,具体读取方法为:1~288行为奇数场数据,289~576为偶数场数据,可以从11~251,300~539读取,或从1~240,289~529读取,只要满足奇偶场的起始行为相邻行,且保证奇数场数据行在前[5]. 最后得到的视频分辨率为640*480(240+240). 在这里就通过sdram读写方法起到解交错和缩放处理功能.

2.6 YUV422-444的算法实现

通过上面操作得到的YUV422影像信号进行色彩空间转换以供下一个模块进行转换,即将16位亮度与彩度分开的影像数据,产生每像素位24位YCbCr影像数据输送给sdram. 当然也可以在进行色彩空间转换之前,对视频行数据进行简单的算法处理,对视频行进行加和及数乘运算,即进行sobel算子处理. 这样做主要是进行边缘检测,降低边缘模糊程度,使效果更好. 然后再行色彩空间转换.

2.7 YCbCr2RGB算法实现

得到24位YCbCr影像数据要送到YCbCr2RGB 模块中进行转换生成相对应的RGB信号以供VGA使用. 这里主要做一定的算法处理即可,算法如下:

R = 1.164(Y-16) + 1.596(Cr-128),G = 1.164(Y-16) - 0.391(Cb-128) - 0.813(Cr-128),B = 1.164(Y-16) + 2.018(Cb-128)在进行该算法之前需要将小数整数化. 因为Verilog里面是不支持小数的,先放大后缩小即可,比如放大512倍即29倍. 即 R << 9 = 596Y + 817Cr – 114131,G << 9 = 596Y - 200Cb - 416Cr + 69370,B << 9 = 596Y + 1033Cb - 141787 这样通过上面的算法处理得到相应的RGB信号.

2.8 VGA控制器部分

RGB信号会送到FPGA开发板上的VGA数模转换芯片(ADV7123). 最后我们就可以看到播放画面了. 在设计VGA控制器时Vertical Parameter和Horizontal Parameter参数可以查看相应的datasheet手册. 该功能模块是VGA控制器,产生VGA显示端的水平同步和垂直同步信号.

2.9 Reset_Delay

由于各个子模块接收到稳定的影像信号会有时间差,所以设计时要设计不同延迟时间的复位信号.

2.10 AUDIO_DAC

在这个模块中,把SDRAM、RAM、FLASH 等音频数据转换成模拟量输出,也可以在模块中自定义函数的音频输出,如sin函数的音频输出. 通过I2C总线控制器的设置可以选择不同的音频输出. 如果不需要这样选择音频输出,则可以将line in 与 line out在内部相连,把DVD影像音频直接输出.

3 仿真结果及分析

本设计使用Verilog编写整个控制程序程序和各个功能模块,使用SignalTap II仿真结果如图2所示.

图2 仿真波形图

其中TD_HS、TD_VS与TD_DATA分别是DVD信号的输入的水平、垂直和数据信号,VGA_R、VGA_G与VGA_B分别是输出给VGA的红、绿和蓝信号.

通过上面的仿真图我们可以知道DVD输入的水平信号TD_HS与垂直信号TD_VS每隔一个周期会同时为高电平,它是为了给复位模块一个输入信号来复位电路,重新传输数据.

同时,可以看到数据信号TD_DATA,比如上面的10h,10h,80h,...,...等经过ITU_R 656译码之后转换成YCbCr信号,接着经过上面介绍的算法处理,就会输出8位的RGB信号.从上面的仿真结果我们可以看到RGB信号中的数据都是像380h,310h,334h,...,...等这种三位十六进制表示的数据.并且还可以看到所有的数据的第一个数据都是不超过3的,因为RGB信号都是10位的数据,用十六进制表示的话前面一位数据不可能超过3.

从这个仿真图像可以看到:整个TV到VGA转换的算法实现是正确、有效的.

4 结论

本文设计的基于DE2-115开发板FPGA实现TV到VGA的视频转换控制器,可以实现在LCD/CRT屏幕上播放DVD的电视信号,其特点为:

1)基于I2C总线控制器,通过将综合代码写入FPGA,方便对外围电路进行配置,有效地利用外围芯片的特点和处理能力;

2)图像处理选用EP4CE115F29C7N的FPGA作为硬件载体;

3)利用quartus自带的算法验证软件SignalTap II来模拟验证从DVD输入影响数据到VGA显示红绿蓝信号的算法正确性和FPGA设计软件开发工具quartus来综合、配置软件代码;

4)采用sobel算子对视频进行边缘检测,可以降低边缘的模糊程度,使影像显示效果更好;

5)采用在读取sdram时,直接选取奇偶各240行组成一幅完整画面,实现解交错和缩放处理,使设计更加简单化.

[1] 廖裕评, 陆瑞强, 友晶科技研发团队. 逻辑电路设计DE2-115实战宝典[M]. 友晶科技, 2012.

[2] 陈宝忠. 基于FPGA的TV-VGA视频转换控制器的设计与实现[D]. 西安: 西安理工大学, 2006.

[3] 郭 平, 李要锋. 基于VX1937的VGA/TV转换器的设计与实现[J]. 电子设计工程, 2010, 18(4): 97-98.

[4] 应芳琴. 基于I2C总线的视频信号采集系统的IP核设计[D]. 杭州: 浙江工业大学出版社, 2005.

[5] 薛海卫. 一种VGA到TV数字视频转换电路的设计[J]. 半导体技术, 2010(2): 194-197.

Design of TV-VGA Based on FPGA

LI Wenlian1, WEI Bibo1, 2, WU Yifu3, PENG Xinxian2, SUN Xiaobing2

(1. School of Physics and Electronic Engineering, Hubei University of Arts and Science, Xiangyang 441053, China; 2. College of Electronic and Information Engineering, Wuhan Institute of Technology, Wuhan430205, China; 3. College of Electronic and Computer Engineering, University of Limerick, limerick, Ireland)

Using Altera Cyclone IV E FPGA to send the input image signals of DVD to the DE2-115 development board of the TV decoder chip (ADV7180),after decoding,the image signals are converted into eight ITU-R standard interface image data ,then it will be sent to the Cyclone IV E FPGA, After separating the brightness signal and chroma signal by ITU-R 656 decoder, and then make staggered and zooming ,Then converting the brightness signal and chroma signal into the red, green, blue image signals of VGA display .After this, the Cyclone IV E FPGA will send the image signals to the DE2-115 VGA analog-to-digital conversion chip on the development board (ADV7123), Finally it is realized to the LCD/CRT screen images. The simulation results show that the conversion controller design is correct and effective.

FPGA; ADV7180; ITU-R; Decoder; DE2-115; ADV7123

TN47

A

2095-4476(2014)05-0033-04

2014-03-19;

2014-03-30

李文联(1956— ), 男, 湖北襄阳人, 湖北文理学院物理与电子工程学院教授, 武汉工程大学兼职硕士生导师, 主要研究方向: 电子技术与计算机应用;

危必波(1990— ), 男, 湖北天门人, 湖北文理学院与武汉工程大学联合培养硕士研究生.

(责任编辑:饶 超)