基于0.18 μm CMOS工艺的低噪声放大器设计

计雷雷,王 江,郑宏兴,张玉贤

(1.天津职业技术师范大学天线与微波技术研究所,天津 300222;2.陕西千山航空电子有限责任公司,西安 710061)

基于0.18 μm CMOS工艺的低噪声放大器设计

计雷雷1,王 江2,郑宏兴1,张玉贤1

(1.天津职业技术师范大学天线与微波技术研究所,天津 300222;2.陕西千山航空电子有限责任公司,西安 710061)

为了提高接收机的性能,基于台积电公司0.18 μm CMOS工艺设计了低噪声放大器。从晶体管模型出发,分析了阻抗匹配,采用源端负反馈和提高输入匹配的电感Q值来降低噪声。通过电路的共源共栅结构搭配电路,消除密勒电容,提高电路性能。

CMOS;反馈;共源共栅;低噪声放大器

在通信系统中,低噪声放大器(LAN)一般用作各类无线电接收机的高频或中频前置放大电路,以及做为高灵敏电子探测设备的放大电路,它是射频接收系统中的重要部件,直接影响着接收机的性能和成本。在提高接收系统性能的关键环节相应放大能力的基础上,它具有噪声系数很低、成本低以及足够带宽等特点,是当前LNA设计中需要面对的问题。CMOS工艺凭借与数字基带电路大规模集成和低成本两大特点,成为低噪声放大电路的首选工艺[1-4]。文献[1]设计了基于CMOS工艺的LNA,其噪声系数很低,性能优越,但是带宽很窄,会因实际加工过程中的误差带来频偏;文献[3]设计的双频段低噪声放大器,功耗低,频段之间隔离度好,但噪声系数超过2.5 dB,会给系统带来不必要的干扰。为了克服上述缺点,本文研究了一种LNA电路设计方案,利用MOS器件设计偏压,降低温度带来的影响,分析5.2 GHz的LNA的电路模型的尺寸与功耗、增益、噪声系数之间的关系,给出设计的方法和公式,同时也对输入网络的匹配特性进行分析,说明了电路设计的关键之处,并通过仿真验证了本设计所要达到的预期结果。

1 宽带低噪声放大器

1.1 CMOS器件模型分析

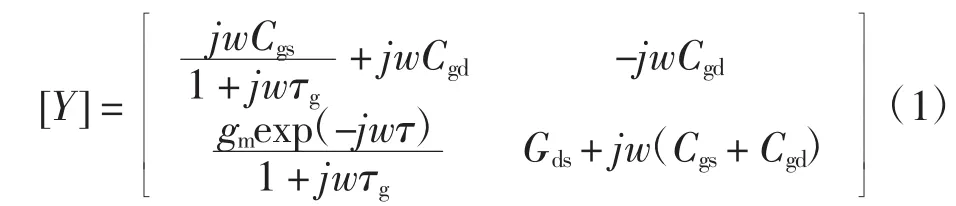

MOSFET器件的等效模型如图1所示。为了表征晶体管的电特性,可以使用共源本征Y参数

式中:Gds=1/Rds;τg=RgsCgs;τ为有效沟道载流子传输时间。将式(1)转换成h矩阵,得到

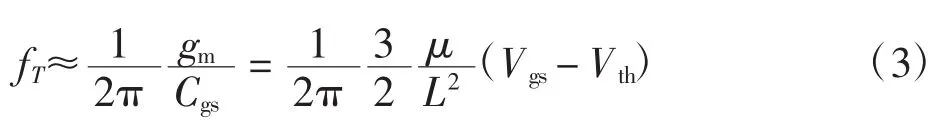

式中:h21为电流增益,选择合适的MOS管的长宽比,可以获得合适的电流增益,当h21=1时,可以获得器件的过渡频率[5]

以式(3)作为电路频率设计参考,选择合适的CMOS管参数,设计的LNA电路如图2所示。图中M1至M4起电压偏置的作用,其中M1和M2的沟道长度0.4 μm,宽度为9.6 μm,M3和M4的沟道长度为0.4 μm,宽度为5.8 μm;M5和M6选用高频管,沟道长度为0.18 μm,宽度为2.5 μm。

图1 MOSFET器件的等效参数模型

图2 LNA设计电路

1.2 消除密勒电容

M5和M6搭配出共源共栅放大器结构。器件在输入和输出节点之间的开路电压增益为Av,那么在这两点之间的阻抗为Z的反馈原件可以由连接在每一个节点和地之间的等效原件代替。等效元件在输入节点的阻抗为:

在输出节点阻抗为:

式中:Zmi和Zmo分别为输入节点、输出节点与地之间的等效输入密勒阻抗。这里使用共源共栅结构放大器,器件M5是一个压控电流源,一个小的栅压可以产生一个大的漏电流,通过输出负载RLOAD,从而产生一个大的输出电压。当M6共栅放大器偏置于饱和状态,这个低阻抗电流缓冲器处于M5和RLOAD之间,可以减小密勒效应。

1.3 噪声系数

噪声系数定义为输入信噪比与输出信噪比的比值。为了降低噪声,人们做了很多研究,包括阻抗匹配技术[5]、级间相互作用的噪声抵消技术[6]和源端电感负反馈[7]等等。根据豪斯理论[8],当ΓS,opt=S11*时,器件的最小噪声系数和最大增益将同时达到。而分立元器件不可能同时得到最小噪声系数和最大增益。为了解决这个矛盾,采用阻抗匹配和源端电感负反馈技术获取低噪声系数以及合适的增益,下面对这两种技术进行分析。

2 阻抗匹配技术

输出噪声电流是由MOS管的沟道热噪声[5]所引起的,等效电路如图3所示。

图3 考虑沟道热噪声的共源放大器等效电路

这里得到

式中:R1取决于电感Lg的品质因数。从式(6)中可以看出,调节匹配电路中Lg电感品质因数,可以优化电路噪声系数。同理,调节图2电路中电感L1和L2的品质因数,可以获得较低的噪声系数。

3 源端电感负反馈技术

利用反馈电感产生实数的输入电阻Req为:

式中:wT为晶体管的截止角频率,取决于工艺而与晶体管尺寸无关;gm为晶体管的跨导;Cgs为M5的栅源电容。根据双端口网络模型[7],电压增益为:

LNA噪声系数NF为:

通过调节电路中源端阻抗Ls修正Req,改变式(8)和(9),可以使近似成立。调节图2电路中的Ls,器件最小噪声系数和最大增益将同时达到,能够获取电路最佳性能。

4 仿真结果

采用台积电公司0.18 μm CMOS工艺,对图2所示的具有宽带特性LNA电路用ADS软件进行仿真。图2中的电路打包为LNA_ALL,如图4所示。

图4 LNA的仿真模型

通过衡量放大器的主要指标包括S参数、噪声系数和稳定度等,反复调节电感、电阻以及电容元件参数达到需要的设计指标后,获得设计数据如表1所示。

表1 LNA电路参数

按照表1中的参数,用ADS软件仿真得到所设计LNA电路的输入、输出特性S11、S22见图5(a)、(b)。在4.7~5.8 GHz频带内S11<-10 dB,S22<11 dB,表明输入输出匹配良好。放大器对噪声系数有严格要求,噪声影响接收机的灵敏度。这里所设计的电路(图2)最小噪声系数在频带内均小于1.2 dB,见图5(c),能够提高系统的灵敏度。稳定性是电路正常工作的必要条件,保证电路在工作中不会振荡。本设计电路在频带内稳定度均大于5,见图5(d),达到良好的性能指标。

在5.2 GHz频率点上,增益S21为12.14 dB,且带内4.7-5.8 GHz,增益波动仅0.5 dB,表明增益平坦,保证放大器的放大效果,见图5(e)。

5 结束语

图5 仿真结果

本文采用0.18 μm CMOS设计工艺,在4.7~5.8 GHz的频段内实现宽带、低噪声,提高电路性能。其噪声系数小于1.12 dB,稳定系数大于5,且在5.2 GHz增益达到12 dB,设计的LNA在各项性能指标方面均能满足设计的要求。

[1] YANG H C.High quality of 0.18 μm CMOS 5.2 GHz cascode LNA for RFID tag applications[C]//IEEE 2nd International Symposium on Next-Generation Electronics(ISNE).2013:313-316.

[2] ARSHAD S,ZAFAR F,WAHAB Q U.Design of a 4-6 GHz Wideband LNA in 0.13 μm CMOS Technology[C]//2012 IEEE International Conference on Electronics Design,Systems and Applications(ICEDSA).2012:125-129.

[3] DAO V K.Dual-band LNA for 2.4/5.2GHz applications[C]// Proceedings of Asia-Pacific Microwave Conference 2006. 2006:678-682.

[4] DATTA S.A concurrent low-area dual band 0.9/2.4 GHz LNA in 0.13 μm RF CMOS technology for multi-band wireless receiver[C]//Circuits and Systems(APCCAS),2010 IEEE Asia Pacific Conference.2010:280-283.

[5] 李志群,王志功.射频集成电路与系统[M].北京:科学出版社,2008:105.

[6] 董叶梓,张鹏,毛陆虹.采用噪声抵消技术的高增益CMOS带宽LNA设计[J].集成电路应用,2013,39(5):44-47.

[7] 刘萌萌.具有抑制窄带干扰带阻特性的3-10 GHz超宽带LNA[J].清华大学学报,2009,49(4):31-34.

[8] LI Richard Chi-His.RF Circuit Design[M].北京:电子工业出版社,2011.

A low noise amplifier design based on 0.18 μm CMOS technology

JI Lei-lei1,WANG Jiang2,ZHENG Hong-xing1,ZHANG Yu-xian1

(1.Institute of Antenna and Microwave Techniques,Tianjin University of Technology and Education,Tianjin 300222,China;2.Qianshan Aviation Electronics Co Ltd,Shaanxi Province,Xi′an 710061,China)

To increase properties of receiver,a low noise amplifier is designed based on Taiwan Semiconductor Manufacturing Company Limited 0.18 μm CMOS technology.Starting with transistor model, we analyze the impedance matching.Noise has been decreased by using source negative feedback and improving Q-factor of input matched inductance.The miller capacitance can be eliminated by using collocating source and grid structure.Circuit performance has been improved.

CMOS;feedback;collocating source and grid structure;low noise amplifier

TN722.3

A

2095-0926(2014)03-0008-04

2014-04-30

国家自然科学基金项目(61371043);天津市应用基础及前沿技术研究计划(12JCYBJC10500).

计雷雷(1988—),男,硕士研究生;郑宏兴(1962—),男,教授,博士,硕士生导师,研究方向为天线、微波电路和计算电磁学.