一种线性可控全集成SiGe BiCMOS驱动放大器

严琼,武永华

(福建江夏学院 电子信息科学学院,福建 福州 350108)

一种线性可控全集成SiGe BiCMOS驱动放大器

严琼,武永华

(福建江夏学院 电子信息科学学院,福建 福州 350108)

基于Jazz工艺,提出一种线性可控全集成SiGe BiCMOS驱动放大器(DRA),实现多种可调功率增益放大作用。电路采用全差分共射共基结构,通过调节CMOS电流镜偏置电路和SiGe-HBT管尺寸以及3bit控制位,实现1dB步长的可控增益。仿真结果显示:在10μA的带隙基准电流源以及3.3V的电源电压下,DRA实现八种可调功率增益,其线性度指标即输出1dB压缩点OP1dB>3dBm,电路供电电流<10mA,且电路输入输出匹配良好(S11与S22均小于-19dB)。

BiCMOS,驱动放大器(DRA),线性度,增益可控

在物联网飞速发展的今天,作为物流自动识别领域灵魂的射频技术是我国物流业发展的重中之重。射频技术以其非接触式双向通信,克服了光学可视的局限性、识别距离有限、信息不可更改的缺点,轻松满足大流量的信息和高安全性、高速的信息处理的需求。

本文偏置电路采用BiCMOS工艺。因为SiGe BiCMOS器件射频性能超前RF CMOS两个工艺代,如0.18 μm SiGe BiCMOS技术可以与90 nm RF CMOS相比较[1],因此采用BiCMOS工艺可采用较低代次的工艺实现,可降低成本。本文主放大电路采用SiGe-HBT器件进行设计,是因为该器件与CMOS相比,寄生参数少,而且发射结两边的掺杂浓度更低,E-B结电容小,因此相比CMOS器件更能在高频处获得增益及增益平坦度。

1 系统设计

在UHF RFID阅读器中,传统的射频前端Tx-FE路径,将上混频器UP-Mixer的差分输出信号直接发送给功率放大器PA,其弊端是:上混频器的转换增益CG一般为负值,而功率放大器输入端需要0dBm左右的大信号,很难实现无损耗的理想传输。增加驱动放大器DRA不仅可以放大上混频器UP-Mixer信号,实现0dBm左右的大信号发送给功率放大器PA,而且可以适应UHF RFID阅读器系统中,标签距离可变的实际应用。

在本项目中,射频前端Tx-FE路径主要包括上混频器UP-Mixer、驱动放大器DRA以及功率放大器PA,其系统框架结构如图1所示。DRA接收来自UP-Mixer的差分输出信号,通过控制增益,实现输出P1dB>0dBm(留有一点裕度),放大功率后发送给功率放大器。

图1 UHF RFID阅读器射频前端Tx-FE路径系统框架结构图

本文设计的DRA采用全差分共射共基结构,通过调节电流镜偏置电路和SiGe-HBT管尺寸以及3bit控制位,实现1dB步长的可控增益。

2 电路设计

2.1 DRA偏置电路的设计

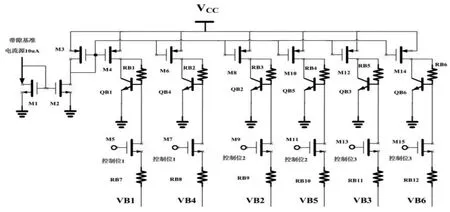

当DRA工作时,偏置电路在10μA的带隙基准电流源以及3.3V的电源电压下,提供给SiGe-HBT管一个稳定的偏置电压以及偏置电流,并且具有温度补偿特性。本次设计采用的电流镜偏置电路结构如图2所示。

图2 电流镜偏置电路原理图

如图1所示,M1和M2、M3和M4、M6、M8、M10、M12、M14构成有源镜像电流源,原理如式(1)所示:

其中,ID4为M4管子的漏极电流,IREF为10μA的带隙基准电流源产生的电流,W/L为管子的宽长比。选择合适的α与β可以确定ID4与IREF之间或大或小的比率,这就是镜像电流源的工作原理。

在图2中,3对外接偏压的SiGe-HBT管以QB1和Q1为例,也构成有源镜像电流源,为主偏置管Q1提供基极偏置。其中M5、M7、M9、M11、M13、M15为开关管,电阻RB7、RB8、RB9、RB10、RB11、RB12设置为5k以上,防止射频信号从SiGe-HBT管的基极通过偏置电路泄露。

2.2 DRA主放大电路的设计

电路设计时,在保证DRA线性度指标即输出1dB压缩点OP1dB>3 dBm,电路供电电流<10 mA,且电路输入输出匹配良好(S11与S22均小于-19dB)的前提下,采用折中方案,实现应用于UHF波段的基于Jazz工艺的八种可调功率增益放大作用。

如图3所示,电路主体部分可以分为两级:带有发射极电感负反馈的共射极放大器以及共基极放大器,它们组成Cascode结构,从而获得较高增益。共射极放大器实现驱动放大作用,共基极放大器具有高输入阻抗和低输出阻抗,减小DRA输入与输出之间相互作用,降低密勒效应的影响。

图3 DRA的电路原理图

通过调节3 bit控制位,使得3对并行输入的SiGe-HBT管处于导通或者截止状态,实现八种可调功率增益放大作用。发射极负反馈电感Ls有利于使DRA输入阻抗的实部与上混频器的输出阻抗相匹配,获得最大的功率传输。3对并排的电容C1、C2、C3、C4、C5、C6作为DRA的输入隔直电容,防止偏置通过输入端的电感L1、L2回流到上混频器。输出端采用典型的L-C网络作为负载[2]。通过在输入端串联电感,并在SiGe-HBT管基极串联不同大小的电容,构成L-C滤波谐振网络,同时也是匹配网络,增加匹配电路的可调性,再调节输出端公用的负载L-C匹配,实现良好的输入输出匹配。

输入网络谐振时,输入管的有效跨导gm可表示为:其中gm1、gm2、gm3分别作为Q1、Q2、Q3的跨导。a1、a2、a3分别代表3个基极偏置电路的数字控制位,通过取值0或者1来代表相应晶体管的工作状态(导通或者截止)。DRA的功率增益G可表示为:其中Rout为DRA的等效输出阻抗,Qin为输入谐振网络的品质因子。从式(3)可以看出,功率增益可以实现8级数字可调。

3 版图设计

DRA的版图如图4所示。电路的输入端和输出端均工作在射频频率,因此在版图设计中,应特别注意寄生电阻、电容、电感参数的影响[2]。电路采用全差分结构设计,因此还应特别注意对称和匹配。

图4 DRA的版图

4 仿真结果与分析

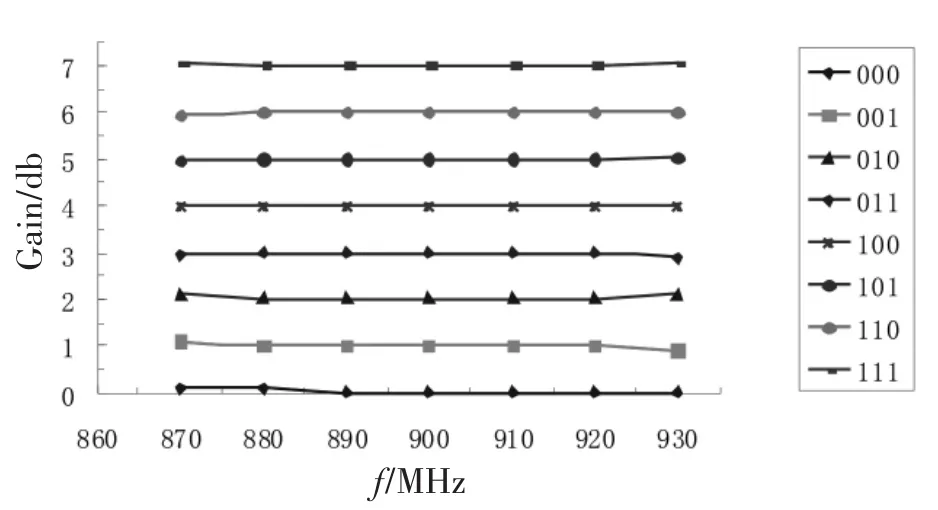

仿真结果显示:在10 μA的带隙基准电流源以及3.3 V的电源电压下,DRA的增益分别为0、1、2、3、4、5、6、7 dB,如图5所示。在8种增益情况下的线性度即输出1 dB压缩点均满足OP1 dB>3 dBm。

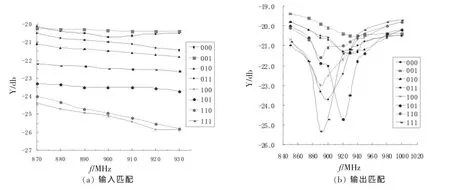

电路的输入输出匹配情况即 S11与S22如图6所示,均小于-19 dB,说明输入输出匹配良好。

图5 DRA的增益

5 结论

本文基于Jazz工艺,提出一种线性可控全集成SiGe BiCMOS驱动放大器(DRA), 实现多种可调功率增益放大作用。电路采用全差分共射共基结构,通过调节CMOS电流镜偏置电路和SiGe-HBT管尺寸以及3bit控制位,实现1dB步长的可控增益。仿真结果显示:在10μA的带隙基准电流源以及3.3V的电源电压下,DRA实现八种可调功率增益,其线性度指标即输出1dB压缩点OP1dB>3dBm,电路供电电流<10mA,且电路输入输出匹配良好(S11与S22均小于-19dB)。

图6 DRA的输入、输出匹配

[1]MARC TIEBOUT,HANS-DIETER WOHLMUTH,HERBERT KNAPP,et al.Low power wideband receiver and transmitter chipset for mm-wave imaging in SiGe bipolar technology[J].IEEE Journal of Solid-State Circuits,2012,47(5):1175-1184.

[2]JOE VALLIARAMAPATH,SAURABH SINHA.Linearity improvement analysis for power amplifiers at mm-wave frequencies[J].Microwave and Optical Technology Letters,2014,56(3):743-748.

(责任编辑:朱联九)

A High-linearity Gain-controlled Fully Integrated iGe BiCMOS Driver Amplifier

YAN Qiong,WU Yong-hua

(College of Electronics and Information Science,Fujian Jiangxia University,Fuzhou 350108,China)

ABSTRCT:A high-linearity gain-controlled fully integrated SiGe BiCMOS driver amplifier is proposed based on Jazz process,and the gain-controlled driver amplifier with many kinds of power gain is realized.In the circuit,a fully differential cascode structure is used and the proposed DRA can achieve the gain step of 1dB by adjusting the CMOS current-mirror bias circuit,the size of SiGe-HBT and the 3 control bits.The simulation results show that under the 10uA bandgap reference current source and 3.3V supply voltage,the proposed DRA can realize the gain-controlled function with 8 kinds of power gain. The linearity of DRA,that is,output 1dB compression point shows OP1dB>3dBm,the power supply current<10mA with good input and output matching(S11 and S22 are both less than-19dB).

BiCMOS,driver amplifier(DRA),linearity,gain-controlled

TN722

A< class="emphasis_bold">文章编号:1

1673-4343(2014)04-0075-04

10.14098/j.cn35-1288/z.2014.04.014

2014-05-27

福建省中青年教师教育科研项目(JA1332)

严琼,女,福建福州人,助教。研究方向:集成电路设计。