基于FPGA的光通信误码率测试系统设计

游淑民

(集美大学 信息工程学院,福建 厦门 361021)

基于FPGA的光通信误码率测试系统设计

游淑民

(集美大学 信息工程学院,福建 厦门 361021)

误码率是数据传输设备的衡量指标之一,误码率测试是SFP光通信模块生产与设计中重要的环节。针对SFP光通信模块设计了一种基于FPGA的误码率测试系统,系统采用并行m型伪随机序列编码,可实现PRBS-7至PRBS-31标准的m序列码流生成,与SFP光通信模块的通信速率为1.25Gbps。系统打破常规测试的局限性,模块连接简便,可以在短时间内对SFP光通信模块进行准确测试,提高了SFP光通信模块误码率测试的效率。

SFP;误码率测试;FPGA;m型伪随机序列

随着光通信系统的传输速率越来越高,对光电设备的可靠性要求也在提高。数据链路长距离的传输或者是外部的干扰都会引起通信数据出现错误。因此需要误码检测来模拟通信链路中的数据传输,在通信系统实际工作之前对通信设备可靠性进行验证。在传输速率确定的情况下,光通信系统的误码率成为了检测光电系统性能的关键所在。在实际系统测试中,通常使用误码仪对数字通信系统的误码进行检测。但是传统的误码检测仪速率较低、接口单一,拥有光接口的型号也较少,已经不能满足当今光通信系统的误码检测要求。本文针对SFP光通信模块设计了一种通信速率为1.25Gbps的误码检测系统,系统采用FPGA作为主控设备,可以克服传统误码检测仪在数字信号处理(DSP)、扩展性及实时性等方面的不足,同时可以在门级进行设计和改动,也能更快的移植到更高速率的光通信模块误码率检测平台。

1 系统总体设计方案

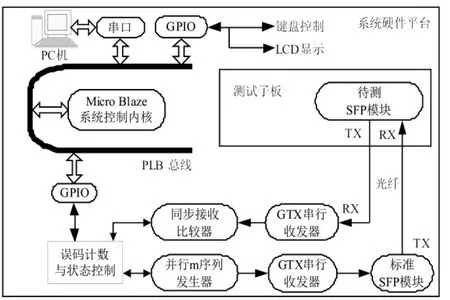

本文所设计的误码测试系统是基于Xilinx公司的Virtex-6 FPGA ML605开发板,FPGA芯片型号为:XC6VLX240T-1FFG1156。系统由一块FPGA开发板和一个SFP光通信模块测试板构成,结构如图1所示,FPGA片上系统产生PRBS伪随机码,通过GTX高速收发器接口发送到标准SFP模块,标准SFP模块再通过光纤传输到外部待测的SFP光通信模块,最后再通过GTX高速收发器传输回FPGA进行码流对比,判断是否有误码。FPGA片上系统采用32位SOC软核MicroB-laze做为系统控制内核,误码测试部分由误码计数和状态控制、并行m序列生成、GTX高速串行收发器和同步接收与比较等模块组成。

图1 系统结构框图

2 伪随机序列产生

为使测试结果尽可能真实地反映系统的性能,需要采用伪随机序列作为测试中传输的信号,常用的伪随机序列有m序列、Gold序列以及Walsh序列等,m序列在误码检测中应用最广泛,其它序列均由m序列推衍产生的,所以本系统选择m序列作为误码检测伪随机序列。

m序列是一种线性反馈移位寄存器序列,由移位寄存器的反馈运算生成。本次设计采用Fibonacci型移位寄存器生成m序列[1-2],该结构中移位寄存器的反馈抽头位置与本原多项式一致,序列与初始状态相对应,其产生速度主要受反馈网络的时延限制。如图2所示,n个寄存器D,从左至右分别代表第1级,第2级,…,第n级寄存器。假设在开始状态,第1级的内容为an-1,第2级内容为an-2,…,第n级内容为a0,可以推导出伪随机序列在最大长度情况下的本征多项式为:

图2 Fibonacci型线性移位寄存器模型

理论上n值越大,伪随机序列每个周期数就越大,随机性就越强。但是n的取值不能太大,n取值越大,占用FPGA的资源越多,影响电路的工作频率。通过公式及模型可知,m序列可通过基本的移位寄存器经过多级异或运算产生,核心代码如图3所示,伪随机序列的并行输出宽度为Nbits,移位寄存器反馈拍数为TAP,LENGHT为D触发器的个数。D触发器的个数(LENGTH)和PRBS数组的宽度(Nbits)决定了进行反馈的逻辑深度和伪随机序列并行输出的个数。LENGHT的取值越大,伪随机序列的周期数就越大,m序列的随机性越强,但是FPGA内部资源的消耗和电路的反馈深度会相应增加,电路的关键路径会变长,影响电路的工作频率,如表1所示。图4为伪随机序列产生模块在LENGHT为7,TAP为6的情况下的仿真波形。

图3 伪随机序列产生核心代码

表1伪随机序列参数对比列表

图4 伪随机序列产生模块仿真图

3 高速码流收发设计

系统所需要进行误码测试的SFP光模块的速率为1.25Gbps,FPGA普通IO口的翻转特性无法达到此要求,系统采用了Xilinx Virtex6中提供的GTX高速串行收发器进行高速码流的发射与接收。

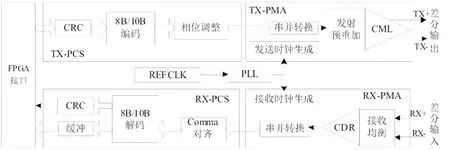

GTX作为一种低功耗的Gigabit收发器[3],配置灵活,功能强大,与FPGA内部的其他逻辑资源紧密联系,可用于实现多种高速接口,如XAUI、PCIE、SATA等。本次设计所选用的FPGA中,GTX传输速率为600 Mb/s到6.6 Gb/s,支持双向收发,GTX的结构如图5所示,接收和发送均由物理编码子层(PCS)和物理媒体接入子层(PMA)两部分组成,PCS提供丰富的物理编码层特性,如8b/10b编码/解码器、弹性缓冲器及时钟校准等功能;PMA部分为模拟电路,包括串行/解串器(SERDES)、TX/RX输入/输出缓冲、时钟产生器和时钟恢复电路,提供高性能的串行接口特性,如预加重、均衡等功能。

图5 Virtex6 GTX结构框图

3.1 GTX发送模块设计

GTX发送模块的设计主要包括CRC电路、8B/10B编码电路和电流模式逻辑电路 (CML)3个部分,FPGA将要传送的数据传给GTX模块,GTX模块首先对数据进行CRC校验,然后按照用户的设置对数据编码,经过相位调整和并串转换之后发射出去。发送模块主要包括两个时钟域,时钟(TXUSRCLK2)为GTX模块的数据装载时钟,另一个时钟(TXUSRCLK)为内部的PCS逻辑电路提供发送时钟。

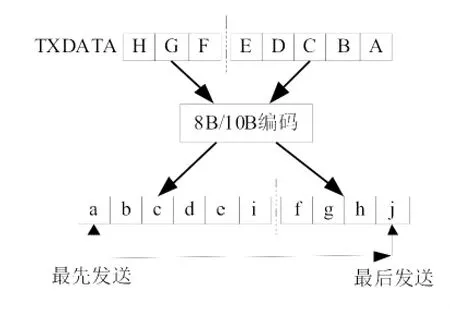

图6 8B/10B编码映射关系

8B/10B编码是一种预防通信链路DC失调的编码机制,在多个连续的“1”或者“0”后插入一位“0”或者“1”,从而保证信号DC平衡。如图6所示,设计中将8位数据分解为两组数据,一组3位,一组5位,经过编码后分别映射为4位和6位的子码,同时各自对应一个反码。在对数据进行编码时,根据当前的DC偏差决定使用子码的正码还是反码,保证信道中的数据DC平衡。8B/10B编码中通过“K码”来实现信号的传输控制,本系统中采用D28.5的码型,即以0xBC为原码,在接收数据时根据原码进行数据的帧对齐。

GTX模块中有两个PLL,参考时钟可以单独提供或者从其他GTX模块中引入,本文采用板载125M的晶振做为驱动GTX模块的PLL时钟。FPGA到GTX的发送模块有两个并行的时钟“TXUSRCLK”和“TXUSRCLK2”。TXUSRCLK是用来进行PCS逻辑的内部时钟,时钟速率取决于GTX模块的接口宽度(INTDATAWIDTH)与发射器的线速率,计算公式如式(2)所示:

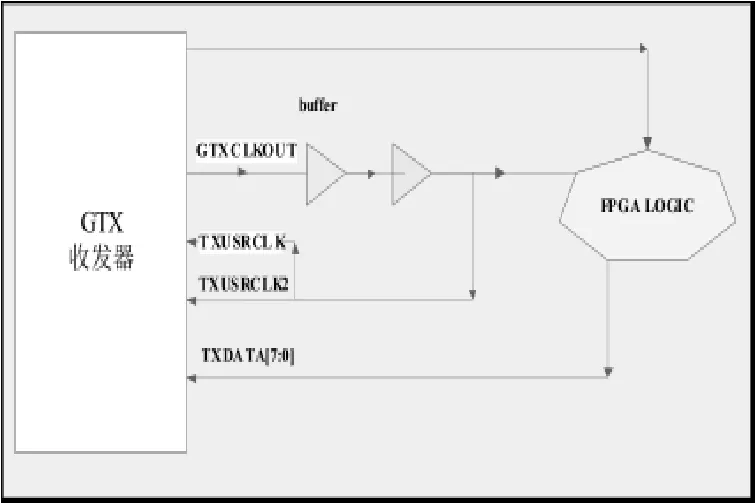

GTX发送模块的数据装载时钟 (TXUSRCLK2)频率由发送的线速率、TXDATA的位宽以及8B/ 10B编码所决定。本文基于系统同步时序设计的考虑,将TXUSRCLK2作为GTX模块的装载时钟、FPGA的系统时钟和同步FIFO的读写时钟,内置PLL的输出端GTXCLKOUT驱动GTX模块时钟的电路框图如图7所示。

3.2 GTX接收模块设计

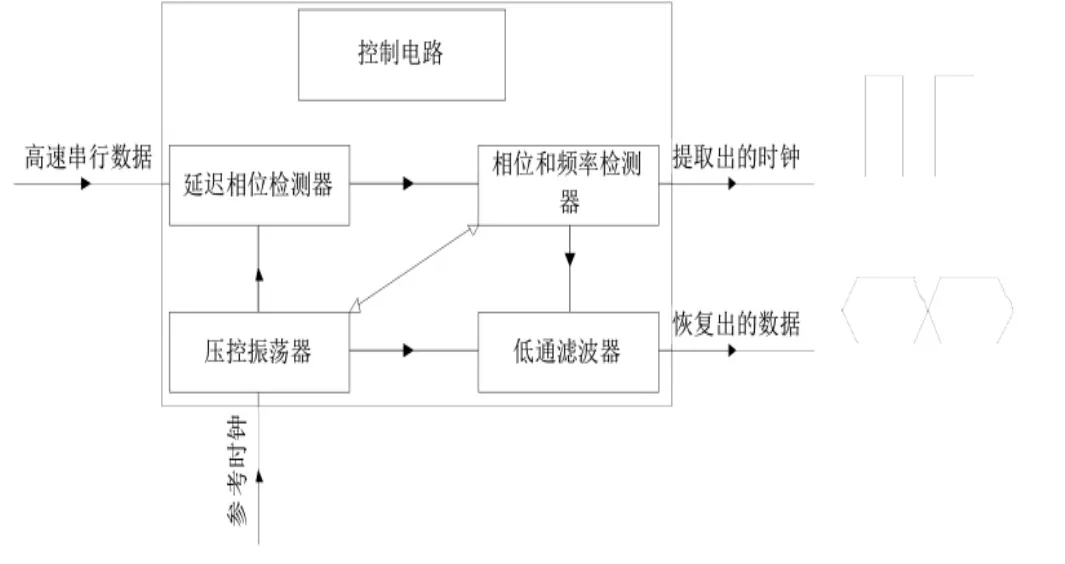

GTX接收模块的核心电路为接收均衡电路,其内部含有自同步电路,当接收外部高速数据时,不需要提供高速时钟,因此可以简化链路互连以及时钟树的复杂度,而且比源同步和系统同步更有保证且更有效率。接收均衡电路中的直接逻辑实现电路(CDR)可以直接从编码后的串行数据流中依据数据的跳变沿提取传输数据的时钟,并且恢复高速数据,完整的CDR电路包括延迟线相位检测器(DPD)、压控振荡器(VCO)、环路滤波器和控制电路等。其主要结构如图8所示。

图7 GTXCLKOUT驱动GTX时钟框图

图8 CDR电路结构图

鉴相/频器将压控振荡器的输出频率锁定在数倍于串行数据的参考时钟上,并根据串行数据的跳变沿实时调整压控振荡器的输出频率分频时钟的瞬态相位,以修正其瞬时频率,实现与串行数据的匹配,从而恢复时钟。数据的恢复则是在眼图搜索的基础上从多级延迟线中取出信号质量最好的采样点输出,也可以采用过采样器以逻辑的方式实现数据的动态恢复。

GTX接收高速串行数据首先需要位对齐,才能接收到准确的数据流,否则接收的数据如果错位或者丢失,则会导致串并转换恢复的数据并不是原数据,后面FPGA进行的数据处理工作也就没有了意义。本文中设计使用的“K码”为0101111100即0xBC,接收器的位对齐操作如图9所示。

图9 接收器对接收数据进行对齐校准

4 误码检测电路设计

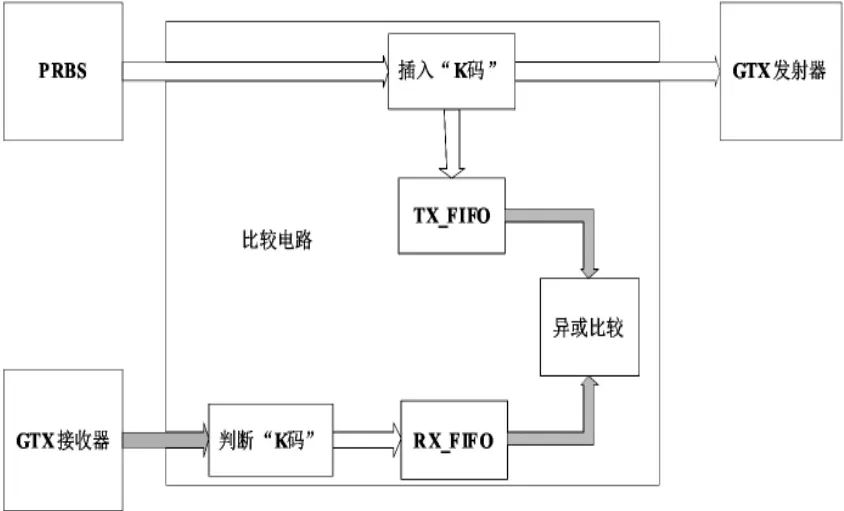

误码检测电路使用同步FIFO对发射序列和接收序列进行缓存,然后比较和计算得到SFP光通信模块的误码率。FPGA中误码序列的比较框图如图10所示。在误码序列的比较电路中,两个FIFO的读写时钟均为系统时钟,FPGA生成伪随机序列并装载至GTX发射器,同时将装载数据写入TX_FIFO中,由于系统延迟,接收器在一段时间后开始接收数据,并将接收数据写入RX_FIFO。FPGA同步读取这发送和接收FIFO的数据进行比较,如果相同说明没出现误码,反之则说明通信出现误码。

GTX发送模块从复位到正常工作需要一个准备时间,为了防止在GTX模块未准备就绪FPGA就开始发送数据的情况出现,需要在控制模块里使用一个计数器电路进行延时控制。当发送标志位为1并且计数器溢出时,FPGA传送伪随机序列给GTX发送模块进行装载发送;反之,则FPGA把“K码”装载至GTX发送模块,进行信道同步工作。

本设计中,为了便于序列的比较,防止信号抖动带来的影响,将16个伪随机数设置为1帧,在FPGA比较模块内用0xBC作为帧同步标志。FPGA每向GTX发送模块装载16个伪随机码,插入一个帧同步标志0xBC,并将帧同步标志后装载的16个数据写入发送缓存模块TX_FIFO,以便与接收缓存模块RX_FIFO中的数据进行比较,当接收器识别到帧同步标志0xBC后,FPGA将其随后的16个数据写入接收缓存模块RX_FIFO。当RX_FIFO的数据个数小于32时,两个FIFO的读端口被禁止,当RX_FIFO的数据等于32时,表明RX_FIFO里至少有两帧伪随机序列,这时使能两个FIFO读操作,如图11所示误码检测流程。FPGA读出两个FIFO的数据进行异或比较,如果为0则说明无误码,反之则有误码,并将误码数量和误码标志传给控制内核。

图10 误码检测电路框图

图11 误码率检测流程

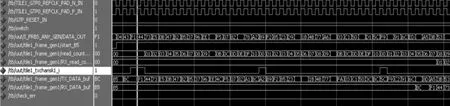

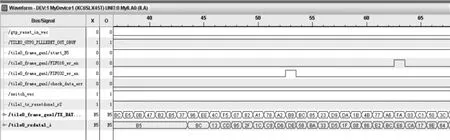

如图12所示FPGA误码检测模块仿真波形,伪随机序列模块的输出DATA_OUT向GTX发送模块传送伪随机数。控制模块的使能端switch以及收发器延迟计数器的标志位start_B5同时为1时,GTX发送模块的接口 TX_DATA_buf开始接收 FPGA产生的伪随机序列,同时计数器read_count_i开始计算GTX发送的伪随机序列字节数。GTX模块每发送16字节,K码使能接口txcharisk置1使GTX在发送序列中插入一个帧对齐标志0xBC。经过一段时间后接收端RX_DATA接收到伪随机序列,当检测到帧对齐标志位0xBC时,接收计数器RX_read_count开始计算接收的伪随机序列字节数。接收字节数大于32时,同步读取发送FIFO和接收FIFO的数据进行比较,误码标志位check_err为0,说明通信正常,反之则说明出现误码。

图12 FPGA误码率检测仿真波形

5 结论

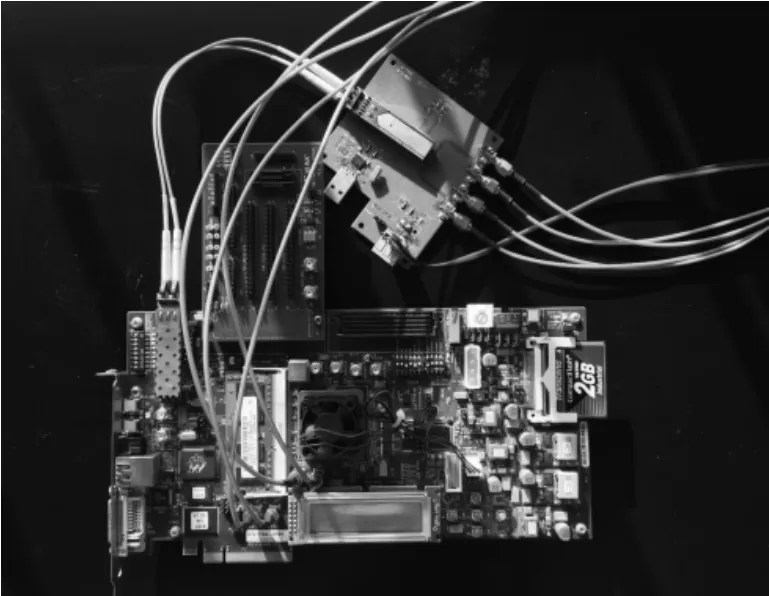

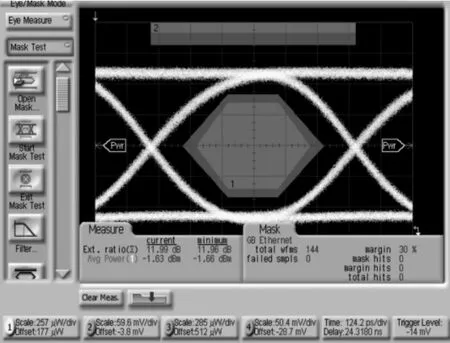

本文针对SFP光通信模块设计了一种基于FPGA的误码率测试系统,测试系统实物图、最终测试SFP模块眼图误码检测模块的Chipscope实时监测波形图如图13~15所示。

图13 测试系统硬件实物图

图14 测试完成后SFP模块的眼图

图 15 误码检测模块Chipscope实时监测波形

系统采用并行m型伪随机序列编码,可实现PRBS-7至PRBS-31标准的m序列码流生成,与SFP光通信模块的通信速率为1.25Gbps,系统打破常规测试的局限性,模块连接简便,可以在短时间内对SFP光通信模块进行准确测试,提高了SFP光通信模块误码率测试的效率。

[1]邹学玉,易建国.一类基于FPGA的m序列发生器的设计[J].长江大学学报:自然科学版.2006,3(3):84-86.

[2]林可祥,汪一飞.伪随机码的原理与应用[M].北京:人民邮电出版社,1998.

[3]XI LIN X.Virtex-6 FPGA GTX transceivers user guide[BD].www.xilinx.com,2011.

[4]刘江,张宏霄,刘洛琨.基于FPGA的误码率测试仪的设计与实现[J].微计算机信息,2005,21(4):162-163.

[5]张驰.基于SFP光模块的误码仪的研制[D].成都:电子科技大学,2009.

[6]BETZ V,ROSE J.VPR:a new packing,placement and routing tool for FPGA research[M].[s.l.]:Springer,1997.

[7]曾金.高速实时信号处理系统的 FPGA软件设计与实现[D].北京:北京工业大学,2009.

[8]王道宪.CPLD/FPGA可编程逻辑器件应用与开发[M].北京:国防工业出版社,2004.

[9]孙航.Xilinx可编程逻辑器件的高级应用与设计技巧[M].北京:电子工业出版社,2004.

[10]赵不贿,景亮,徐雷钧,等.在系统可编程器件与开发技术[M].北京:机械工业出版社,2001.

[11]赵曙光,郭万有,杨颂华.可编程逻辑器件原理、开发与应用[M].西安:西安电子科技大学出版社,2006.

[12]杨晖,张凤言.大规模可编程逻辑器件与数字系统设计[M].北京:北京航空航天大学出版社,1998.

[13]PETERSON B A,MEDINA R,PETERSON F J.Pluggable transceiver module having rotatable release and removal lever with living hinge[Z].Google Patents,2002.

[14]王妮,侯韶华.基于 SFP光模块控制系统的设计和实现[J].光通信技术,2010(009):36-38.

[15]王三.千兆光纤收发模块SFP的设计及测试.[C]//第十三届全国青年通信学术会议论文集(上).[s.n.],2008.

(责任编辑:朱联九)

Design of FPGA Based Bit-error Rate Test System for Optical Communication

YOU Shu-min

(The College of Information Engineering Jimei University,Xiamen 361021,China)

Bit-error rate (BER)is a criterion used for testing the data transmission equipment and BER test is an important procedure in manufacturing and design of SFP optical communication modules.In this paper,a BER test system based on FPGA for SFP optical communication module is proposed.This system employs parallel m-sequence based pseudo-random coding and therefore is capable to generate standardized m-sequences from PRBS-7 to PRBS-31.The communication rate between BER test system and SFP optical communication module is 1.25 Gbps.The proposed BER test system employed a novel testing method and connection to SFP modules is simple,thus it is able to test SFP modules in a short time with high accuracy,i.e.,the test efficiency is improved.

SFP;bit-error r ate test;FPGA;m-style pseudo random sequence

TP312

:A

1673-4343(2014)04-0079-07

10.14098/j.cn35-1288/z.2014.04.015

2014-07-08

集美大学育研基金项目(XX201406)

游淑民,女,福建龙岩人,助教。研究方向:集成电路设计。