基于STM32+FPGA的数据采集系统的设计

曹彬乾,程远增,杨 青

(军械工程学院电子与光学工程系,河北石家庄050003)

0 引 言

由于火控系统工作环境特殊,所需采集信号复杂多样,传统的以微控制器或PC为主的采集系统往往难以胜任[1,2]。针对上述问题,提出了一种基于STM32+FPGA的数据采集系统的设计方案,该方案不仅能够完成对多路多样信号实时、精确地采集,而且具有高速信号处理和数据传输能力,具有集成化程度高、体积小、资源丰富、价格便宜等优点。

1 系统总体设计

在实际应用中,所采集的信号既有模拟信号,也有数字差分信号,并且有多通道、串并混合、数据量大等特点。为了满足需求,本文设计了图1所示的数据采集系统,它能根据需求进行6路±10V模拟信号,18路数字差分信号的采集、处理和实时传输。系统采用STM32+FPGA的组合方式,FPGA为Alter公司的EP1K50TC144器件,由STM32417给FPGA发送控制命令,通过FPGA内部的地址译码、逻辑控制以及数据缓冲实现信号采集[3],并通知STM32417对数据进行读取,最后,由STM32417对得到的数据进行处理和传输。

其中,STM32F417是意法半导体公司生产的基于ARMCortex-M4架构的微控制器,内核架构先进,性能优越,主频可达168MHz,执行效率高,具有较高的运算能力及数据处理能力,拥有丰富的外设接口和扩展功能[4]。在图1中,STM32F417与上位机之间的以太网通信,就是MII(medium independent interface)外接DP83848物理层芯片,通过相关配置后扩展实现的。

2 STM32与FPGA的接口设计

STM32F417与FPGA的接口方式有很多种,可以是串行的,也可以是并行的,考虑到FPGA在多路并行数据处理方面有明显优势[5,6],设计采用STM32F417的可变静态存储控制器(flexible static memory controller,FSMC)并行总线接口实现与FPGA的连接。

2.1 接口电路设计

FSMC是STM32系列采用的一种新型的存储器扩展技术,支持不同的外部存储器类型,其中就包括多种类型的静态存储器[7],因此,可将FPGA当成STM32F417的外部SRAM来配置,通过扩展出的数据/地址/控制三总线来实现操作,这样既能保证较快的操作速度,又具有很高的灵活性。接口电路硬件连接如图2所示。

图2 STM32F417与FPGA接口连接电路

将FPGA直接连接在STM32F417的FSMC总线上,FSMC提供了4个Bank用于连接外部不同的存储器,每个Bank有独立的片选信号,FSMC_NE3是Bank1第三区的片选信号,FSMC_NOE和FSMC_NEW分别是接口读写信号,根据应用需求,设计接口数据宽度为16位,地址线为10位,将数据线FSMC_D[15~0],地址线FSMC_A[9~0]连接到FPGA的I/O端口,寻址空间为1K字。除此之外,还有一些中断信号(INT),用于FPGA向STM32F417发送中断请求。这样FPGA就作为STM32F417的外设连接在了系统中,通过存储器读写指令就可以访问FPGA。

2.2 关于接口地址的STM32软件设计

在STM32F417内部,FSMC的一端通过内部高速总线AHB连接到内核Cortex-M4,另一端则是面向扩展存储器的外部总线,内部AHB总线的地址HADDR与FSMC总线地址存在一定的映射关系。

FPGA连接在FSMC的Bank1第三区,HADDR总共有28根地址线(HADDR[27~0]),其中HADDR[26~27]用来对Bank1的4个区进行寻址。当PFGA使用第三区时,对应的HADDR[27∶26]等于10。当Bank1在外接16位宽度存储器时候,只有HADDR[25∶1]是有效的,对应关系变为:HADDR[25∶1](FSMC[24∶0],由此可知,接口地址FSMC_A[9~0]对应的HADDR的地址为0x68000000~0x680007FE,在进行地址读写操作时,HADDR[0]并没有用到,相当于地址右移了1位,使得每次读写操作时,函数中的地址增量都为2。

3 数据采集的FPGA实现

3.1 模拟信号采集

根据应用需求,模拟信号采集选用MAXIN公司的12位AD转换芯片MAX196。该芯片有6个单端模拟输入通道,并且其量程范围、通道选择、工作方式均编程可控,转换时间为6μs,采样速率为100ksps,具有精度高、功耗低、开发方便等特点[8]。

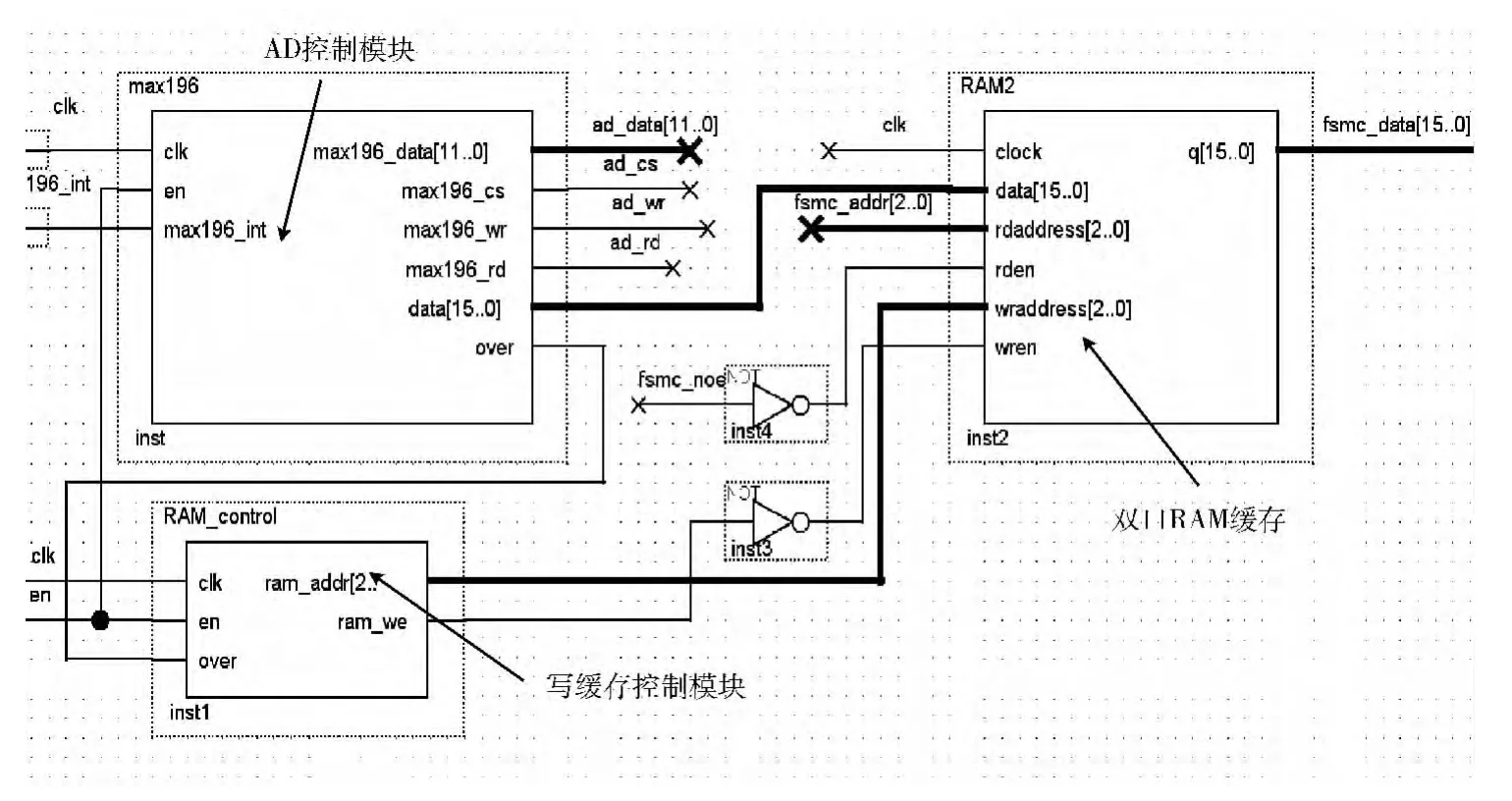

由于MAX196芯片是5V电压供电,为了解决逻辑电压匹配的问题,设计使用电压转换芯片SN74AHCT245PWLE来实现FPGA与AD的连接。由FPGA控制AD进行信号采集,使用其内部逻辑,完成芯片的配置、中断的响应以及转换结果的缓存,FPGA内部逻辑电路如图3所示。此逻辑电路主要由AD控制模块、写缓存控制模块和双口RAM缓存3部分组成。

3.1.1 AD控制模块

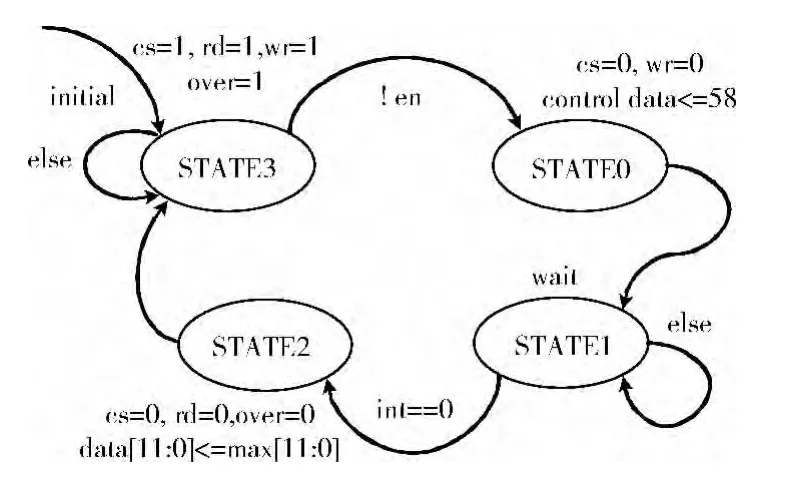

AD控制模块用来完成MAX196的采集时序的控制,为了确保时序控制的准确性和连续性,设计一个状态机,如图4所示,从STATE0~STATE3依次变化,整个过程对应一次完整的采集周期,系统中所有的系统时序由外部40 M有源晶振产生。

图3 AD采集内部逻辑电路

图4 AD采集控制状态机

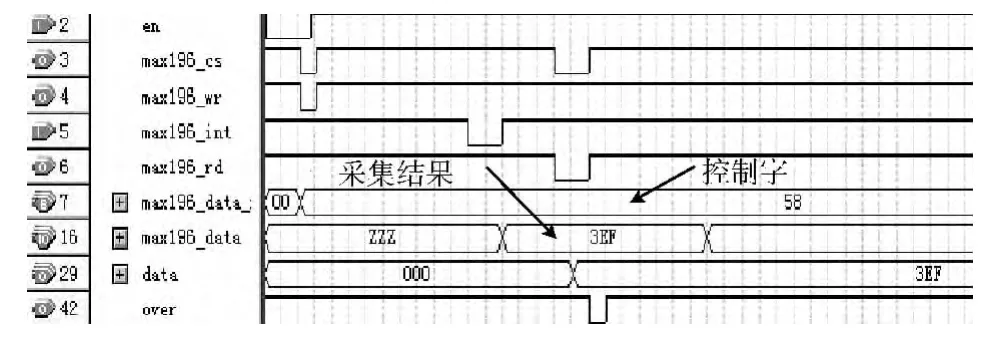

状态机的初始状态为STATE3,控制端口默认置高,在FPGA在收到STM32F417发出的采集命令en后,转入STATE0,输出脉冲(wr+cs)启动AD转换,并且向AD芯片写入8位控制字,完成初始化,然后,STATE1等待AD完成数据转换,转换结束时,AD产生中断信号int,接着进入STATE2,进而输出脉冲信号(rd+cs),读取转换的结果。该过程使用Verilog HDL语言来描述[9],时序仿真如图5所示。

图5 AD控制时序仿真

在实际应用中,AD的转换量程选择为±10V,双极性,使用内部转换模式,控制字后3位选择输入通道。由MAX196用户文档可知,通道0采集的控制字为0x58,假设得到的转换结果为0x3EF,为了下一步数据存储的需求,设计将数据缓存在寄存器data[11∶0]中,并产生一个over中断信号用于后期处理。

3.1.2 数据缓存

缓存的设置主要是解决AD连续高速的数据采集与STM32F417数据处理周期不匹配的问题,当AD完成一个通道的数据采集时,需要对数据进行缓存,考虑到FSMC总线接口的特点,在设计中,使用FPGA内部的双口RAM完成数据缓存[10],由Quartus II自带的IP核生成,其中RAM的读取端连接FSMC接口,而写入端连接AD,写缓存的地址通过写缓存控制模块进行控制。

信号en在启动AD控制模块的同时,将写缓存控制模块的地址清0,在over信号的触发下,地址加1,并且产生RAM写信号ram_we,寄存器data[11∶0]的数据写入RAM里,在连续6路的采集中,每一路的数据对应不同的地址,进而完成数据的缓存。时序仿真如图6所示。

图6 缓存读写时序

采集结束后,STM32F417通过读取存储地址分别得到6个通道的采集数据,进而完成下一步的数据处理和传输。

3.2 数字差分信号采集

数字差分信号的采集首先需要将差分电平转换成数字电平,选用MAXIN公司的MAX3362作为数字差分信号收发器。数字信号既有并行数据,也有串行数据,在同步触发脉冲的作用下,可通过FPGA内部逻辑电路对数据进行处理。对于15路并行数据,通过集成电路74373+74541的逻辑组合模块进行采集,在同步时钟sync1置高时将数据锁存至74373,而对于1路串行数据,则通过74164+74541的逻辑组合,在触发脉冲sync2的上升沿将数据由串行转为并行,STM32F417向对应的地址发出读指令,地址经译码后,选通缓冲器74541,从而得到相应数据。

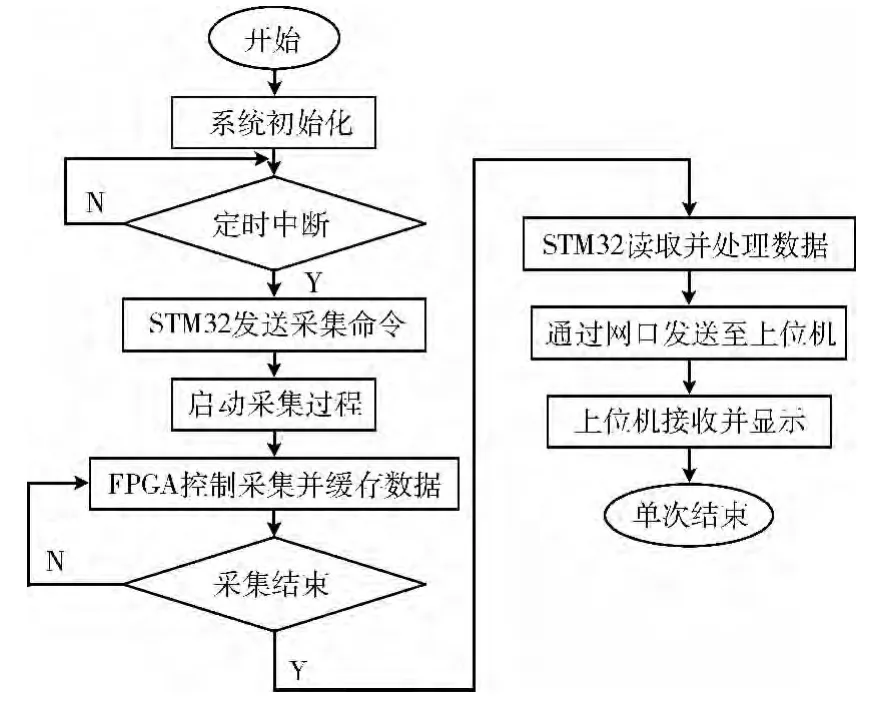

4 系统总体流程和结果测试

系统上电后,STM32和FPGA首先进行硬件初始化,其中FPGA通过PS的方式完成配置。STM32启动定时器产生定时中断,在中断响应中,发送开始采集命令,进而启动FPGA内部逻辑电路进行信号采集控制和数据缓存,在采集结束后,STM32响应FPGA发出的结束中断请求、读取数据、处理数据并将处理后的结果打包发送至上位机,最后,上位机接收数据并显示结果。

系统工作流程如下图7所示。

图7 数据采集系统流程

STM32F417通过网口将结果发送至上位机,其以太网通信是基于LwIP协议栈,利用改进后的UDP协议,实现数据实时可靠的传输。PC上位机则通过C++Bulider平台上的TNMUDP控件完成数据的接收。采集系统在实际实验中,控制MAX196完成6个通道采集的时间为约40μs,加上读取、处理、传输和显示的时间,系统可在50μs内完成全部采集和处理,设置定时器TIM1,使其50μs中断一次,并在中断响应中再次发送采集命令,实现精确时间间隔的连续采集。

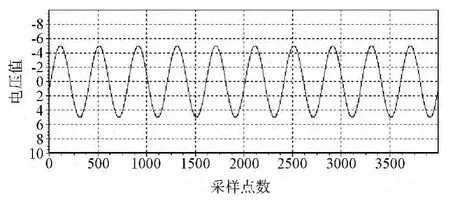

通过信号发生器,产生50Hz的正弦波,连续采集波形如图8所示。

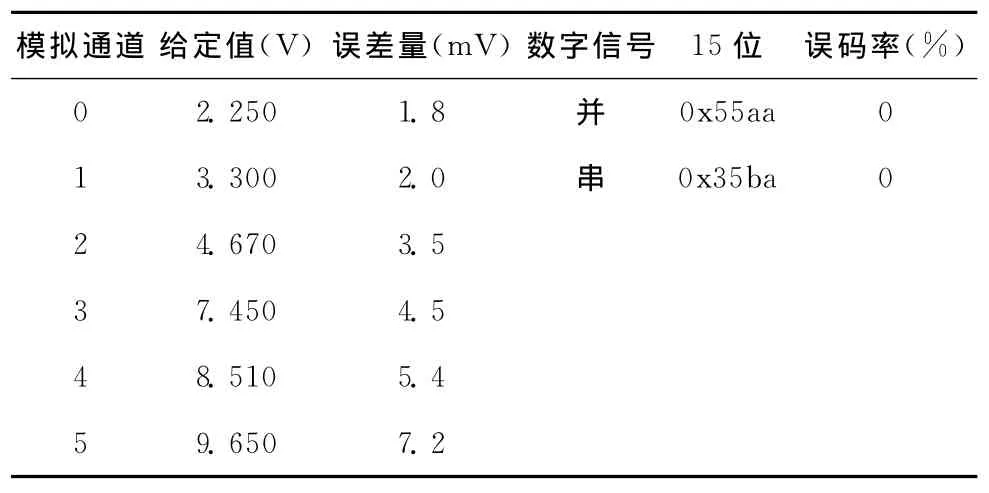

模拟通道和数字信号端口分别对给定值连续测试5000次,统计结果的误差和误码率见表1。

图8 50Hz正弦信号采集

表1 测试误差统计

测试的结果表明,模拟通道测量误差在10m V之内,数字信号端误码率为0,系统采集精度满足设计要求。

5 结束语

本系统很好地结合了STM32微控制器和FPGA可编程器件两者的长处,利用STM32硬件中的FSMC、Ethernet MAC、定时器等外设功能,以及FPGA灵活的逻辑可操控性,解决了系统接口设计、时序控制、组网传输等复杂问题,实现了火控系统信息多通道、多类型信号的实时采集,保证了精度高、传输快,实时处理的采集要求,为后续应用打下了良好的基础。同时,简化系统硬件设计,缩小了系统体积和开发周期,具有极高的性价比。本系统还保留了很大的灵活性,可轻松进行二次开发,组合架构可应用于不同的信号采集领域,有广阔的应用前景和参考价值。

[1]ZHU Xiaopeng,XIAO Tiejun,ZHAO Hui.System design of real-time data acquisition based on ARM and FPGA[J].Computer Engineering and Design,2009,30(13):3088-3089(in Chinese).[朱晓鹏,肖铁军,赵蕙.ARM+FPGA的实时数据采集系统设计[J].计算机工程与设计,2009,30(13):3088-3089.]

[2]XIAO Zusheng,CHENG Ming.Design of data acquisition and analysis system based on FPGA[J].Application of Electronic Technique,2009,35(3):49-50(in Chinese).[肖祖胜,程明.基于FPGA的数据采集分析系统设计[J].电子技术应用,2009,35(3):49-50.]

[3]ZHANG Yigang,SU Jungao,LIU Zhaoqing.Design of seeker da-ta acquisition system based on DSP and FPGA[J].Electronic Measurement Technology,2008,31(5):109-112(in Chinese).[张毅刚,苏俊高,刘兆庆.基于DSP和FPGA的导引头数据采集系统设计[J].电子测量技术,2008,31(5):109-112.]

[4]STMicroelectronics.STM32F415xx/417xx datasheet[OL].http://www.st.com/,2011:1-156(in Chinese).[意法半导体.STM32F415xx/417xx参考手册[OL].http://www.st.com/,2011:1-156.]

[5]XIN Junjun,HUANG Songling,LIU Lili,et al.Design of super multi-channel and high-speed data acquisition system based on FPGA[J].Electrical Measurement &Instrumentation,2008,45(10):34-36(in Chinese).[辛君君,黄松岭,刘立力,等.基于FPGA的超多通道高速数据采集系统设计[J].电测与仪表,2008,45(10):34-36.]

[6]YANG Guangyou,PAN Wu.Reconfigurable high-speed ethernet data acquisition platform design[J].Machine Tool &Hydraulics,2009,37(8):282-283(in Chinese).[杨光友,潘武.可重构的高速以太网数据采集平台设计[J].机床与液压,2009,37(8):282-283.]

[7]PAN Hui.NOR Flash memory extension based on STM32-FSMC[J].Microcontrollers &Embedded Systems,2009(10):31-33(in Chinese).[潘辉.STM32-FSMC机制的NOR Flash存储器扩展技术[J].单片机与嵌入式系统应用,2009(10):31-33.]

[8]Maxim Inc.MAX196/MAX198 datasheet[OL].http://www.maxim-ic.com/,2011:1-16(in Chinese).[美信公司.MAX196/MAX198参考手册[OL].http://www.maxim-ic.com/,2011:1-16.]

[9]DU Huimin,LI Youmou.FPGA design based on Verilog[M].Xi'an:Xidian University Press,2006:60-290(in Chinese).[杜慧敏,李宥谋.基于Verilog的FPGA设计基础[M].西安:西安电子科技大学出版社,2006:60-290.]

[10]LI Yanjun,GUO Zhenggang,ZHANG Zhixin,et al.Design of multi-channel synchronal data acquisition system based on FPGA[J].Microcomputer Information,2007,24(26):21-22(in Chinese).[李艳军,郭正刚,张志新,等.基于FPGA多通道同步数据采集系统设计[J].微计算机信息,2007,24(26):21-22.]