基于ARM-Linux的移动终端高稳定VGA接口设计

李 辉,庄 杰,王佳明

(电子科技大学通信与信息工程学院,四川成都611731)

0 引 言

目前很多微处理器芯片都集成了LCD接口控制器,如三星的S3C2440、S3C2410,但是不支持VGA接口。随着可穿戴技术的发展,头戴式显示器的应用越来越广泛。由于VGA接口的稳定性和可靠性,头戴式显示器基本上都是使用的标准VGA接口,同时VGA接口在其他领域也有着广泛的应用。在开发基于S3C2440的可穿戴便携式辅助维修系统时,针对在无线通信环境下使用头戴显示器的情况,需要一种适合于可穿戴系统且抗干扰能力强的VGA接口方案。传统的方案是利用FPGA/CPLD和SDRAM构造双口SRAM[1]。这种方案实时性好,性能高,但是硬件和软件设计比较复杂,应用于嵌入式系统相对成本比较高。文献[2,3]中提到的基于ADV7125、ADV7120的VGA接口方案比较适合嵌入式系统,相对成本低,实现简单,在不使用WIFI的环境下输出图像稳定,但是在无线通信环境下输出的信号会受到干扰,抗干扰能力达不到要求,例如广泛使用的天嵌公司开发的基于ADV7125的VGA转接板。为了满足S3C2440在无线通信环境下的VGA显示,笔者设计了一种基于CHRONTEL公司的CH7026芯片的嵌入式VGA接口方案。此方案对提高VGA接口的抗干扰能力具有重要意义。

1 系统总体设计

基于ARM-LINUX的VGA接口方案的总体结构如图1所示,微处理器S3C2440通过I2C总线对CH7026的各个寄存器进行配置,使其为VGA输出方式;S3C2440输出的数字信号经过CH7026转换后变成标准的VGA模拟信号,再通过DAC0-2送给VGA接口。微处理器输出的行、场同步信号经过CH7026的调整后,再通过HSO和VSO管脚送给VGA接口[4]。

图1 系统总体框架

2 器件介绍

本方案涉及的硬件主要包括电源芯片、CH7026视频芯片和LCD控制器。

2.1 CH7026芯片介绍

CH7026是一款高性能的视频芯片,该设备内的三片10位高速DACs具有灵活的输出能力,如单、双或三CVBS输出,色差端子输出,RGB输出和同步CVBS输出;其内嵌的一个16Mbit的SDRAM用作帧缓冲,它可以使图像在播放时更加流畅;其可编程的24位/18位/16位/12位/8位数字输入接口支持各种RGB(RGB565、RGB666、RGB888),YcbCr的多路输入;在电源管理方面,CH7026可以根据寄存器的检测结果管理DACs的开关。

CH7026具备强大的图像处理能力。CH7026嵌入了灵活的向上和向下缩放引擎,具有文本增强功能,支持像素的亮度,对比度,色调,饱和度调整为每个类型的输出,为RGB模式输出时,只支持亮度和对比度的调整;支持像素水平位置调整和垂直位置调整;支持帧速率转换、图像90/180/270度旋转。该设备能够编码视频信号并产生同步信号,支持480p、576p、720p和1080i高清格式。

2.2 LCD控制器简介

LCD控制器是S3C2440内部集成外设,支持TFT、STN两种类型的LCD[5],而TFT屏是目前嵌入式系统应用的主流,以下所讲述有关LCD控制器内容均针对TFT屏而言。LCD控制器的管脚分为数据端口和时序控制端口。管脚及其含义如表1所示。垂直同步信号VSYNC和水平同步信号HSYNC的详细定义参见文献[6],每发出一个脉冲都表示新的一行图像资料开始发送。

表1 LCD控制器管脚定义

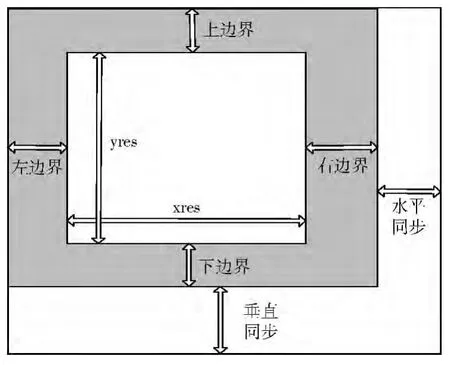

图2给出了LCD控制器中的主要参数,这些参数的具体含义参见文献[7]。在垂直同步和水平同步的头尾都必须留有回扫时间,也就是图2中的上、下边界,左、右边界,这些参数是决定图像输出效果的主要参数。

图2 LCD控制器主要参数

时序发生器产生控制信号给LCD驱动器,例如VSYNC、HSYNC、VCLK、VDEN和LEND信号。这些控制信号决定于REGBANK中LCDCON1/2/3/4/5寄存器。REGBANK中的LCDCON1/2/3/4/5寄存器都可以通过编程来配置,TIMEGEN就是其中的一个,通过编程控制,它可以产生适合不同的LCD驱动器的控制信号。水平同步信号(HSYNC)和垂直同步信号(VSYNC)可以通过LCD控制寄存器2/3中的HOZVAL字段和LINEVAL字段来配置。其中,HOZVAL字段、LINEVAL字段可以按照如下系列等式由LCD面板大小决定

VCLK信号的频率取决于LCDCON1寄存器的CLKVAL字段。如下等式定义了VCLK和CLKVAL之间的关系

帧率就是垂直同步信号的频率。帧率同VSYNC、VSPW(垂直同步信号的脉宽)、VBPD(垂直同步信号的后肩)、VFPD(垂直同步信号的前肩)、LINEVAL、HSYNC、HBPD(水平同步信号的后肩)、HFPD(水平同步信号的前肩)、HOZVAL、HSPW(水平同步信号的脉宽)和CLKVAL字段有关。多数LCD驱动器需要它们自己适当的帧率。具体关系如下面的系列等式所示

S3C2440中的LCD控制器支持1、2、4或8bpp(位每像素)调色显示和16或24bpp无调色真彩显示。S3C2440给LCD控制器提供了256色调色板。调色板支持的格式有5:6:5和5:5:5:1格式。另外,S3C2440还有电源使能功能。如果设置S3C2440的电源使能引脚,ENVID就会控制LCD_PWREN引脚的输出值。

3 系统电路设计

CH7026将LCD控制器输出的数字信号转变为VGA模拟信号输出,由于需要在无线移动通信环境下使用,在电路设计时特别考虑了电路的抗干扰能力。文献[2,3]中提到的方案都是直接使用LCD控制器输出的同步信号作为VGA接口的同步信号。此方案在没有高频信号干扰的情况下,能够正常的工作,但是在微处理器同时使用无线通信的环境下,LCD控制器输出的数字信号会受到高频信号的干扰,而同步信号又直接由LCD控制器输出到VGA接口,没有得到调整,图像就会随着干扰的强度出现不同程度的错位。CH7026是将LCD控制器输出的同步信号作为输入,经过调整后再输出到VGA接口,其具有调整同步信号的功能。这使得其具有更好的抗干扰能力,CH7026还支持外加晶振输入的功能,在电路设计时给CH7026芯片加了一个独立的14.318MHZ的晶振,调整同步信号需要用到该晶振,因此晶振的精度必须在±20%PPM以内。CH7026所有的电源管脚接了一个0.1微法的滤波电容,这样CH7026可以获得更稳定的电源,这在DACs工作时十分重要;另外在PCB设计时采用了地线敷铜的方式,它能减小底线阻抗,减小信号线的回流面积,提高抗干扰能力,具体电路如图3所示。

图3 VGA接口电路

CH7026工作需要3种电压,1.8V、2.5V、3.3V,分别由3种线性电源提供。在电源输入和输出端分别需要接滤波电容,大小电容值最好相差100倍以上,从而能够较好的滤掉高频和低频噪声。CH7026所有的电源管脚都接了一个0.1微法的电容,这些电容器应尽可能接近各自的电源和地引脚,同时使用短而宽的引线来减少引线引入的电感;ISET管脚用来设置DAC电流。在ISET和AGND_DAC之间应该连接一个1.2千欧的电阻,此电阻对于整个系统十分关键,必须保证该电阻的精度在1%以内。如果阻值过小,DAC的电流将过大,会导致输出图像过亮。如果阻值过大,结果将相反。同时这个电阻也应该尽可能靠近ISET引脚;SPD和SPC是CH7026的串行接口,SPD是双向数据线,SPC是时钟线。在电路中,SPD和SPC管脚必须接上拉电阻。如果没有接上拉电阻,CH7026将无法初始化,整个系统都无法工作;AS管脚是CH7026的I2C地址选择管脚,当AS接高电平时,设备地址为75h。当AS接低电平时,设备地址为76h;ATPG管脚需要通过一个10千欧姆的电阻接地;当有未使用的数据输入端口时,可以悬空或者接一个10 k电阻;另外CH7026最高可以接受从数字视频端口控制器输入的24位数据,三片10位高速DACs提供了灵活的输出能力,例如单、双或三CVBS输出,色差端子输出,RGB输出和同步CVBS输出。需要特别注意的是DAC0-2的3个引脚各需要接一个75欧姆的电阻,将输出电流转换为电压,同时起到阻抗匹配的作用。

4 系统软件设计

在软件设计时,需要根据实际需要将来配置LCD控制器参数,来满足相应设备的刷新频率。另外一个重要工作是需要编写CH7026的驱动程序,使其在VGA模式下工作。

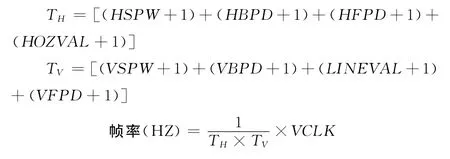

4.1 LCD控制器的配置

由于目标显示器的分辨率是640×480,刷新频率为60HZ,因此可以根据前文所述内容和实际需要来配置LCD控制器。对于寄存器LCDCON1,因为HCLK=100MHZ,640×480模式需要的VCLK=800×525×60=25.2MHZ,因此CLKVAL=1。由于LCD控制器的设置是针对TFT LCD,所以PNRMODE=0x03。选择BPP模式,BPPMODE=0x1100,即为TFT的16bpp[8];对于寄存器LCDCON2,VBPD=0x05。LINEVAL=480-1,VFPD=35,VSPW=4。对于寄存器LCDCON3,HBPD=50,HOZVAL=640-1,HFPD=80。具体实现方法是对内核驱动程序mach-tq2440.c进行修改来。LCD寄存器参数配置如图4所示。

图4 LCD寄存器参数配置

4.2 CH7026配置程序设计微

处理器S3C2440是通过I2C总线接口对CH7026的各个寄存器进行控制,CH7026一共有112个寄存器,但是其中大部分的寄存器不需要重新配置,采取默认设置值即可。在对CH7026配置时是调用内核中的I2C驱动程序[9]来完成数据的读写,在整个过程中CH7026是作为从设备,控制器是主设备。通过I2C总线对CH7026进行数据读写的过程分为以下几个步骤:当进行读操作时,微控制器先写从设备的I2C设备地址,然后写需要读取的寄存器的地址,最后再读取数据;当进行写操作时,先写从设备的I2C设备地址,然后写需要写入数据的寄存器地址,接下来就是写入需要写入的数据。其中CH7026的I2C设备地址由其管脚AS决定,当AS管脚为低电平时,ADDR=0x76h;当AS管脚为高电平时,ADDR=0x75h。此地址为7位地址,当进行读操作时需要将ADDR左移一位然后加1;当进行写操作时只需将ADDR左移一位。

CH7026的配置程序流程图如图5所示。

在调用I2C驱动时主要是对i2c_smbus_ioctl_bus这个结构体进行操作,这个是实现数据读写的基础。i2c_smbus_ioctl_bus结构体[10]的主要代码如下:软件执行的具体流程如下:

图5 CH7026配置程序流程

首先打开I2C驱动设备文件,如果打开成功开始检查I2C从设备是否为CH7026,具体过程是读取CH7026的寄存器0x00,然后将读取的值与CH7026的ID(0x54)进行比较,如果相等即为CH7026,否则程序结束。此模块的主要代码如下:

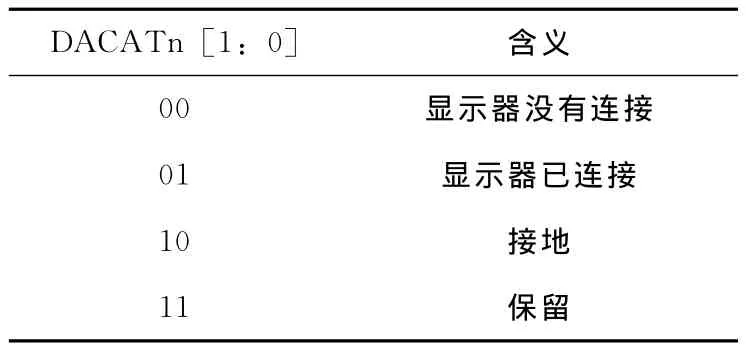

接下来检查VGA设备是否连接,具体的实现过程是读取寄存器0x7Fh的值,然后根据读取的值来判断VGA设备是否已经连接上。寄存器7Fh是制度只读寄存器,从低位到高位的具体含义为DACAT 0[0]、DACAT 0[1]、DACAT 1[0]、DACAT 1[1]、DACAT2[0]、DACAT 2[1]、Reserved、Reserved。各个DAC返回值的含义如表2所示。

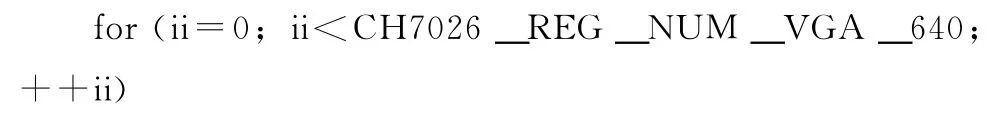

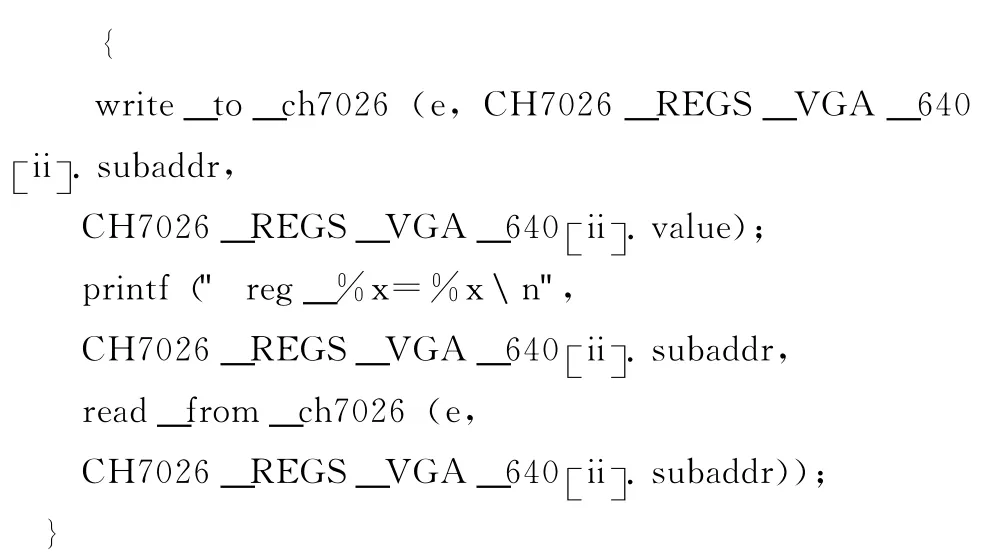

最后是整个配置流程中最为重要的部分,对CH7026的主要寄存器进行配置。配置文件先通过数据结构定义在头文件,然后调用编写好的I2C写函数将配置值写入到相应的寄存器。此过程的主要代码如下:

表2 LCD控制器管脚定义

5 测试结果

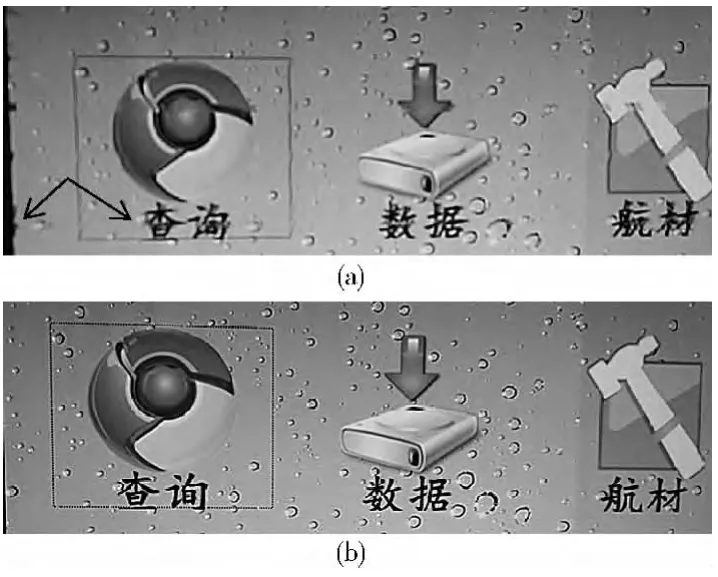

在完成硬件和软件设计后对整个系统进行了测试,测试结果如图6、图7所示,图6为示波器所测得的水平同步信号和垂直同步信号。信号波形稳定,其中水平同步信号为31.0585KHZ,垂直同步信号为59.272HZ,完全符合640×480分辨率的VGA时序要求。图7(a)是使用天嵌公司开发的基于ADV7125的VGA转接板在高频信号干扰下的输出效果,图7(b)为基于CH7026的VGA接口输出效果。对比发现,图7(a)边缘有明显的错位、残影,图像有明显的抖动波纹,而图7(b)图像清晰。测试结果表明笔者设计的方案在高频信号干扰下具有很强的抗干扰能力。

图6 VGA转接板同步信号时序

6 结束语

笔者所提出的基于ARM-LINUX的VGA接口方案,在软件设计上充分利用了Linux内核I2C驱动资源,避免了再次编写I2C驱动的重复工作;在硬件设计方面该方案有硬件设计可靠、抗干扰性强、成本低的优点。测试结果表明在进行VGA显示同时使用无线WIFI信号,该方案输出的图形清晰、稳定。与文献[2-4]中提到的VGA接口方案相比,该方案解决了S3C2440在进行VGA显示同时使用WIFI时的抗干扰问题。整个系统能够很好的满足可穿戴设备的头带显示器以及其他无线移动通信的VGA显示需要。

图7 VGA接口输出效果对比

[1]WANG Liang,LI Zheng,NING Tingting,et al.VGA display Chinese characters of the FPGA design and implementation of[J].Computer Engineering and Design,2009,30(2):275-277(in Chinese).[王亮,李正,宁婷婷,等.VGA汉字显示的FPGA设计与实现[J].计算机工程与设计,2009,30(2):275-277.]

[2]FU Zongbao,LIU Xiangyang,XIA Lingen.Based on ADV7120 embedded VGA interface design and implementation[J].Automation and Applications,2012,31(6):42-46(in Chinese).[付宗宝,刘向阳,夏林根.基于ADV7120的嵌入式VGA接口设计与实现[J].自动化技术与应用,2012,31(6):42-46.]

[3]ZHENG Tianhao,ZH ANG Hongyu,ZHANG Hongbin.Embedded system based on ADV7125 VGA interface design[J].Microcontrollers &Embedded Systems,2011,11(8):37-40(in Chinese).[郑佃好,张红雨,张洪斌.基于ADV7125的嵌入式系统VGA接口设计[J].单片机与嵌入式系统应用,2011,11(8):37-40.]

[4]FAN Jinlong,WANG Jingzhong.Based CH7004 VGA interface embedded system design[J].Electronic Design Engineering,2009,17(9):3-6(in Chinese).[范金龙,王景中.基于CH7004的嵌入式系统VGA接口设计[J].电子设计工程,2009,17(9):3-6.]

[5]XIE Zhaoli,JIANG Tao,LIU Liang,et al.The VGA interface based on ARM embedded system research and design[J].Journal of LCD to display,2007,22(6):761-764(in Chinese).[谢昭莉,蒋涛,刘亮,等.基于ARM嵌入式系统的VGA接口的研究与设计[J].液晶与显示,2007,22(6):761-764.]

[6]CHEN Gui,TIAN Xuelong,CHEN Nanxi.ARM embedded platform VGA interface design[J].Microcontrollers &Embedded Systems,2007(4):25-28(in Chinese).[陈桂,田学隆,陈南西.ARM嵌入式平台的VGA接口设计[J].单片机与嵌入式系统应用,2007(4):25-28.]

[7]FU Hong,LIU Guifang,LI Chunshan,et al.S3C2440 LCD controller configuration and application[J].Computer Engineering and Design,2010,31(11):2470-2472(in Chinese).[付虹,刘桂方,李春善,等.S3C2440的LCD控制器的配置与应用[J].计算机工程与设计,2010,31(11):2470-2472.]

[8]ZHU Liting,ZHAO Zhe.S3C2440 embedded VGA interface design[J].Hangzhou University of Electronic Science and Technology,2010,30(5):45-48(in Chinese).[朱丽婷,赵哲.S3C2440的嵌入式VGA接口设计[J].杭州电子科技大学学报,2010,30(5):45-48.]

[9]HE Yajun,DENG Feiqi.Embedded Linux I2C bus driver design[J].Computer Engineering and Design,2008,29(10):2517-2519(in Chinese).[何亚军,邓飞其.嵌入式Linux中I2C总线驱动程序设计[J].计算机工程与设计,2008,29(10):2517-2519.]

[10]DU Bo,FANG Xiangzhong.The embedded Linux system under the I2C device driver development[J].Microcomputer Information,2006,22(11):21-23(in Chinese).[杜博,方向忠.嵌入式Linux系统下I2C设备驱动程序的开发[J].微计算机信息,2006,22(11):21-23.]