LTE 基站中PDSCH 预映射算法的FPGA 实现

杜东振,朱宇霞,陈印锋

(1.武汉邮电科学研究院,武汉,430074;2.北京北方烽火科技有限公司,北京,100085)

0 引言

在LTE(Long Term Evolution,长期演进)基站系统中,使用FPGA(Field Programmable Gate Array,现场可编程门阵列)完成上行、下行基带算法的数据处理过程,已被大多数设备商所采用。FPGA 具有良好的时序控制能力,但由于FPGA 资源的有限性和基带算法时间要求的及时性,对FPGA 在数据处理过程中提出了越来越高的时间(速度)要求、空间(面积)要求。下文将详细介绍一种新的PDSCH(Physical Downlink Shared Channel,物理下行共享信道)资源粒子映射算法的实现过程,这种算法可以在实现资源粒子映射时,节省大量的FPGA 硬件资源。

1 预映射算法

PDSCH 算法处理分为比特级算法处理和符号级算法处理,其中,符号级算法处理的依次步骤为加扰、调制、层映射、预编码和RE(Resource Element,资源粒子)映射。调制是采用n 位二进制数作为输入,产生复值调制符号x=I+jQ 作为输出,IQ 两路数据在FPGA 中分别使用16 位的二进制数表示。PDSCH 算法使用到QPSK(2bits 映射为1 个复值调制符号)、16QAM(4bits 映射为1个复值调制符号)、64QAM(6bits 映射为1 个复值调制符号)三种调制格式。复值调制符号在层映射、预编码和RE 映射过程,映射完成后生成OFDM 符号时,根据时序要求需要对符号的复值调制符号32bits 数据进行缓存。

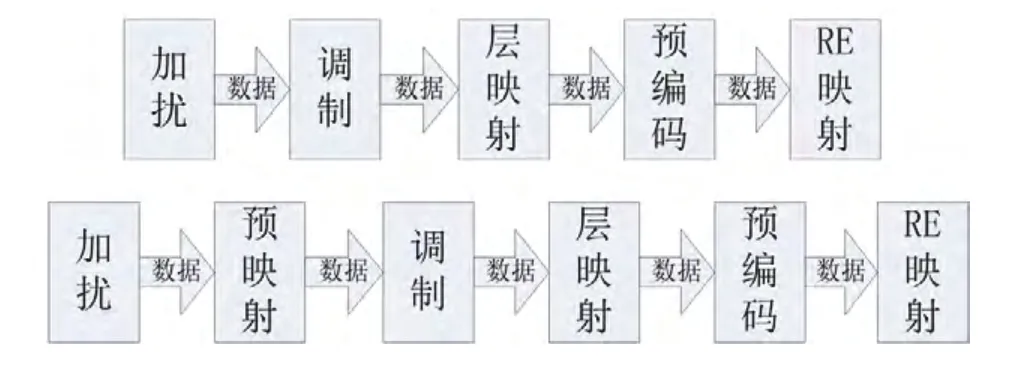

本文提出了预映射的概念,即在调制之前,完成部分RE 映射的工作,实现对比特数据存储代替符号数据存储。预映射根据PRB(Physical Resouce Block,物理资源块)索引值,将预映射数据以为PRB 单位进行预映射数据的存储,同时将与PRB 对应的调制格式、预编码格式及功控系数等符号级参数对应存储。存储完成后,当收到需要进行符号级算法处理的指令,以RE 为单位读取预映射数据,以PRB 为单位读取符号级参数,经过调制、层映射和预编码后进行RE 映射,生成OFDM 符号。预映射在PDSCH 符号级算法处理中的位置如下图:

图1 预映射在符号级处理过程中的位置

以64QAM 调制方式为例,调制前预映射数据占用6bits 存储资源,映射为复值调制符号后,需要存储32bits 的IQ 数据,因此此方法理论上可以减少81%左右的存储资源。

整个设计实现的过程,重点在于:1.预映射数据和符号级参数的同步;2.根据PRB 索引等参数确定数据和符号级参数的存储地址。下文将详细介绍预映射算法的设计过程。

2 模块设计

2.1 参数存储

参数存储模块完成PRB 索引值和符号级参数两部分的参数存储和读写操作。所需参数都由上层传送过来,首先需要使用分布式RAM 消除异步时钟域问题和输入输出位宽不一致问题。

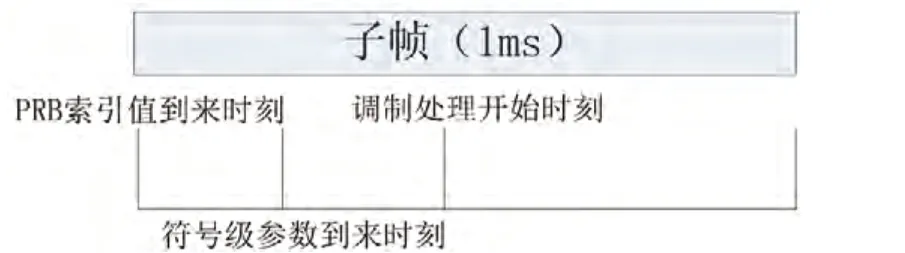

图2 子帧内PRB 索引值和符号级参数到来时刻

PRB 索引值在每个子帧的帧头时刻由上层传送过来,它指示每个PDSCH 所占用的PRB 资源等。根据PRB 索引值和PDSCH 参数,生成预映射数据和符号级参数的存储地址。

符号级参数在请求时刻到来,而进行符号级处理调制时刻将会受到比特级处理时刻影响,开始时刻不定。符号级处理时刻有可能与新的符号级参数到来时刻产生冲突,因此需要对符号级参数进行存储。对于一个子帧来说,PDSCH 数目不变,通过PDSCH数目和PRB 索引值来控制符号级参数的存储和读取。读取指令到来时刻,以PRB 为单位取出符号级参数,以完成数据的后续调制、层映射、预编码等处理。

2.2 预映射数据存储

PDSCH 的符号级处理调制算法存在QPSK、16QAM、64QAM 三种调制方式,分别需要将2、4、6 个预映射数据映射为复值调制符号。为了程序的流畅性,统一以6bits 预映射数据表示一个符号,QPSK 调制方式时,高4bits 添加0,低2bits 为有效数据;16QAM 调制方式时,高2bits 添加0,低4bits 为有效数据;64QAM 调制方式时,6bits 都为有效数据。

PDSCH 的预映射数据以PRB 为单位进行存储,首先,根据OFDM 符号个数开辟存储空间,将一个PRB 时域上的数据存储在相应的OFDM 符号对应的地址,然后在相应的地址内,将该PRB 下一个时域的数据按照一定时序存储,同一个PRB 在不同OFDM 符号上的预映射数据对应的存储地址不同。简化说明,我们假设现在需要生成OFDM 符号3、OFDM 符号4、OFDM 符号5,进行资源粒子映射时对应的PRB 的个数为4 个,索引号分别为1、5、9、13。存储预映射数据时,先存储PRB-1在OFDM-3上的预映射数据,然后存储PRB-1 在OFDM-4 上的预映射数据,然后存储PRB-1 在OFDM-5 上的预映射数据,PRB-1 上的预映射数据存储完毕。依此类推,然后存储PRB-5、PRB-9、PRB-13 上的预映射数据。

读取指令到来时刻,以RE 为单位,依次取出预映射数据即可。

2.3 RE 映射

类似于PDSCH 预映射数据存储和符号级参数存储,LTE 基站下行基带算法的其他物理信道/物理信号也完成相应的预映射处理。当需要执行RE 映射处理时,RE 映射模块计算出相应RE的属性值,即此RE 是用于哪一种物理信道/物理信号的映射,然后根据属性值输出读取指令,取出相应存储中的预映射数据和参数。

各个物理信道/物理信号的数据的比特级处理和符号级处理需要不同的时间,RE 模块发出的读取指令可以对齐,传输到各个物理信道/物理信号后,各延后N 个时钟周期再执行预映射数据和参数读取,使得各个物理信道/物理信号的复值调制符号到达RE 映射模块的时刻对齐的,也就可以无缝合并成为完整的OFDM 天线端口信号。这样,最大限度地提高了FPGA 处理效率,从使用上看,其占用的各种FPGA 资源相对来说会节省很多。

3 设计综合和仿真

使用VHDL 硬件描述语言编写程序,FPGA 芯片选用Xilinx Kintex-7 系列下的xc7k325t-1ffg900,在Xilinx ISE Design Suite 13.4 中选用122.88MHz 主时钟频率编译成功。采用Modelsim6.5 完成电路仿真,采用Matlab 完成数据分析。

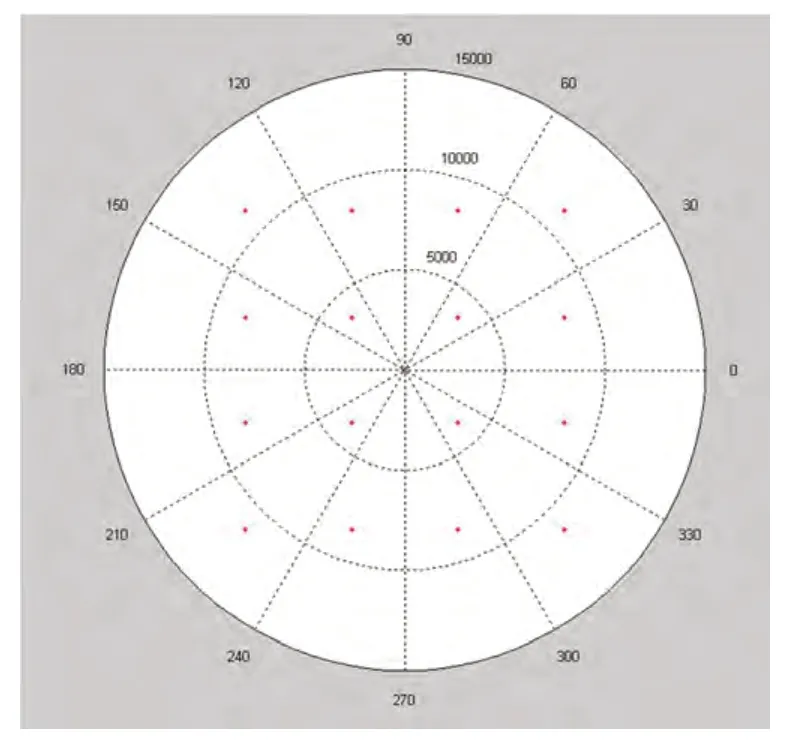

仿真采用的是16QAM 的调制方式,将输出的数据使用用MATLAB 做出16QAM 的星座图,如下图3 所示:

图3 16QAM 调制星座图

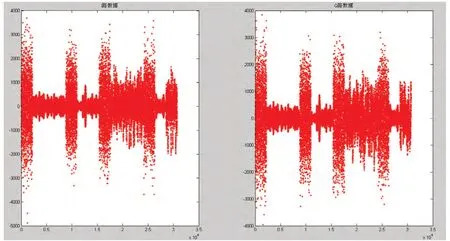

将生成的OFDM 符号取出,画出IQ 两路的时域图形,如图4所示:

由图3 可知,数据较为集中,可以看出结果具有良好的16 点的16QAM 调制效果;由图4 可知,时域图形具有良好的TD LTE信号特征,证明预映射算法是正确可行的。

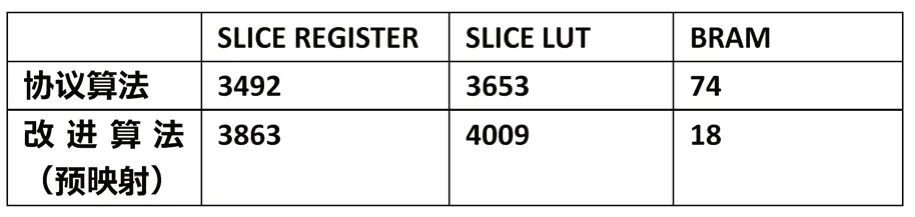

预映射算法占用的FPGA 资源如表1 所示:

表1 预映射算法占用FPGA 芯片资源表

由表1 可知,在寄存器和查找表资源表几乎没有增加的情况下,节省75%的RAM 资源,大大节省了FPGA 的存储资源。

4 总结

本文在现有的PDSCH 下行基带算法的基础上,提出关于PDSCH 资源粒子映射处理时更节省FPGA 资源的设计方法。这种思路也可以推广到其他物理信道/物理信号的资源粒子映射的实现,在FPGA 资源节省方面具有一定的借鉴意义。

图4 子帧0 的I 路和Q 路时域图

[1] 北京北方烽火科技有限公司.LTE 系统中资源粒子的映射方法和装置:中国,201310359326.9

[2] 3GPP TS 36.211,Physical Channels and Modulation (Release 8)[S]

[3] 3GPP TS 36.213,Physical layer procedures(Release 8)[S]

[4] 王映民,孙韶辉等.TD-LTE 技术原理与系统设计.人民邮电出版社,2010.