声无线传感网络节点数据高速存储实现*

刘泳锐,刘文怡,张彦军

(中北大学,电子测试技术国家重点实验室,太原030051)

无线传感器网络WSN(Wireless Sensor Network)是一种全新的信息获取平台,是传感器技术、嵌入式技术、现代网络及无线通信技术等多种技术的融合,能够实时监测和采集网络分布区域内各种被监测对象的信息,并将这些信息发送到网关节点,以实现对复杂范围内目标的监测与跟踪,具有快速展开,隐蔽性强等特点,有着广阔的应用前景[1]。随着无线传感网络节点采集数据量的不断增大,在节点中实现快速数据存储越来越重要。本文针对声音目标进行探测,完成了声无线传感网络节点的数据存储设计,实现了一种交错双平面高速存储技术在节点中的应用。

1 无线传感网络结构

无线声传感器网络结构如图1所示,它由大量廉价且具有传感采集、数据处理、无线通信、能量供给等模块的传感器节点组成。其中各节点是同构的,成本低,静态不移动,随意散布在要监测的区域,同时有足够能量保证正常工作。一个典型的无线声传感器网络结构包括声音传感器节点(Sensor节点)、汇聚节点(Sink节点)以及网络监控管理节点等。声传感器节点被随意的散布在监控区域以实现声音采集,数据预处理,并能够与汇聚节点组成一个自组织、多跳、无线的网络。汇聚节点是网络的处理中心节点,具有较强的处理能力、存储能力和通信能力、以及稳定充足的电源,但一般没有感知能力。该节点向监控管理节点上传各个节点的数据,并向各个节点下发控制命令。监控管理节点一般由普通的计算机系统构成,通过与汇聚节点通信来监控、管理目标对象的状态变化情况,从而对整个无线传感网络进行信息融合,得到整个监控区域的信息状态[2-3]。

图1 典型多跳无线传感器网络结构图

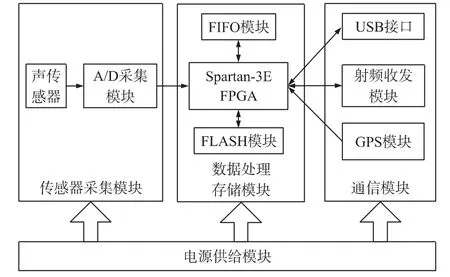

2 无线传感网络节点结构设计

无线传感网络节点一般由传感器采集模块、数据处理模块、通信模块、电源供给模块组成,如图2所示。传感器模块完成对监控区域的目标信息采集,并将模拟信号转换成数字信号提供给处理模块,本节点中针对声音信号进行采集。数据处理模块完成对数据的处理,信息识别和存储功能。通信模块完成节点间的信息交换。电源供给模块为整个节点提供能量保证,由于节点使用环境的限制,要求电源能提供高效稳定的能量。本次设计中要求对数据处理的同时进行数据的快速存储以便为试验数据分析提供保证,所以对FLASH的存储操作至关重要。

图2 声无线传感网络节点结构图

3 高速存储设计

3.1 高速存储方案设计

本次设计中,对于传感器节点来说,由于数据量较大和通信速率的限制,节点采集的数据、与邻近节点交换的数据需要在一定时间内进行保存,以实现数据处理和传输速率的匹配,并为后续试验分析提供数据保证。因此对数据进行存储显得尤为重要,本设计中在传感器节点上配置了一块非易失性NAND型FLASH存储模块。

FLASH是基于页编程、块擦除的,进行读、写、擦除都需要一定的时间,在这段时间内FLASH芯片内的被操作的Plane不能进行其他响应,这个等待时间会影响数据的记录速度[4]。本文选用三星公司的K9WBG08U1M芯片,为了提高数据的存储速度,采用交错双平面页编程方式进行操作,其主要工作思想是流水线操作。

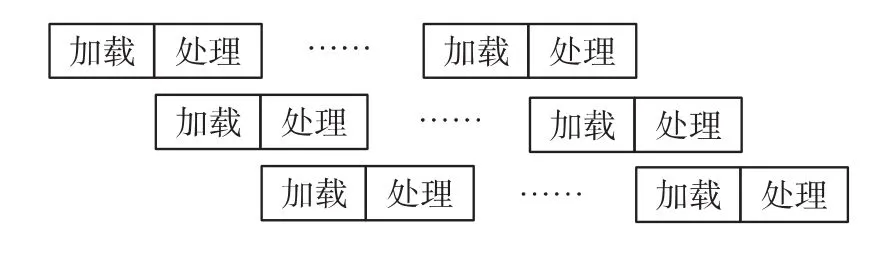

3.2 流水线操作模式

流水线技术可以提高系统频率,通常用在高速信号处理领域,如果整个设计是单向的并且可以分为若干个步骤进行处理,就可以用流水线技术提高系统工作频率[5-6]。主要方式是将一个整体过程从等待时间分开形成一个步骤,在等待时,执行下一个过程中的一个步骤。这样可以利用等待时间进行操作,提高器件的工作速度,如图3所示。

图3 多级流水线操作示意图

FLASH的流水线操作是利用芯片在进行一页编程的典型时间进行下一个Plane的页操作,实现时间上的复用。页编程分为数据写入寄存器和内部自动编程两个过程。数据写入寄存器过程可以分为发送编程命令、地址、数据。在完成写入寄存器过程后,芯片进入内部自动编程过程。在此期间立刻对另一个Plane进行数据写入寄存器操作。以此类推,从而实现数据的流水线写入操作。

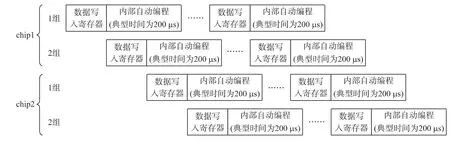

3.3 交错双平面操作

本次采用的4 Gbyte K9WBG08U1M芯片,它是由两片2 Gbyte的 K9WAG08U0M(分别为 chip1和chip2)组成的。本设计利用交错双平面页编程(Interleave Two-Plane Page Program)实现两个2 Gbyte K9WAG08U0M之间交错写入数据。每个K9WAG08U0M内部可以划分为4个存储平面(Plane),每个平面包含2 048个块和4224 byte的页寄存器,并且每个Plane可以进行单独的页编程和块擦除操作[7]。进行双平面操作时,必须将Plane0和Plane1分为一组(记为1组),Plane2和Plane3分为一组(记为2组)。只能同时对每一组里的两个Plane进行操作,如图4所示。不能交叉,如果同时对Plane0和Plane3、Plane1和Plane2操作是不正确的。

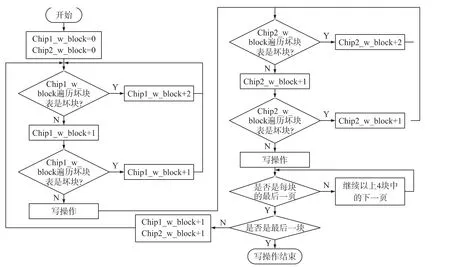

在进行交错双平面编程的时候,首先使能CE1,即选中chip1。对chip1中的1组进行双平面写入操作时,1组的每一次操作都将完成Plane0和Plane1中两个对称块上同一位置的一页写入操作(包括命令字、地址、数据),之后等待200μs的自动编程忙状态。这时对2组进行写入操作,其过程与对1组操作一样,之后等待200 μs。这时控制端使能CE2,即选中chip2,对chip2中的1组和2组进行操作,其过程与chip1中的操作一样,如图5所示。交错双平面页编程与普通的FLASH页编程(Page Program Operation)比较可知,普通的页编程在写入一页数据后要等待200 μs的页编程时间;而使用交错双平面页编程时,是在写入两页后才有一次真正的200 μs的页编程时间,节省了一次页编程时间,交错双平面页编程操作流程如图6所示。

图4 K9WBG08U1M型内部阵列结构图

图5 交错双平面页编程写操作原理图

图6 FLASH交错双平面页编程操作流程图

采用交错双平面操作,其写入速度的理论极限值为40 Mbyte/s。假设数据以40 Mbyte/s的速度写入,完成第一组某块的一页寄存器操作后,该组将进入200μs的等待时间,此时依次对chip1中的2组、chip2中的1组、chip2中的2组进行写入操作[8]。整个写入时间为:

6 ×4 096 byte/40 Mbyte/s=585.9 μs>200 μs

由此可见,在第四个组完成写入寄存器操作后,第一个组的等待时间已经结束,可以继续从第一组开始写入。整个过程中没有等待时间。由于极限速度是40 Mbyte/s,本设计为了增加冗余,FPGA控制器对FLASH以30 Mbyte/s的速度进行写入操作。

4 实验结果

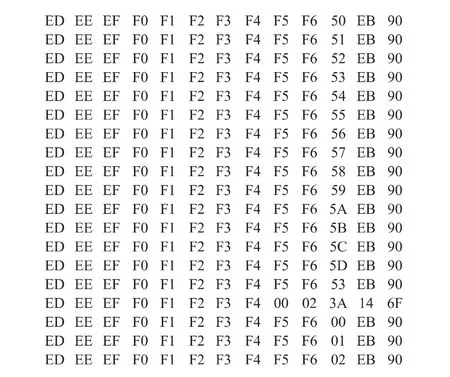

试验时,在对节点的FLASH完成无效块检测后,采用30 Mbyte/s的速度对FLASH进行交错双平面写入操作。写入操作上位机截图如图7所示。最后将存入FLASH中的数据通过FPGA经由USB控制芯片(CY7C68013)读取到上位机,进行数据分析。

图7 上位机写入操作

使用递增数对FLASH进行写入操作,递增数的数据格式为:大帧=96×小帧(250 byte),小帧格式为:递增数(00-F6)、1位帧计数(从00开始)和小帧帧标志(EB 90);大帧格式为:当记到96个小帧时,写3位帧计数(从00 00 00开始)和大帧帧标志(14 6F)。图8为上位机读取的递增数。

图8 上位机读取的递增数

5 结束语

该系统对声音无线传感网络节点数据存储进行设计,利用交错双平面页编程操作实现了对FLASH的高速数据存储。有效地保证了节点因数据量大和传输速率受限而引起的数据不能及时处理和交互的问题。通过试验表明,该存储方式稳定、可靠,为整个试验系统的正常工作和后续分析提供了有力的保障。

[1]赵海,赵杰,刘铮,等.一种无线传感器网络节点的设计与实现[J].东北大学学报(自然科学版),2009,30(6):809-812.

[2]佟吉钢,张振新,陈增强,等.基于FPGA的无线传感器网络节点设计[J].传感技术学报,2009,22(3):417-421.

[3]梁小满,马行坡.无线传感器网络数据存储技术研究进展[J].计算机应用研究,2009,26(2):439-443.

[4]陆浩,王振占.高速大容量固态存储器设计[J].计算机工程,2011,37(15):226-231.

[5]吴萌,刘波.高速、大容量视频数据存储、传输系统设计[J].电子器件,2009,32(3):638-642.

[6]李超,王虹现,邢孟道,等.高速大容量FLASH存储系统设计[J].火控雷达技术,2007,36(1):83-88.

[7]Samsung Electronics K9XXG08XXM Data Sheet[EB/OL].http://www.samsung.com,2006,12.

[8]赵海舰,甘萌.嵌入式系统中的FLASH编程技术研究[J].计算机工程与设计,2005,26(11):3006-3009.