低温沉积SiO2薄膜工艺的研究

李璟文,周 艺,吴 涛,章 强

(中国科学院苏州生物医学工程技术研究所,江苏苏州215163)

1 引言

等离子体增强化学气相淀积SiO2薄膜由于其沉积温度低、速率快、折射率一定范围内易调、覆盖性好、介电强度高、对光的散射吸收小等性能而广泛应用于微电子领域。它借助微波或射频等方式使含有薄膜原子组成的气体电离,在局部形成等离子体并在基片反应,从而形成薄膜,由于等离子体化学活性很强,因此反应可以在较低温度下进行。为了获得高质量的SiO2薄膜,目前一般的沉积温度在200~350℃[1,2],虽然远低于传统的化学气相沉积法(700℃)[5]及光化学气相沉积法(500℃)[4],但是,在柔性电子、MEMS器件的应用中,由于聚合物、有机材料很难承受200℃以上的高温(通常在180℃以下)[6-8],这就限制了SiO2薄膜在以上场合的应用。尝试在150℃低温下沉积高质量的SiO2薄膜,测试了薄膜厚度、均匀性、折射率、沉积速率等参数,讨论了气体流量对薄膜沉积速率、折射率的影响,分析影响薄膜应力的参数,并通过调节射频功率优化薄膜应力,最终获得接近零应力的SiO2薄膜,同时该薄膜具有良好的附着力及抗蚀性能。

2 试验装置与方法

SiO2薄膜的沉积试验采用平行极板式等离子体增强化学气相沉积系统。极间距设定为11 mm,底电极接地,并配有加热装置,温度范围。频率为13.56 MHz的射频信号经匹配网络加载到上极板,设备本身的Load Lock腔室极大程度地保证了工艺稳定性。

沉积SiO2薄膜采用的反应气体为稀释至5%的SiH4、N2O及高纯N2。基片采用三寸GaAs(E100)晶片。

均匀性测试采用九点法测试,即在基底选取均匀分布的九个点,分别测试各点的厚度值,利用广泛采用的非均匀性公式(最大值-最小值)/2倍平均值得到。其中,薄膜厚度及折射率均采用Filmetrics F40-UV膜厚仪测试。

SiO2薄膜的应力σ(Pa)可以凭借测量基片曲率在薄膜沉积前后的改变按(1)式计算。即:

式中:E为基片杨氏模量,Pa;v为基片的Poisson比;H为基片厚度,μm;T为沉积薄膜厚度,μm;R1为沉积前的晶圆曲率半径,μm;R2为沉积后的晶圆曲率半径,μm。实验中采取GaAs基片杨氏模量为85.3 GPa,v=0.31。

SiO2薄膜的附着力采用常用的Scratch&Tape方法,即首先用金刚石刻刀划开基片上的SiO2薄膜,观察薄膜有无开裂或脱落,然后使用胶带贴住该区域并快速撕掉胶带,检查胶带上有无SiO2薄膜碎片,薄膜边缘有无SiO2薄膜脱落,从而判断SiO2薄膜的附着力。若薄膜无开裂脱落,胶带上无薄膜碎片,则说明薄膜附着力良好。SiO2的抗蚀性能在十倍稀释的氢氟酸缓冲液中进行。

3 结果与讨论

3.1 薄膜均匀性及折射率

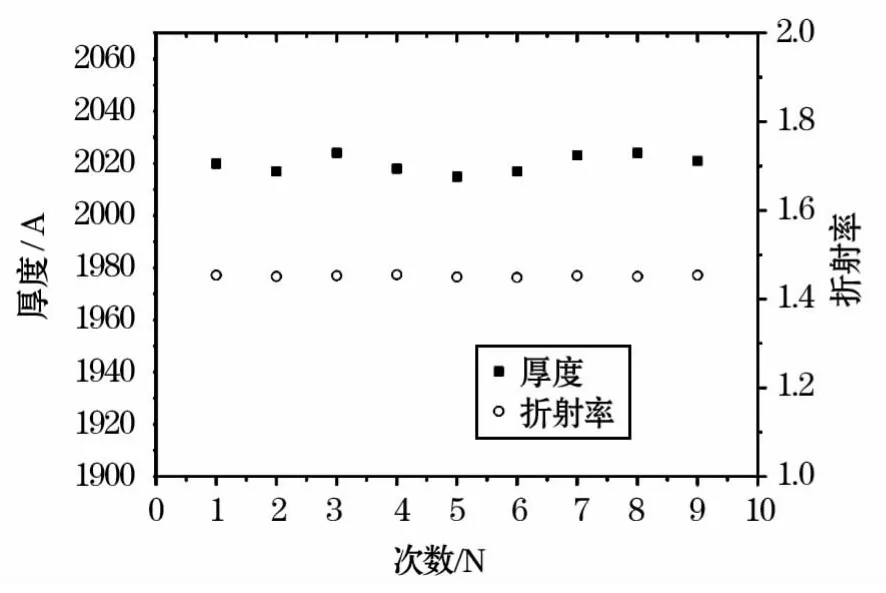

衬底采用 GaAs(E100)三寸基片,沉积初始条件为:功率 200 W,温度 150℃,SiH4流量 8.45×10-5Pa·am3/s,N2O 流量 8.45×10-4Pa·am3/s,N2流量 8.45×10-5Pa·am3/s,压力 150 Pa,沉积时间 600 s。薄膜厚度及折射率的九点采样分布如图1所示:

薄膜厚度为2 020 A,均匀性优于3%,沉积速率约为20 nm/min,折射率为1.45,均匀性优于±0.004。在此沉积条件下获得的薄膜折射率偏低,主要是由于薄膜致密性较差,一方面是由于SiH4流量不足,薄膜含硅量较少,另一方面是由于沉积温度较低,样品表面原子的运动活性较低,导致薄膜致密性不高。为了获得与块体材料折射率相近的SiO2薄膜,首先尝试通过提高SiH4流量,提高硅原子密度,从而提高折射率。将SiH4流量提高至1.69×10-4Pa·am3/s,其余条件不变,薄膜厚度及折射率分布如图2所示:

图1 SiO2薄膜厚度及折射率分布

图2 SiO2薄膜厚度及折射率分布图

可见,SiH4流量增大后,薄膜中硅原子含量增加,薄膜更加致密,折射率也响应增加至1.46,与SiO2块体材料相当。同时,沉积速度也随流量增加正比例提高,由20 nm/min增加至40 nm/min。

3.2 应力

在SiO2薄膜的应用中,为了避免薄膜翘曲导致器件失效,希望获得应力尽可能低的薄膜。由于PECVD沉积二氧化硅薄膜在高频和低频条件下分别呈现张应力和压应力[1],因此,采用高低频混合沉积的方法可以使应力相互抵消,即通过对混频工艺中的低频和高频的时间比进行控制,从而可以在一定程度上减小薄膜应力,但是在工程领域,这种工艺的稳定性及可靠性有待进一步验证,而且很少有化学气相沉积设备配备双频源。因此,主要针对单一的射频源,尝试通过调节射频功率的大小优化薄膜应力。

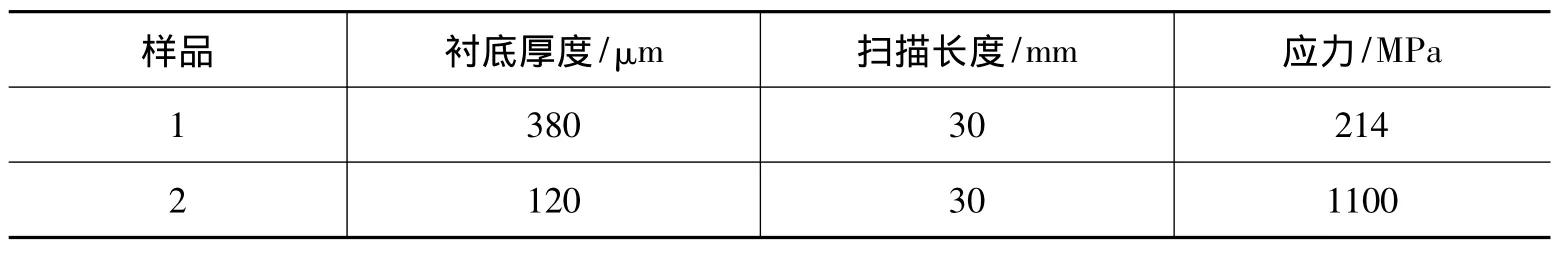

由于采用的应力测试手段会受基片本身的厚度、曲率半径的影响,为了尽量避免衬底对薄膜应力的影响,我们首先做了验证,即在同一批试验中,同时放入两片厚度分别为380 μm和120 μm的GaAs基片,沉积结束后,分别测试SiO2薄膜的应力。如表1所列:

表1 基片厚度对薄膜应力的影响

可以看出,在同等条件下,衬底越薄,应力越易体现,对SiO2薄膜真实应力的影响也越小。因此,采用120 μm的GaAs基片,通过调节射频功率优化薄膜应力。

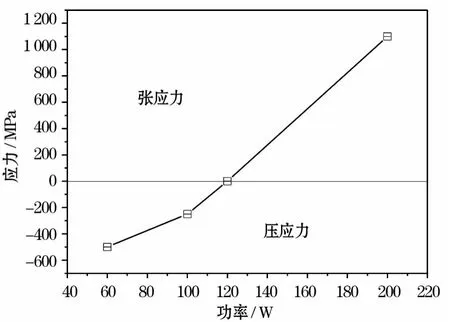

由于功率较低时薄膜一般呈现压应力,而功率较高时薄膜通常呈现张应力,这是由于在功率较低时,等离子体密度有限,发生化学反应的原子有足够的时间有序的排列形成致密的氧化硅薄膜,随着功率的增大,等离子体密度随之增大,发生表面淀积反应的分子快速增加,原子将没有足够的时间进行排列,而是无序性增强,压应力随之减小并逐渐转变为张应力,并随功率的继续增加而增加。

在200 W的功率下,薄膜表现出很大的张应力,当调整功率为60 W时,又表现为较大的压应力,因此初步判断零应力点应处于60 W与120 W之间,通过两次调试,最终发现SiO2薄膜的零应力点位于120 W附近,如图3所示。

图3 SiO2薄膜应力与射频功率的关系

此外,还可以通过调节沉积压力、衬底温度、气体配比等参数调节SiO2薄膜应力[3]。当气压较低时,离子对样品表面的轰击作用较为明显,达到一定程度后会打破SiO2薄膜中的原子键,造成膜膨胀,引起压应力,这与低频下薄膜产生压应力的原因是一致的。

从低温到高温,应力的变化趋势是从压应力变化为张应力,压应力是由于膜在沉积过程中,到达薄膜表面的离子的横向移动速率太小,来不及到达其晶格位置,被后来的离子覆盖,这样离子就相当于被阻塞在某一位置,最终会膨胀形成压应力。张应力的形成是在膜的形成过程中,由于反应中间产物的气化脱附,而参加沉积的原子,其迁移率不够大而来不及填充中间产物留下的空位,最后形成的膜会收缩产生张应力。

3.3 附着力

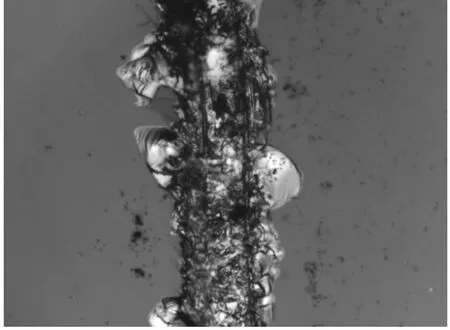

为了检验低温沉积SiO2薄膜的附着力,采用前面所述的Scratch&Tape方法进行了相应测试,测试结果如图4所示:

图4 薄膜附着力测试

可以看出,薄膜在金刚石刻刀划过后无龟裂、脱落现象,使用胶带贴住此区域并快速撕掉,胶带上无薄膜碎片,因此薄膜具有优越的附着性能。

3.4 刻蚀速率

测试PECVD淀积SiO2薄膜的抗蚀性能,室温26℃下,利用十倍稀释的40%HF溶液进行试验,刻蚀时间为20 s。图5所示是在三寸片随机均匀取点在刻蚀前后的数据,刻蚀速率约为3 400~4 000 A/min,并保持很好的刻蚀均匀性。与CVD沉积的SiO2薄膜相比[2],抗蚀性能较差,这一方面是由于PECVD淀积的SiO2薄膜针孔较多,结构较为疏松。另一方面,由于沉积温度较低,薄膜致密性较差,因此抗蚀性能较差。

4 结论

尝试在低温150℃下利用PECVD沉积SiO2薄膜,测试了薄膜的厚度、均匀性、折射率、沉积速率等参数,通过调节射频功率优化薄膜应力,获得了接近零应力的SiO2薄膜,此外,该薄膜还具有良好的附着力,较好的抗蚀性能。由于这种工艺温度较低,可以应用于温度敏感材料或器件,特别是对于柔性电子器件等涉及聚合物材料的应用。此外,还可以应用与目前柔性电子器件、柔性显示等领域绝缘层及钝化层材料。

由于沉积温度低及PECVD方法本身的不足,沉积的SiO2薄膜呈多孔状,致密性劣于热氧化及传统CVD方法,因此抗蚀性能也较差,对低温沉积的SiO2薄膜进行退火处理,一定程度上可以实现致密化,提高密度及抗蚀性能。

图5 SiO2薄膜BHF刻蚀前后薄膜厚度

[1]Adams A C,Alexander F B,Capio C D,et al.Characterization of plasma deposited silicon dioxide[J].J.Electrochem.Soc.1981,128:1545-1551.

[2]Nguyen S V.High-density plasma chemical vapor deposition of silicon based dielectric films for integrated circuits[J].IBM Journal of research and development.1999,43:109-126

[3]吕文龙,罗仲梓,何熙,等.PECVD淀积SiO2的应用[J].功能材料与器件学报,2008,14(1):33-37.

[4]Liu C H,Chang C S,Chang S J.The characteristics of photo-CVD SiO2and its application on SiC MIS UV photodetectors[J].Materials Science and Engineering,2003,100(B):142-146.

[5]关旭东.硅集成电路工艺基础[M].北京:北京大学出版社,2006:139-179.

[6]Mark Meitine ,Andrei Sazonov.Low Temperature PECVD Silicon Oxide for Devices and Circuits on Flexible Substrates[C]//MRS Proceedings.2003,769.

[7]Kan Zhang,Jung-Hun Seo,Weidong,et al.Fast flexible electronics usingtransferrable silicon nanomembranes[J].J.Phys.D:Appl.Phys.2012,45(14):143001-143014.

[8]Ming Ying,Andrew P Bonifas,Nanshu Lu ,et al.Silicon nanomembranes for fingertip electronics[J].Nanotechnology.2012,23(34):344004-344010.