多速率调制解调器设计与实现

余金磊,冯晓东

(1.中国电子科技集团公司第五十四研究所,河北石家庄 050081;2.总参信息化部驻石家庄地区军事代表室,河北石家庄)

0 引言

现代通信系统中对多速率传输的需求日益凸显,多速率传输在3G通信网、无线局域网等通信系统中得到了应用和推广。

在以往的多速率传输系统中,为保证系统性能,通常的做法是在射频通道设置一组滤波器,依据不同的传输速率进行切换,系统的复杂度增加,成本升高;如果不设置滤波器组,则系统的性能无法得到保证。

现代大规模集成电路特别是现场可编程门阵列(FPGA)的出现使通过软件无线电的方法实现多速率传输成为可能[1]。在FPGA内部通过算法实现不同信息速率的同频带传输能够大幅简化射频通道的设计,而付出的代价仅仅是算法复杂度的提高,相关算法的实现可以调制解调器中进行。

1 调制解调器设计

某微波通信系统中包含有:320 kb/s、640 kb/s、1280 kb/s、2560 kb/s、10240 kb/s 和 40960 kb/s 6种信息速率。使用直接序列扩频技术(DSSS)选择不同长度的扩频码将 320 kb/s、640 kb/s、1280 kb/s、2560 kb/s的传输速率既码片速率扩展至20480 kb/s,使用卷积编码将10240 kb/s变换至20480 kb/s,调制方式使用BPSK;40960 kb/s使用QPSK调制,实现了不同信息速率在相同的带宽上传输。直接序列扩频技术可以提高通信系统的抗干扰和抗多径传输效应的能力[2],而采用卷积编码可以很容易地降低指定差错性能时所需要的信噪比[3]。

多速率兼容调制解调器采用一体化和小型化设计,将调制、解调和中放AGC等功能模块集成在一起。使用大规模集成电路、大容量FPGA,全数字地实现信息的扩频/编码、基带成型、IQ调制、相干解调、解扩/解码等功能,扩频、解扩或者编码、解码都在调制解调器中使用FPGA实现,具有集成度高、可靠性高、稳定性好以及设置灵活等优点。

多速率兼容调制解调器信息处理流程图如图1所示。

图1 调制解调器信息处理流程图

不同速率的信息码流通过直接序列扩频或卷积编码完成速率兼容,经过基带成型后送给IQ调制器转化为中频信号送给发信机。

来自收信机的中频信号经过中放AGC转化为恒幅信号,中频信号在复数混频器中去掉相位误差转换为零中频信号,在解扩器中去掉扩频调制后提取定时信息和载波误差,最后进行判决和差分译码后送出数据和时钟,恢复出使用直接序列扩频进行速率兼容的信息码流。去掉相位误差的零中频信号经过内插后送给均衡器完成时域均衡,分别进行差分译码和卷积/差分译码恢复出另外2种速率的信息。

2 实现

2.1 调制器

由图1可知,调制器中直接序列扩频和卷积编码是实现速率兼容的关键。

2.1.1 PN序列的相关性

信息速率320 kb/s、640 kb/s、1280 kb/s、2560 kb/s分别使用64位、32位、16位、8位的 PN序列实现扩频,由于PN序列较短,扩频码的自相关特性不是很理想,以16位PN序列{1100110101000011}为例,其自相关性如图2所示。

图2 16位PN序列的自相关性

观察图2可知,当接收码流相位与本地PN序列相位完全对齐时,相关峰值是理想的;但在相位未对齐的时刻,或码元相位跳变时刻也会出现一些小的相关峰值,这些峰值最大时达到了相位对齐时峰值的一半,这些峰值的出现会影响解扩时定时同步的提取,因此解调器如何提取定时信息就成为一个必须要考虑的问题。

2.1.2 卷积编码

卷积码可以简单的用3个整数(n,k,K)来描述,其中k/n表示卷积码的编码效率,K称为约束长度,表示在编码移位寄存器中k元组的级数,也即与编码器输出有关的输入数据的个数。考虑速率兼容,编码增益和译码的复杂度等因素,在设计中使用一种短约束长度的卷积编码,其编码矢量为{ 1001111}和{ 1101101},这是一种得到广泛应用的短约束长度的最佳卷积编码[1],其编码器如图3所示。

图3 卷积码编码器

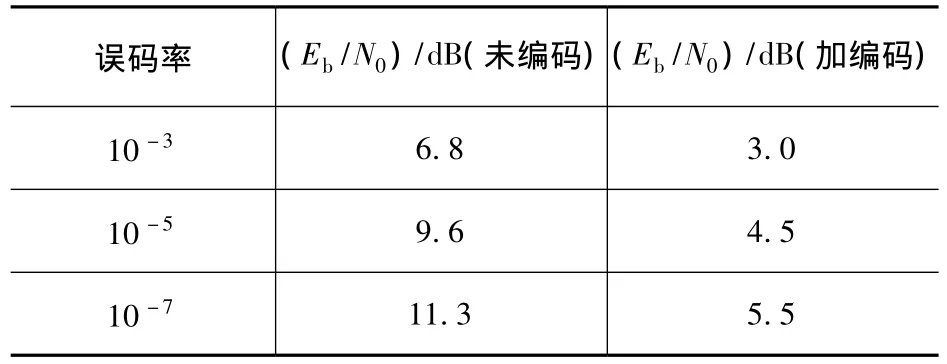

由图3可知,(2,1,7)卷积编码实现简单,1/2的编码效率能够很好地实现速率兼容的目标。此外,卷积编码还能够带来一定的编码增益。表1列出了经高斯信道传输、采用软判决译码的(2,1,7)卷积编码,与未编码的相干BPSK相比的差错性能改善。

表1 (2,1,7)卷积编码的差错性能改善

2.2 解调器

解调器中的关键是如何实现扩频解扩和卷积译码。

2.2.1 扩频解扩

直接序列扩频信号的捕捉同步方式有很多种,最常用的是序列相关积分处理法和匹配滤波器法[4-6]。两者各有优缺点,滑动相关器法硬件电路简单,码长可以较长,但同步速度慢,同步时间与伪码长度有关,码序列越长同步时间越长;匹配滤波器同步速度快,同步时间仅为一个伪码周期,但在伪码长度较长时需要消耗较多硬件资源,设计的主要代码实现在大容量FPGA中进行,资源充足,实现较为简便。因此采用数字匹配滤波器(DMF)来实现扩频信号的解扩。

2.2.2 定时提取

定时同步采用PN码和数据符号同步的方式,即一个数据符号的转换点对应着一PN码周期的转换点,DMF完成一次PN码解扩,同时意味着获取了数据符号的位同步信息,再附加一定的数据位时钟恢复和保护电路,就可以获取精确的数据位同步,如图4所示。

图4 定时同步提取原理框图

数字匹配滤波器输出的相关峰信号经过取绝对值去掉相位信息后送给去直流梳齿滤波器,经过梳齿滤波器进行提纯后在一个数据符号内寻找最大值,在门限判决模块内将找到的峰值和内部存储器存放的门限进行比较,若峰值大于给定的门限值,则输出一个以峰值为中心4个采样点宽度的窗口信号,DMF输出的相关峰信号在此窗口内寻找最大值,输出即为位同步信号。

时间窗的作用除了时钟恢复和保护外,还可以屏蔽掉出现在时间窗以外的虚警信号[7]。时间窗的宽度选择,即时间窗内包含的样值数目,对时钟的性能影响很大。时间窗越宽,跟踪范围越大,但是发生虚警可能性越大。

2.2.3 卷积译码

卷积码常用的译码方法有维特比译码和序贯译码。维特比译码的算法复杂度与信道特性无关,却随约束长度呈指数级增长;序贯译码受约束长度影响较小,但在信噪比较低时有可能导致译码器的溢出[8]。比较2 种方法的优缺点,结合(2,1,7)卷积编码约束长度较短的实际,本设计中采用维特比译码。

由图1可知均衡器的输出既是译码器的输入,均衡器的输出有2种构造方式:一种构造方式是硬判决,即直接输出“0”或者“1”;另一种构造方式是软判决,即量化后的有噪声信号。对于高斯信道来讲,3 bit量化的软判决维特比译码相较硬判决维特比译码能带来2 dB的性能提升,付出的代价仅仅是增加少许的计算量[9]。Altera公司的FPGA内嵌有维特比译码IP核,因此在算法实现时需要保证的就是译码器输入的时序和逻辑关系。

3 测试验证

数字微波通信设备接收门限电平为:

式中,-174是宇宙背影辐射噪声功率谱密度,绝对温度T0=300 K时的环境噪声;R为信息速率,单位为“bps”;NF为接收机的噪声系数,取值为3;Eb/N0是误码率为1×10-6时,理想归一化信噪比,取值为10.6。

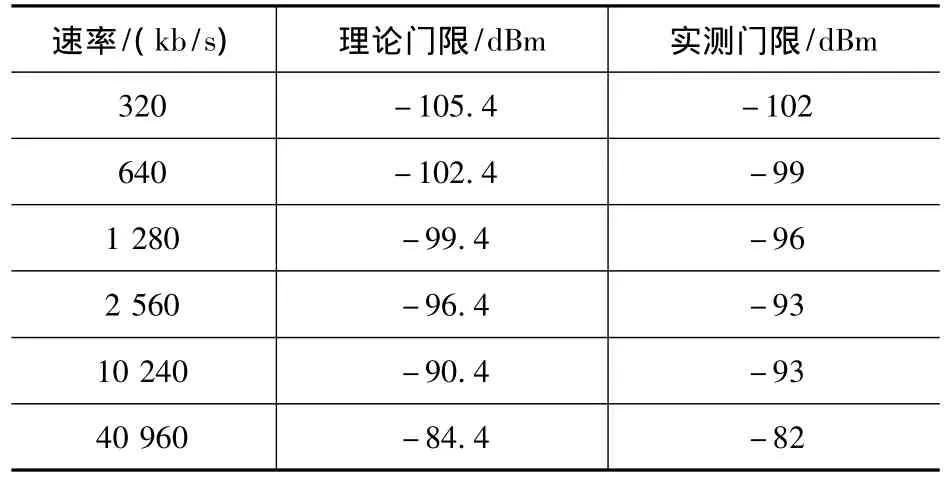

在高斯白噪声信道下,对微波系统接收门限进行了测试,与由式(1)得到各信息速率接收门限电平的理论值对比,结果如表2所示。

表2 接收门限测试

由表2可知,当系统信息速率为10240 kb/s时,卷积编码带来的编码增益使实测接收门限优于理论接收门限2.6 dB,其他速率实测接收门限与理论接收门限相比,性能损失也在3.4 dB以内。考虑到差分译码引起的误码扩散、解调损失、信道的非线性失真、环境温度变化以及调制矢量偏差等因素引起的接收门限恶化,测试结果表明使用本调制解调器的微波通信系统在降低了硬件成本的同时能够满足系统的整体性能。

5 结束语

现代通信系统中,多速率传输应用日益普及,其实现方案也多种多样。针对工程实际提出了一种多速率调制解调器实现方法,设计的实现基于直接序列扩频和卷积编码,分析了发端PN序列和卷积码的特性,并给出了收端如何恢复出信息码流的方法。直接序列扩频的应用场景还有很多,如码分多址等,卷积编码的性能随着约束长度的变化以及译码算法的不同也有提升的空间。多速率调制解调器已应用于工程实际,工作稳定可靠。本设计在实现多速率通信的同时,显著降低了系统的设备复杂度,保证了性能的实现,具有相当大的实用价值。

[1]杜慧敏.基于Verilog的FPGA设计基础[M].西安:西安电子科技大学出版社,2006.

[2]樊昌信,曹丽娜.通信原理(第6版)[M].北京:国防工业出版社,2009.

[3]斯克拉(Sklar B)(美).数字通信——基础与应用(第2版)[M].徐平平,译.北京:电子工业出版社,2002.

[4]韦惠民.扩频通信技术及应用[M].西安:西安电子科技大学出版社,2007.

[5]李雪华.CDMA通信中扩频解扩技术分析[J].无线电通信技术,2011,37(3):30 -32,64.

[6]何秀慧,马世平.基于QPSK调制的扩频通信系统FPGA实现[J].微计算机信息,2011,37(4):97-98,198.

[7]管吉兴.一种扩频接收机的设计分析[J].无线电通信技术,2012,38(5):58 -61.

[8]李勇,刘洋.一种新型数字化中频调制解调器设计[J].无线电工程,2010,40(5):27 -29,39.

[9]蔡晶烨,查光明,习友宝.基于软件无线电的 DS/DQPSK调制解调器[J].无线电通信技术,2008,33(3):55-57.

[10]田青峰,丁有志.基于CDMA网络的大容量移动短数据传输[J].无线电通信技术,2012,38(3):47-49.