毫米波二倍频器的研究与设计

张 倩,孙玲玲,文进才

(杭州电子科技大学射频电路与系统教育部重点实验室,浙江杭州310018)

(Key Lab.of RF Circuit and System,Ministry of Education,Hangzhou Dianzi University,Hangzhou Zhejiang 310018,China)

0 引言

毫米波倍频器是毫米波系统中常用的部件,它是频率合成器和倍频链等毫米波设备的关键模块。近年来,倍频器也常被用在毫米波超外差接收机的本振源中。原则上,所有非线性器件都能用于倍频器的实现,但实际上常用二极管和有源三端器件实现倍频。与二极管倍频器相比,有源倍频器的显著优点是:在工作频带内电路稳定、直流功耗小、变频损耗低或者可实现变频增益、并且对输入信号要求较低。随着工艺水平和器件模型的持续发展,国内外对倍频器的研究主要集中在毫米波亚毫米波频段。一些文献已经报道了基于硅CMOS工艺的倍频器,其直流功率损耗低但输出功率低、变频损耗大[1-3]。为了获得高输出功率、低转换损耗和面积紧凑的二倍频器,本文设计了一款基于GaAs FET器件的单端二倍频器。

1 倍频原理

对于任何非线性器件,当用正弦信号激励时,其输出端便会在谐波频率上产生功率。倍频电路的主要功能便是获得所需谐波的输出功率,同时滤除基波和其他无用谐波。

对于FET管,其非线性作用主要有饱和或截止两种状态。研究表明,利用漏极电流Ids的限幅作用可以实现较高的倍频增益。当FET管工作在饱和状态时,利用Ids-Vds曲线的非线性实现倍频,需要很大的漏极直流电流,所以转换效率很低,同时栅极电流存在的尖峰会损坏FET管,故而,实际应用中GaAs FET管毫米波倍频器大多采用工作在截止状态的模式。漏极电流是一脉冲型的,可以近似为一个整流之后的余弦,由傅氏级数来展开,可以得到漏极电流的表达式如下:

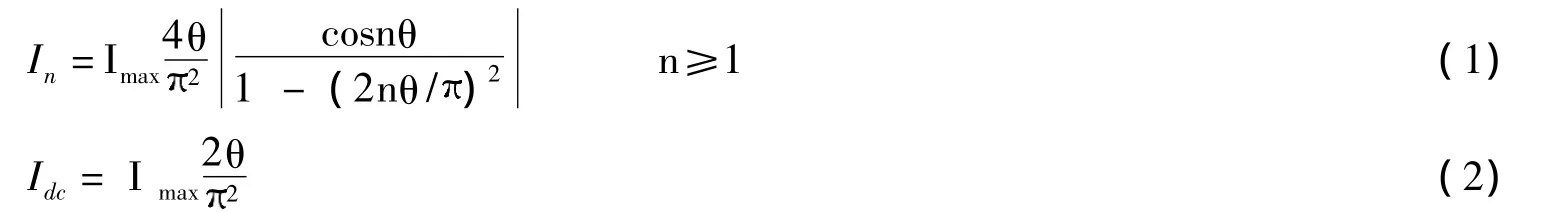

式1、2中,In是漏极电流的n次谐波,Idc是漏极电流的平均值,Imax是漏极电流的最大值,2θ是导通角。图1表示出漏极电流各次谐波与导通角之间的函数关系,为了使所需的谐波获得最大输出功率,Imax应该尽量大,选择合适的导通角获得较大的In。对于二倍频器,希望得到漏极电流二次谐波的最大值。根据图1所示,最优导通角约为0.35×360o=126o,相应的In/Imax=0.27,以此便可以确定最优栅极偏置电压。直流偏置栅极电压和漏极电压分别取-0.65 V和1.2 V,这样可使FET管工作在截止状态,既获得良好非线性又同时保证了较低的直流功耗[4]。

图1 谐波漏极电流与导通角之间的函数关系

2 电路设计

二倍频器的电路原理图如图2所示,对直流损耗和二次谐波输出功率之间进行折中并最终确定管芯的尺寸。该单端二倍频器包括了非线性器件、匹配电路和偏置电路3个部分。若要在所需频率上实现最小变频损耗,偏置电路和匹配电路的设计尤为重要。直流偏置网络和匹配网络使用微带线完成。偏置电路的选择决定了输出频率中是否含有所需频率的谐波成分,而匹配电路决定了是否能在所需谐波上获得最大功率,并最大限度抑制无用谐波分量和实现良好的隔离。

图2 二倍频器的电路原理图

输入端偏置电路由L9、C5及R构成,而输出端偏置电路由L4、C4及R构成。为了尽量减小电源对射频信号的影响,偏置电压应该加在所传输频率的开路点上。图2中,直流偏置电路中的微带线L9长度为基波频率f0对应的四分之一波长,微带线L4的长度为二次谐波频率2f0对应的四分之一波长,进而保证了直流输入对主传输线上信号传输的影响降至最低。C5和C4是去耦电容,可以降低电源对GND的交流阻抗;去耦电容容值不能取得太大,过大则会影响电路的稳定性。

在输入端,由L8、L10、L11及C3构成输入匹配电路。输入匹配电路使激励源与FET管输入阻抗实现共轭匹配,以此对基波f0进行匹配和对二次谐波2f0进行反射。这样,可以保证激励功率中的基波有效的加到FET管输入端,并同时抑制其他无用谐波输入和返回激励源,这是实现二倍频器低变频损耗和高效率输出的重要保证。

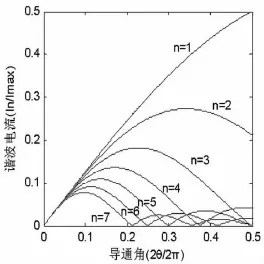

在输出端,由L1、C1、L3、L5及L2、C2构成输出匹配电路。输出匹配电路的设计原则是实现最大输出功率,这便要求对二次谐波2f0进行匹配并同时对基波f0进行反射。由于二倍频器的输出频率中包含较为丰富的频率分量,为了改善频谱质量,基波及其他无用谐波抑制是二倍频器的一个重要指标,因此滤波电路显得特别重要。在毫米波段倍频器中,广泛采用λ/4开路短截线抑制基波和其他无用谐波。但是,基波f0频率下的λ/4开路短截线太长。为了解决这个问题,采用微带线串联电容到地的结构实现滤波功能[5]。图3为λ/4开路短截线结构和微带线串联电容到地的结构,图4为两种结构性能的比较。通过选择适当的电容C2容值和微带线L2长度,在基波f0频率处出现传输零点。微带线L2(120 μm)约是基波f0频率下λ/4开路短截线长度的1/8倍。

图3 基波抑制电路

图4 基波抑制电路的性能比较

3 版图的设计

版图设计对任何一个芯片设计的性能能否实现非常关键。考虑到电路整体布局问题,使芯片面积得到最大化的应用,并尽量减小器件之间的串扰和耦合,最终得到的版图如图5所示。芯片面积为1.068 mm ×0.495 mm,芯片流片中。

图5 二倍频器版图

4 仿真结果

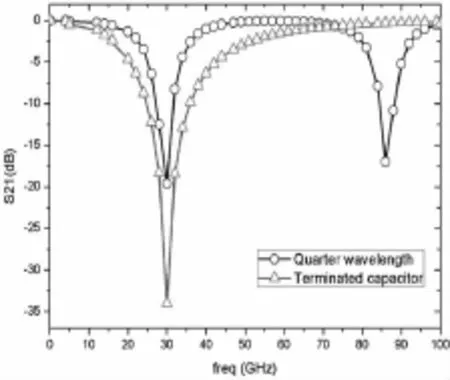

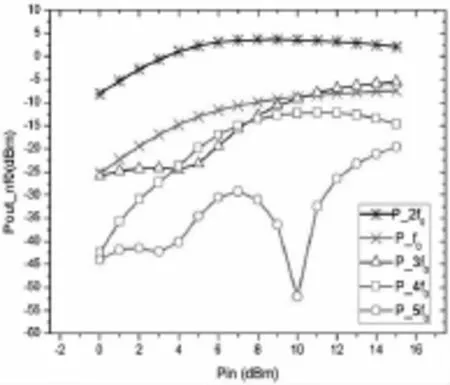

利用ADS中自带的电磁场仿真软件Momentum对无源结构,如微带线、电容、过孔和PAD等模型进行电磁仿真。整体电路采用Momentum和原理图进行联合仿真,整体电路的输出功率仿真结果如图6、7所示。从图6中可以看出,当输入频率f0在27 33 GHz范围内,且输入功率为5 dBm时,二倍频器的输出功率大于0 dBm;在输出频率60 GHz处,二倍频的输出功率达到2.256 dBm;变频增益大于-5 dB。从图7中可以看出,输入基波(30 GHz)功率为7 dBm时,输出二倍频(60 GHz)的信号功率可以达到3.459 dBm,基波抑制和三次谐波3f0均大于15 dB;四次谐波4f0和五次谐波5f0都获得了良好的抑制。

图6 输出功率随输入频率f0的变化

图7 输出功率随输入功率Pin的变化

5 结束语

本文基于GaAs工艺,设计了一个输出频率为54 66 GHz的有源单端二倍频器。本二倍频器联合仿真后获得较好性能:当工作频率在27 33 GHz范围内时,其输出功率大于0 dBm,变频损耗小于5 dB,基波抑制大于15 dB。

[1]Mattias Femdahl,Bahar M.Motlagh,Herbert Zirath.40 and 60GHz Frequency Doublers in 90-nm CMOS[J].IEEE MTT-S International,Microwave Symposium Digest,2004,(1):179 -182.

[2]Chen Jixin,Yan Pinpin,Hong Wei.A 50 - 70GHz Frequency Doubler in 90nm CMOS[C].Nanjing:Microwave Workshop Series on Millimeter Wave Wireless Technology and Applications,2012:1 -3.

[3]Mikko Kantanen,Jan Holmberg,Timo Karttaavi,etal.60 GHz Frequency Conversion 90 nm CMOS Circuits[C].Amsterdam:European Microwave Integrated Circuit Conference,2008:60 -63.

[4]David M,Klymyshyn,Zhen Ma.Active Frequency-Multiplier Design Using CAD[J].IEEE Transactions Microwave Theory and Techniques,2003:51(4):1 377 -1 385.

[5]Masaharu Ito,Shuya Kishimoto,Takao Morimoto,etal.Highly Integrated 60 GHz-band x12 Multiplier MMIC[C].San Francisco:Microwave Symposium Digest,2006:1 697 -1 700.