一种相位可调的低频信号源设计

陈国童,廖建庆 (宁德师范学院物理与电气工程系,福建 宁德 352100)

可编程逻辑器件具有器件规模大、工作速度快、可编程的硬件特点,同时它的开发可借助EDA的支持,这使得它适合用来实现DDS技术[1-2]。因此,以单片机+CPLD (复杂可编程逻辑器件)为硬件载体可实现DDS直接数字频率合成技术。下面,笔者进行基于单片机+CPLD相位可调的低频信号源设计。利用单片机软件控制的灵活性,用单片机STC89C52实现信号的控制部分。利用CPLD硬件上的高速、高集成度和可编程性,由CPLD (EPM7128S)和EPROM (2716)、D/A (DAC0832)构成信号产生部分,最后,用汇编语言和VHDL硬件描述语言分别对其编程。

1 系统组成及原理

图1 系统原理框图

系统主要由如下模块组成:MCU系统模块;CPLD系统模块;波形查表模块;幅度调节模块;D/A波形产生模块;低通滤波模块;相位差检测模块;7279键盘显示模块。系统原理框图如图1所示。

MCU信号控制部分主要通过7279键盘显示模块获取数值实现输出信号的频率、相位差和幅度的设置,并通过7279键盘显示模块实现输出信号的频率、相位和幅度的显示,还实现计算频率控制字、相位差控制字和幅度控制字,并向CPLD提供频率控制字、相位控制字和向幅度调节模块提供幅度控制字,幅度调节模块把输入的单片机产生的幅度控制字转换成D/A波形产生模块输出波形的参考电压,从而控制输出信号的幅度;DDS信号产生部分主要用来实现DDS技术,产生2路同频正弦波信号。

为了检测系统产生信号相位差效果,系统还设计了信号相位差检测部分。系统首先把2路正弦波信号转换为脉冲信号送至单片机的INT0、INT1,通过产生中断开始定时器T1计时和停止定时器T1计时,算出信号之间的时间差和周期,从而计算出两同频信号的相位差。

2 系统硬件设计

系统硬件电路设计包括CPLD电路、波形查表电路、D/A波形产生电路、幅度调节电路、低通滤波电路、相位差检测电路、7279键盘显示电路等电路设计。

2.1 CPLD电路

设计中选用EPM7128SLC84-15型号的CPLD为芯片,其属于Altera公司推出的MAX7000S系列。该芯片采用CMOS E2PROM工艺,传输延迟仅为5ns,内部具有丰富的资源,包括128个触发器、2500个用户可编程门;具有68个用户可编程的IO口,为系统定义输入、输出和双向口提供了极大的方便;通过配置,输入引脚可以兼容3.3V/5V逻辑电平,输出可以配置为3.3V/5V逻辑电平输出。EPM7128同时还提供了JTAG接口,可进行ISP编程,极大地方便了用户[3-6]。

设计中,CPLD电路实现DDS技术,生成2路11位的地址扫描信号,主要由EPM7128SLC84-15及相应的无源时钟振荡电路和JTAG接口下载电路组成。

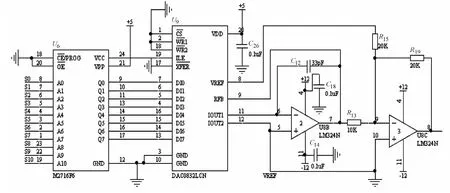

2.2 波形查找电路和D/A波形产生电路

首先要解决正弦信号在一个周期内的采样问题,采样值的个数根据相位差要求 (相位差范围为0~359°,相位差步进为0.2°),而该设计考虑到实现更高的移相精度,拟采用2048个采样点,且波形查找表设计为8位数字量输出。这样便可以确定正弦查找表为2048×8位结构,存储了正弦波在一个周期内波形的2048个采样点。由此相位差分辨率实际可达到360°÷2048=0.1757°。可以通过C语言编程来获得正弦查找表的采样值,并将8bit的采样值分别存放在2块8bit的2716存储器中。另外,对于D/A转换器的选择,首先要考虑到D/A转换器的转换速率,然后根据D/A转换器字长所带来的误差,决定D/A的位数。由此选择D/A转换器的型号为美国数据公司的8位高速数/模转换器DAC0832,片内带数据锁存器,输出电流稳定时为1μs,功耗为20mW。波形查找和D/A波形产生电路图如图2所示。

图2 波形查找和D/A波形产生电路图

2.3 幅度调节电路

为了可以调节输出信号的幅度大小,选用DAC0832(2个电流输出端Iout1和Iout2)构成幅度调节电路,其原理是通过控制DAC0832的VREF来控制输出信号的幅度。幅度调节电路如图3所示。

在图3中,Iout1为输入数字全为 “1”时,输出电流最大,约为255VREF/256RFB。当输入数字全为 “0”时,输出电流为0。输出端V0=-Iout1×RFB,当输入数字全为 “1”时,V0=-255VREF/256。

图3 幅度调节电路图

通过单片机发出的数字量 (用X表示)不同,来控制调幅的DAC0832的Iout1。其输出端V0=-X·VREF/256=-X·5/256(该0832的VREF固定为5V),从而使DAC0832的输出端V0作为后2块D/A转换器的DAC0832的VREF,即通过VREF的大小可以控制后2块DAC0832输出端V0的大小,由此实现幅度调节的功能。

2.4 相位检测电路

相位检测可以用来检测2路输入正弦波的相位差。该电路由同相放大电路和迟滞比较器和一个反向器组成。相位检测电路图如图4所示。

同相放大电路具有使输入信号放大的功能,其由运放LF353P构成。该同相放大电路的放大倍数Au=1+R31/R11=1+100/10=11。迟滞比较器是一个具有迟滞回环传输特性的比较器,在反相输入门限电压比较器的基础上引入了正反馈网络,由此构成了具有双门限的反相输入迟滞比较器。由于正反馈作用,这种比较器的门限电压是随输出电压Vom改变的。该迟滞比较器由LM393N构成。Vom是经迟滞比较器输出后的电压,V1是经同相放大电路输出后的电压,Vb是经R17输出后那点的电压,由于Vb的比较电压为0,所以,Vb=V1-(V1-Vom)/(R17+R21)×R17=0,得到V1-(V1-Vom)/11=0,即(10V1+Vom)/11=0,10V1+Vom=0,从而当Vom=-5V时,V1=0.5V,即V+i=0.5V;当Vom=+5V时,V1=-0.5V,即V-i=-0.5V。该反向器采用的是高速的HD74HC14反向器,由于输入信号变化较快,低速的反向器不能满足要求。

图4 相位检测电路图

3 系统软件设计

系统软件设计通过汇编语言和VHDL硬件描述语言来编写程序,完成信号的产生和控制设计。采用Altera公司的可编程逻辑器件和器件的软件开发平台MAX+plusⅡ进行VHDL编程。汇编语言则主要完成单片机对信号的控制功能的编制。

3.1 软件结构设计

为了使系统软件设计条理清楚,方便调试和使用,依照系统功能模块规划进行相应设计。软件则由2个不同的工具来编程。系统模块框图如图5所示。

MCU信号控制模块通过人机对话 (HD7279键盘显示模块)生成频率控制字、相位差控制字送CPLD信号产生模块、生成幅度控制字送DAC0832控幅模块,并显示相关频率、相位差、幅度值。相位差检测模块检测CPLD信号产生模块生成的2路信号的相位差。CPLD信号产生模块接收MCU发送的频率控制字和相位差控制字并通过寄存器拓展到相应位数。24位相位加法器生成信号地址并通过寄存器压缩为11位地址送2716波形存储器;相位加法器在Address1的基础上加上相位差控制字生成的地址增量,生成了第二路波形的扫描地址Address2并送2716波形存储器。

图5 软件结构设计框图

3.2 主程序设计

主程序的功能包括对系统的初始化及提供对键盘的扫描和信号频率、相位差、幅度及信号检测相位差值的显示等功能。主程序流程如图6所示。

当上电或复位时进入主程序,首先进行MCU的初始化:堆栈栈顶的设置;定时器T0、T1和中断INT0、INT1的初始化,接着是8s定时器的复位清零和显缓区、恢复数据暂存区的初始化及相关的标志位,然后调用显示程序将所有的参数 (频率、相位差、幅度)显示出来,同时发送相应控制字到CPLD信号产生模块和DAC0832信号幅度控制模块。当MCU初始化后,在主程序中做一闭路的循环。循环开始设置堆栈栈顶,防止程序跑飞堆栈地址混乱;之后调用键盘处理子程序SUB_KEY,使键盘始终处于查询状态。若有键按下则做相应处理,无键按下则返回到循环开始处。

图6 主程序流程图

4 结 语

设计了一种相位、频率、幅度都可调的2路波形输出的低频信号源,采用单片机和CPLD来设计信号源的控制部分,一方面能利用单片机软件控制的灵活性,另一方面又能利用CPLD硬件上的高速、高集成度和可编程性。使用上述方法可以充分利用软件支持方便地实现对信号参数的控制和修改,同时又能保证信号产生的高速和灵活可控,使系统能够满足设计要求的精度。

[1]张迎新.单片微型计算机原理、应用及接口技术 [M].北京:国防工业出版社,2004.

[2]廖日坤 .CPLD/FPGA嵌入式应用开发技术白金手册 [M].北京:中国电力出版社,2005.

[3]刘雁飞,赫建国,郑燕 .一种基于DDS技术的信号源及其CPLD实现 [J].西安邮电学院学报,2005,10(1):49-52.

[4]李小波,孙志勇,刘春生 .基于CPLD和单片机的低频信号源设计 [J].仪表技术与传感器,2005,15(11):46-48.

[5]王庆,刘涤尘 .基于CPLD的高精度可程控多路信号源 [J].仪表技术与传感器,2005,15(3):36-38.

[6]王永涛,韩建,牟海维,等 .基于单片机与AD9852的信号源设计 [J].电测与仪表,2006,43(7):39-41.