基于VHDL的FPGA新实验开发——简易处理器实现

陆玲霞, 姚 维, 高 健

(浙江大学电气工程学院,浙江杭州310027)

0 引言

EDA技术经过20多年的发展,由于其高速度、高可靠性、高集成度等优点已被广泛应用到医疗卫生、军事航天、科学计算等领域。为适应EDA技术的发展规律,培养该领域的系统级优秀人才,国内外高校纷纷开设基于FPGA的相关课程和实验。然而FPGA课程实践性强、设计性要求高,在FPGA教学过程中,实验课程占据很大的比例是非常重要的,因此如何激发学生的实验兴趣及探索实验有效途径是首要任务[1-2]。

为充分给予学生实践机会,本文通过引入暑期短学期集中培训的方式,尽量压缩理论课堂教学时间,充分给予学生实验室动手实践机会;同时结合实验项目给定的方式开展实验课堂教学,并通过结果和过程两者相结合的评定机制提升学生的学习积极性。值得特别提出的是:掌握FPGA技术的关键是使学生能自主完成较完整的系统设计,同时由于高性能CPU是国家技术实力的象征,设计国内自主产权的CPU意义重大,而且学生也已学过“微机原理和接口技术”课程,基于上述多方面原因,通过开设VHDL硬件描述语言实现简易处理器内核的综合性、创新性实验,帮助学生深刻理解微处理器内部结构和工作机理,更好地掌握FPGA的设计原理、步骤和方法,精通VHDL硬件描述语言的开发和实践,意义深远。

1 实验基本要素

Altera DE2-70实验/开发两用板是台湾友晶公司为高等院校学生学习FPGA编程和学习,基于Nios软核处理器应用项目编程而开发的实验平台。DE2-70多媒体开发平台的核心是Altera公司Cyclone II系列2C70型FPGA芯片,其拥有7万个逻辑单元,全称EP2C70F896C6,包括了丰富的资源,如存储芯片、音频、视频解码器、以太网接口、USB接口、串口等可靠的外设及多媒体特性,是一款具有强大数字信号处理功能和多媒体功能的开发板,可靠性较高[3-4]。

本实验就基于DE2-70采用VHDL硬件描述实现一个能执行如立即数赋值、寄存器赋值、寄存器加减法等简单指令功能的单片机系统[5-8]。

2 简易微处理器设计

2.1 处理器内部结构

图1为该处理器的内部结构,包含多个16位寄存器,多路选择器,加法器、减法器,计数器,和一个控制单元。数据采用16位标准输入,内部单元间传输数据通过16位总线,通过时钟来驱动输入控制信号和数据以完成微处理器的一系列指令动作。

考虑到开发板的硬件条件限制,在实际开发中,指令和立即数同时由外部输入信号Din给定,并通过不同的时钟步调实现指令和数据的读取和操作。

2.2 指令功能设计

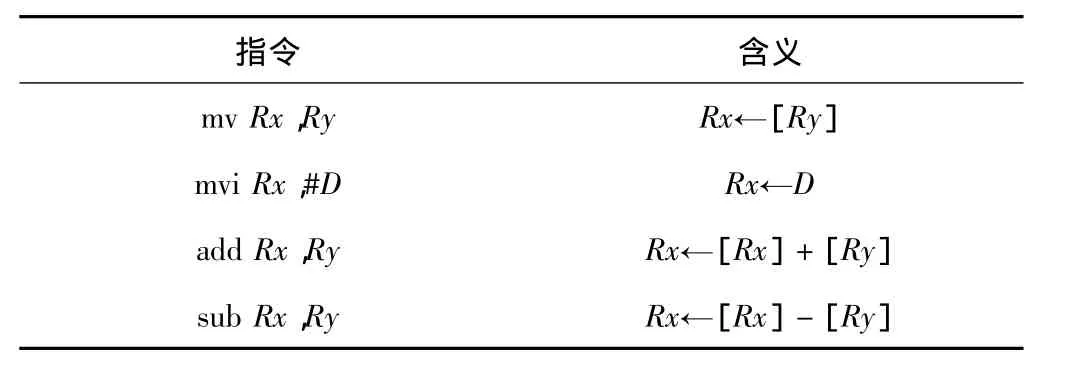

最终需实现的最基本的指令见表1。表1左栏定义了寄存器的指令名称和操作数,右栏中Rx←[Ry]是指寄存器Ry的内容赋值给Rx,Rx←D是指将立即数D赋值到Rx中,以此类推,完成经典的四个汇编指令功能,分别是寄存器之间赋值、向寄存器赋立即数、寄存器内容相加减。

每个指令译码成9位二进制数存入到IR寄存器中,格式如IIIXXXYYY,其中III代表指令,如mv、mvi等;XXX表示Rx寄存器;YYY表示Ry寄存器。该指令由16位DIN输入信号分离出9位二进制数得来,如图1所示。但对于mvi指令来讲,YYY没有任何意义,该操作数是立即数#D,由DIN输入完毕9位指令后待第二个时钟来临时所获得的16位数值。

图1 微处理器内部结构

表1 指令和功能介绍

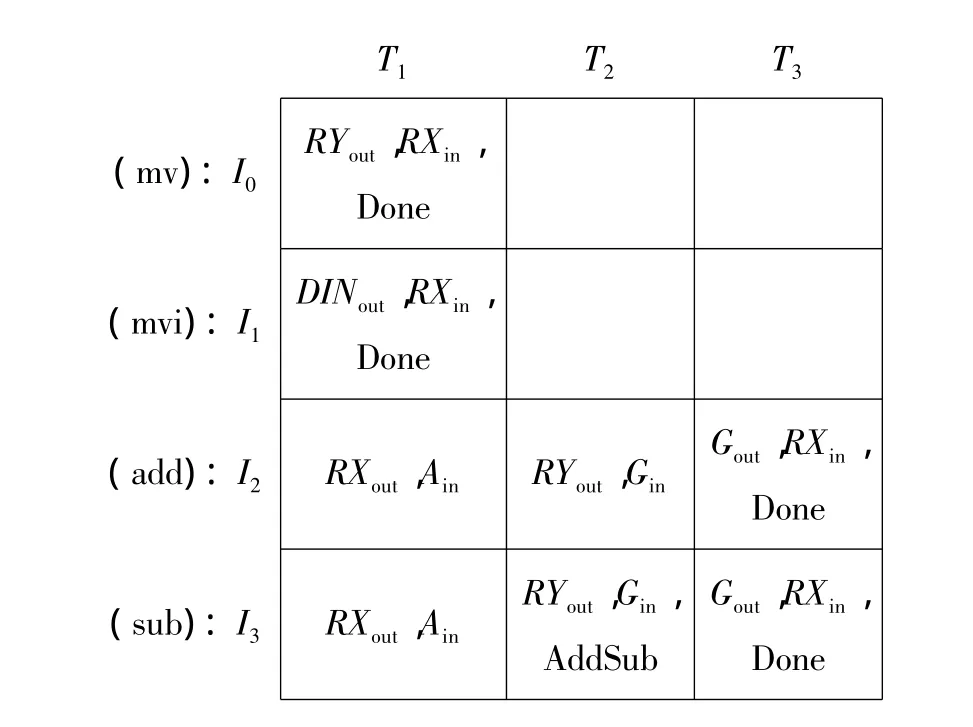

2.3 指令操作周期设计

Run信号高电平有效,控制指令的执行与否;一旦某一指令执行完毕,控制器将发出Done信号;而当reset信号来临,系统复位;指令周期分配由图1中couter模块提供,是一个二维量,不同指令需不同的处理周期。由于都需要通过总线buswire才能传递数据,因此将mov和movi指令分配两个周期(T0和T1),add和sub分配4个周期(T0、T1、T2和 T3),其中 T0时刻完成共性的动作——指令的读取,控制IRin有效,其余控制信号与相应的指令周期请见图2。

参看图2中mvi指令:要完成立即数的读取,首先在T0时刻将IRin置为有效,从DIN信号中分离出有效地指令信息,然后等待T1时刻来临,再将IRin置为无效后使DINout、RXin、Done3个控制信号有效,即完成将外部的立即数信号通过总线传输到寄存器的过程,并给出指令完成信号Done提醒用户。

2.4 软件流程图

通过对图1内部结构的剖析,自然想到采用VHDL结构化的编程思路[9-10]。对应于图中各部件,编写各例化元件(component),主要包括 counter、addsub、multiplexer、IR、control等。其中最关键的是control模块,它包括向各寄存器提供输入控制信号,向多路选择器提供选通控制信号等。主要的设计流程图见图 3[11-15]。

图2 控制信号与周期匹配图

图3 软件流程图

3 处理器仿真图

图4说明了4个指令的执行过程,Clock时钟信号为上升沿有效,一个时钟周期也就是图2中的T为20 ns,因此完成加减法指令需要4个CLOCK周期,即80 ns。4个指令的顺序执行过程如下:

① MOVIR0,#0005H;10 ns~50 ns区间

R0←0005H 即此时R0=0005H

② MOV R1,R0;50 ns~90 ns区间

R1←R0 即此时R1=R0=0005H

③ ADD R0,R1;90 ns~170 ns区间

R0←[R0]+[R1]

即此时R0=0005H+0005H=000AH

④ SUB R0,R0;170~250区间

R0←[R0]-[R0]

即此时R0=0005H-0005H=0000H

该仿真图充分验证出设计结果的准确性和步调一致性。

图4 处理器仿真图

4 结语

通过实验,有利于学生系统地综合应用多路选择器、人机显示、计数器等各种模块,掌握用component编程思想,思路清晰,自上而下,并通过控制器的时序实现,帮助学生更清晰地明白汇编指令功能的实现原理,实现过程,改变以往学生只是了解单片机汇编语言指令使用方法的现状,提高学生的学习积极性,加深其对VHDL语言的理解,熟悉并掌握FPGA开发的基本过程,实验教学效果良好。

[1] 陈 林,陈 晴,邢思锐,等.基于FPCA的综合设计性实验项目设计[J].实验室科学,2012,15(4):83-86.

[2] 杨 光,冯 涛,秦永左.VHDL实验教学的研究与探索[J].中国校外教育(下旬刊),2008(8):82.

[3] Nakkar Mouna.VHDL project tutorial on Altera DE2 board[C]//ASEE Annual Conference and Exposition,2009.

[4] 黄雄华,周 娅,蒋韦贞.基于Altera DE2板的数字逻辑电路课程EDA实验内容的设计[J].实验室科学,2010,13(4):90-93.

[5] 范晓亮.基于FPGA的双核模型机CPU的设计与实现[D].沈阳:东北大学,2008.

[6] 邵天增.基于FPGA的计算机组成与结构实验系统的设计与实现[D].上海:华东师范大学,2010.

[7] 刘 星.基于FPGA的8位模型机的设计与实现[D].天津:天津工业大学,2011.

[8] 邓惠娟.8086单芯片计算机VGA控制器的研究与设计[D].合肥:合肥工业大学,2010.

[9] 毛 敏.基于VHDL的一个简单Mealy状态机[J].现代电子技术,2009,32(14):4-6.

[10] 刘 君,常 明,秦 娟,等.基于硬件描述语言(VHDL)的数字时钟设计[J].天津理工大学学报,2007,23(4):40-42.

[11] Charles H,Roth Jr,Lizy K John.数字系统设计与 VHDL(英文版)[M].北京:电子工业出版社,2010:340-349.

[12] Ortiz M,Quiles F,Hormigo J.Efficient Implementation of Carry-Save Adders in FPGAs[C]//Proceeding of20th IEEE Conference on Application-Specific Syatem,Architecture and Processors(ASAP 2009).Boston.2009:207-210.

[13] 罗力凡,常春藤.基于VHDL的FPGA开发快速入门技巧实例[M].北京:人民邮电出版社,2009:21-84.

[14] 赵艳华,曹丙霞,张 睿.基于Quartus II的FPGA/CPLD设计与应用[M].北京:电子工业出版社,2009:162-171.

[15] 陈欣波.Altera FPGA工程师成长手册[M].北京:清华大学出版社,2012:120-150.