基于FPGA的DDS设计与实现

佟景泉,刘 悦,邢东峰

(兰州交通大学 光电技术与智能控制实验室,兰州 730070)

随着科技的进步和电子技术的发展,信号源应用越来越广泛,对其各方面的要求越来越高。传统的信号发生器在实际中已经不能满足需求。直接数字频率合成技术(DDS)具有频率分辨率高、频率变换速度快、相位可连续变化等特点,现在已广泛应用于信号发生器、通信及雷达系统等。

1 DDS的设计原理

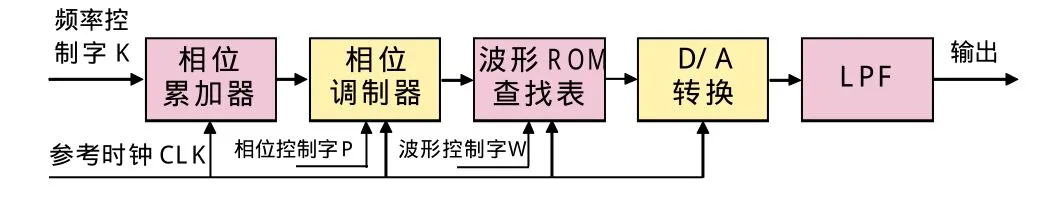

DDS是从相位概念出发,直接合成所需波形的一种频率合成技术,可以合成正弦波、矩形波以及三角波,而且还可以控制波形的初始相位。DDS主要由参考时钟、相位累加器、相位调制器、波形查找表、D/A转换器以及低通滤波器(LPF)组成。DDS的原理如图1。

图1 DDS的原理图

其中K为频率控制字,P为相位控制字,W为波形控制字。设参考时钟频率为fc,相位累加器的字长为N,相位调制器的字长、波形ROM查找表以及D/A转换器的字长为M,N位相位累加器在参考时钟CLK作用下,频率控制字K累加,溢出后截断高M位与相位控制字P相累加,累加结果作为波形ROM查找表的输入地址,对波形进行寻址。ROM的输出幅度码经过D/A转换成阶梯形波形,在经过低通滤波器(LPF)平滑得到合成的波形。得到的波形取决于ROM中存储的幅度码。

频率控制字K也称作相位的增量,设fc为参考时钟的频率, fo为输出波形的频率,相位累加器的精度为N,DDS的方程为:fo=fcK/2N。由奈奎斯特采样定理可以知道,最大输出频率在当K=2N-1时,fo=fc/2。当N→∞,输出频率fo越来越细。要改变DDS的输出频率fo,只需改变的是K的取值。

如:假设参考时钟fc=50 MHz,32位的相位累加器,频率控制字K=0X10000000,那么fo=50×228/232=3.125 MHz。当然可以利用PLL倍频或者分频,合成所需频率。

2 DDS各模块实现

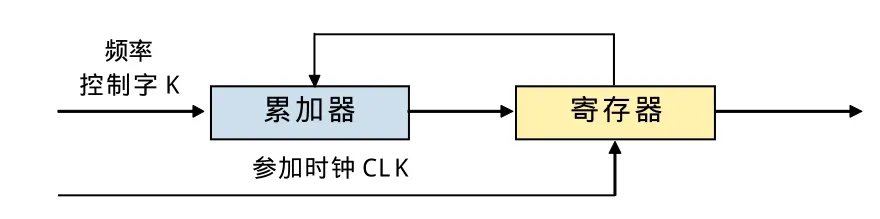

2.1 相位累加器

相位累加器是直接数字频率合成器的重要组成部分,用于实现相位的累加并存储其累加结果。N位的相位累加器由N位累加器和N位寄存器构成,实现相位的累加并存储累加的结果,每来1个参考信号CLK,由频率控制字K与寄存器存储的结果相累加,然后再送给寄存器。寄存器不断的把累加的结果送回累加器,然后在下1个时钟CLK到来时,和频率控制字K相加,当相位累加器加满时便产生1次溢出,完成1次周期性动作。

图2 相位累加器

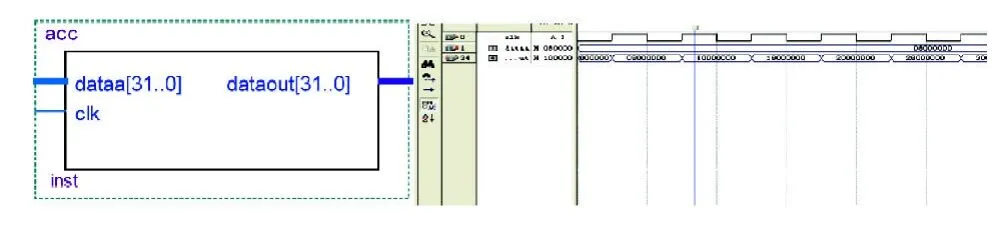

本设计中的相位累加器字长为32位,由4个8位相位累加器组成,利用Quartus II编译Verilog HDL编写的相位累加器,生成功能模块以及仿真波形如图3:

图3 相位累加器的功能模块与仿真波形

2.2 波形存储器ROM

波形存储器ROM中存储波形量化的数据,即每1个相位所对应的二进制数字正弦波幅值,在每个时钟来临时,相位累加器输出截取高M位作为ROM的输入地址,查询不同的地址所对应的幅度,实现相位和幅度的转换,这样就可以在给定时间上进行抽样,得到不同的相位所对应的二进制幅值序列,完成波形产生功能。利用Quartus II上面自带的LPM ROM,然后把.mif文件加载到ROM中,以实现所需的功能。对于ROM的设计主要有2种方法:(1)设计一个ROM,把波形的量化数据顺序或间隔的存放进去;(2)设计3个ROM分别存储正弦波、矩形波、三角波的量化数据。.mif文件可以借助matlab生成。但这样在设计过程中使ROM的开销特别大,造成资源浪费,可以从利用分象限的角度来考虑,如:正弦波形分成4个部分(00~900)、(900~1800)、(1800~2700)和(2700~3600),ROM中只需存储(00~900)的波形,利用正弦波形的对称性,就可以计算出(00~3600)内的波形,从而节约开销。最高位代表符号位,如果为“1”则进行取补。高2位表示角度所在的象限:“00”表示第1象限,正弦值不变;“01”表示第2象限,正弦值取补;“10”表示第3象限,正弦值取补;“11”表示第4象限,正弦值不变。

2.3 D/A转换器

D/A转换器(DAC)的作用是用来将数字信号转换成模拟信号。DDS系统中,波形的幅度值量化后被存于ROM中,然后通过数据线转输出代表二进制数的电平信号,DAC作用就是将电平数字信号转换成模拟信号。为了得到准确的数据,DAC必须有足够的精度,同时保证在较高频率下,有很好的转换速度,但是由于DDS分辨率的限制,输出的信号并不能真正实现连续可变,故其输出波形只为阶梯型,需要通过低通滤波器滤去高分频部分,平滑后得到模拟的波形,一般情况下,DAC作为DDS的外部模块,提高了DAC设计的方便性。

2.4 低通滤波器

滤波器就是用来改变信号中各个频率分量的相对大小,或者抑制,甚至全部滤除某些频率分量。选择性滤波是让1个或者1组频率范围内的信号无失真通过,而衰减或完全抑制其余频率范围的信号,实现这种功能的系统称为选择性滤波器。低通滤波器(LPF)用于衰减和滤除不需要的取样分量以便输出频率纯净的波形信号。从D/A转换器输出波形是阶梯型波形,含有大量的高分频谐波,经过1个低通滤波器(LPF),无失真的通过所有频率分量,低通带之外的所有频率都被完全抑制,输出的为正弦波形。

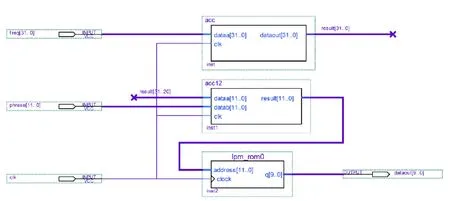

2.5 核心模块设计

从系统的总体要求出发,用自上而下的设计方法,逐步设计各模块,最终完成基于硬件的设计。DDS的核心模块如图4。

在此设计中,设计出32位的相位累加器,12位相位调制器,然后12位输出作为ROM的输入地址。

3 仿真验证

将DDS模块仿真后的工程下载到Altera的FPGA中进行验证,可以观察生成的波形仿真图如图5。

图4 DDS核心模块

图5 DDS的仿真正弦波、方波和三角波波形仿真图

4 结束语

基于FPGA设计的DDS信号源,具有频率分辨率高、切换速度快、相位噪声低等优点,广泛应用于现代雷达系统、通信系统和电子对抗系统中。随着DDS频率的上升,DAC对DDS输出影响也越来越大,对于由于截断相位累加器引起杂散以及对ROM的开销很大等都是DDS中有待改进的地方。

[1]王金明. 数字系统设计与Verilog HDL[M]. 北京:电子工业出版社,2009.

[2]夏宇闻.Verilog数字系统设计教程[M]. 北京:北京航空航天大学出版社,2008.

[3]李海江,刘 方. 基于Verilog HDL的DDS任意波形发生器设计[J]. 仪器仪表用户,2009(4):55-57.

[4]李春剑,吉望西,刘达伦. 基于Verilog HDL的DDS设计与仿真[J]. 现代电子技术,2008(20):15-17.