CSNS/RCS高频低电平远程控制系统样机

王 林 雷 革 马 力

(中国科学院高能物理研究所 北京 100049)

中国散裂中子源(CSNS)快循环同步加速器(RCS)高频低电平系统的任务是保证高频系统严格按照电压、相位、频率的优化工作曲线运行,同时还要克服束流负载效应造成的系统不稳定性问题。它要完成腔压幅度控制、同步相位控制和自动调谐等功能[1]。

高频低电平远控系统负责将低电平系统接入到EPICS控制系统框架中,使其与中央控制上位机进行实时数据通信。

1 总体结构

1.1 软硬件结构

EPICS(Experimental Physics and Industrial Control System)是开源的实验物理和工业控制系统软件包,已在世界范围内广泛应用于粒子加速器、天文望远镜等科学装置。它提供了丰富的控制系统软件开发工具,可以用来建立分布式的控制系统体系结构,进行系统集成。

EPICS 由操作员接口 OPI(Operator Interface),输入输出控制器IOC(Input/Output Controller)和局域网LAN(Local Area Network)三部分组成[2]。

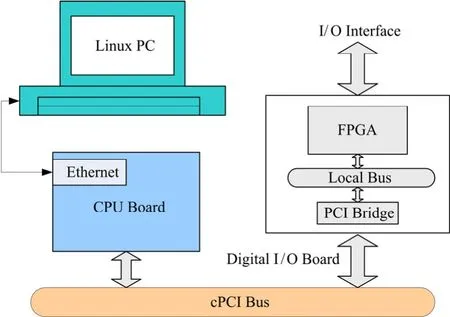

高频低电平远控系统采用全数字控制模式,CPU板+cPCI总线+数字I/O板的架构[1],CPU板和数字I/O板放在同一个cPCI机箱内,CPU板通过cPCI总线控制数字 I/O板和网络与上位机进行通信。CPU板是爱默生的 CPCI-6020,操作系统是vxWorks。高频低电平远控系统结构如图1所示。

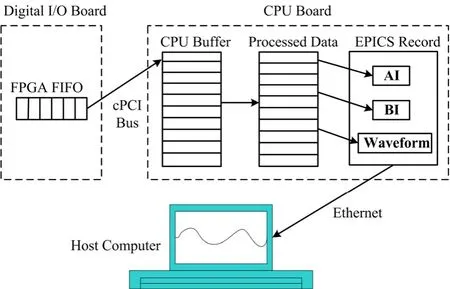

RCS高频系统有8个高频腔,相应有8块数字I/O板,每块板卡控制一个腔。因此,在一个总线机箱内,一个CPU板需要控制8块数字I/O板。其结构如图2所示。

图1 高频低电平远控系统结构图Fig.1 Architecture of LLRF remote control system.

图2 CPU板与数字I/O板的对应关系图Fig.2 Correspondence between CPU and digital I/O boards.

1.2 工作过程

RCS的重复周期是40ms,高频系统在前20ms由数字I/O板采集与高频腔相关的实时数据,包括腔压、相位、频率等。后20ms,CPU板通过cPCI

中国散裂中子源工程建设资金资助

系统的时间分配是,留出2ms的余量,也就是用18ms的时间传输数据。由于有8块数字I/O板同时工作在一个cPCI机箱内,所以平均每块板卡需要在2.25ms内完成数据的传输。

数字I/O板中的FPGA固件程序的功能是以固定时间间隔产生中断,CPU板接收到中断后,利用DMA传输,读取 16K个整型数据(即64KB)。中断周期为 40ms产生 4次中断,与下一次中断的间隔分别为 4.5ms、 4.5ms、 4.5ms、 26.5ms。 16K个整型数据由 FPGA 内部 FIFO 产生,在产生中断之前准备好,为了方便对数据进行校验,这些数据是定值,分别是1,2,3,…,16384。

数据的传送过程如图 3所示。CPU板先通过DMA把FPGA中的数据取出来放到缓冲区中,原始数据需经过标度变换,然后送到EPICS的ai、bi和 waveform等记录中,再通过网络把数据送到上位机显示。

图3 数据传送过程Fig.3 Data transfer process.

2 软件开发

2.1 板卡配置

2.1.1 板卡识别

与VME等标准总线的板卡类似,在cPCI总线上,板卡首先要被识别。cPCI总线和PCI总线使用相同的软件接口,因此数字I/O板的识别方法与PCI设备相同,下面很多概念也将直接以PCI总线来描述。

PCI设备空间包括配置空间和地址空间,配置空间用于存储和配置设备的基本信息,地址空间用于访问设备的内部寄存器。当vxWorks操作系统启动时,逐个扫描PCI设备,并为设备分配总线号、设备号、功能号,程序中通过总线号、设备号、功能号来访问PCI设备的配置空间。然后,vxWorks为PCI设备分配基地址,并将其写入到配置空间的BAR(Base Address Register),程序中通过基地址来访问PCI设备的内部寄存器。

在数字I/O板中,PCI桥芯片PLX-9656与cPCI总线接口,并通过 Local Bus与 FPGA接口。PLX-9656和FPGA都需要PCI地址空间,这两个地址由 vxWorks系统分配以后自动存储在PLX-9656配置空间的BAR0和BAR2中。

2.1.2 板卡配置过程

首先,使用vxWorks函数pciFindDevice(),以PLX-9656的vendor(供应商)和device(设备)ID为参数[3],查找数字 I/O板,为识别出的每块板卡分配一个结构体,用于存储板卡基本信息,并通过链表连接起来,以便查找。然后,在PCI配置空间中读取总线号、设备号、功能号、基地址和中断向量等信息,开辟数据缓冲区、vxWorks信号量,分别将它们存储在板卡结构体中。最后,连接中断服务程序,启动中断服务任务[4],初始化 PLX-9656桥芯片。板卡配置过程如图4(a)所示。

2.2 中断服务程序(ISR)

2.2.1 PCI中断

PCI总线采用共享的中断方式,每个PCI设备有 4个中断引脚 INTA、INTB、INTC、INTD(通常只用INTA)[5]。CPCI-6020的中断控制器为PCI设备提供了4个中断请求线,分别编号为28、29、30、31。PCI设备配置空间中的中断线寄存器用于指示中断引脚与中断控制器的连接关系,对于CPCI-6020,即为28、29、30、31中的一个。

在程序中,用中断线的值作为中断向量来关联中断服务程序,于是,当中断发生时,中断服务程序就会被vxWorks执行。由于数字I/O板的数目多于4个,一个中断向量会对应两块数字I/O板,所以当中断产生时,需要查询PCI设备的中断标志位来判断到底是哪个设备产生的中断,产生的是哪个中断。

2.2.2 中断服务程序工作流程

每个数字I/O板有三种中断,即FPGA中断、DMA通道0中断和DMA通道1中断。FPGA中断表明数字I/O板中的数据己经准备好,DMA通道0和DMA通道1的中断表明本次DMA传输完成。DMA通道0用来将数字I/O板中的64KB数据传到CPU板,DMA通道1用来将CPU板中的波形数据传到数字I/O板中。

样机的中断服务程序查询每块板卡的PCI中断标志位,确定是哪块板卡产生的哪个中断。如果是FPGA中断,则发起一次DMA,从数字I/O板传输64KB数据到CPU板。如果是DMA通道0或DMA通道1中断,则释放信号量,触发中断服务任务进行数据读写和处理。中断服务程序流程如图4(b)所示。

2.3 中断服务任务

程序中有两个中断服务任务,任务1等待DMA通道0释放的信号量,然后进行字节序转换、数据校验和数据处理。数据准备好后,触发EPICS记录来读取数据。在这里,进行字节序转换是因为 PCI总线的数据使用小端模式(little-endian),而PowerPC处理器的数据使用大端模式(big-endian)。数据处理是按照高频低电平系统的需求,把 64KB数据分成8组,每组8KB,并对每组数据进行标度变换。中断服务任务1的流程如图4(c)所示。

任务2等待DMA通道1释放的信号量,输出运行信息,表明波形数据已经写入到数字I/O板中。

图4 主要函数流程图Fig.4 Flow chart of main functions.

2.4 DMA传输

为了提高数据传输带宽,使用 DMA(Direct Memory Access)方式进行数据传输。DMA控制器在PLX-9656桥芯片上,桥芯片一边连接cPCI总线,另一边连接板卡的内部总线(Local Bus)。发起一次DMA传输的过程是:在桥芯片的DMA控制寄存器中,先设置PCI地址、内部总线地址、传输的数据量、传输方向,然后使能DMA即可。DMA传输完成时,桥芯片向PCI总线发出中断,通知操作系统DMA传输完成。

2.5 EPICS接口

程序中,EPICS记录使用中断的扫描方式,当CPU板缓冲区中的数据准备好时,触发EPICS记录进行处理,从而EPICS记录将数据从缓冲区中读取到自己的value域。具体过程是,数字I/O板配置时,使用 EPICS函数 scanIoInit()初始化一个IOSCANPVT型的变量。然后在记录的设备支持函数的 get_ioint_info()中,将记录与相应的IOSCANPVT型变量进行捆绑。当缓冲区中的数据准备好时,使用EPICS函数scanIoRequest(),以这个变量为参数,即可触发相应的 EPICS记录进行处理。

样机的实时控制部分用到了EPICS的ai、bi、waveform等记录类型,使用EPICS base中自带的记录支持,然后单独开发了设备支持和设备驱动。bi用于读取板卡工作模式,bo用于设置板卡工作模式、发送“板卡开始工作”等控制信息;longin和longout分别用于读取和设置测试时FPGA的中断次数;ai和ao用于读取和设置标度变换的系数;8个waveform分别用于读取 8组 8KB的数据;1个waveform用于向数字I/O板写入波形数据,这个波形数据是电压、相位或频率的优化工作曲线,保证高频系统严格按照这个曲线运行。波形数据先用EPICS工具caput写入到waveform记录,再由记录的设备支持直接发起一次 DMA,传输到数字 I/O板中。

2.6 时间测试

CPCI-6020的CPU是MPC7410,这个CPU里面自带了时间计数器,以 25MHz的频率递增,时间精度是 40ns。可以使用 CPCI-6020 BSP中的sysTimeBaseLGet()函数获取时间计数器的当前值,将这个函数穿插在程序中,就可以计算出程序的执行时间。

表1列出了FPGA发出6个中断的时间测试。在一个重复周期,每个数字I/O板消耗的时间主要是DMA传输、字节序转换、数据校验和数据处理。在后续的应用中,字节序转换的时间可以通过FPGA中数据反写而省掉,而且也不再需要数据校验。DMA传输时间和数据处理时间的总和远远小于2.25ms,因此,数据传输和处理的时间满足高频低电平系统的要求。

表1 时间测式结果 (ms)Table 1 Time measurement (ms)

3 人机界面

人机界面使用EDM开发。如图5所示,上面四个X-Y Graph控件以曲线的形式分别显示8组数据,下面的文本框分别用于读取和设置8组数据标度变换的系数,右下角的 intNum文件框用于读取和设置 FPGA产生中断的次数。AutoStop和NeverStop显示当前板卡的工作模式。系统有两种工作模式:N 次停止模式(AutoStop)和连续工作模式(NeverStop)。AutoStop是用 intNum文本框来设置一定的中断次数,当FPGA已经发出了intNum次中断时,就停止工作;NeverStop是让系统持续工作下去,只有切换成AutoStop模式才能停止。系统处于AutoStop模式时,按钮显示NeverStop,系统处于NeverStop模式时,按钮显示AutoStop,点击按钮进行模式切换。Reset按钮用于重置8组数据标度变换的系数。Start按钮用于使能数字 I/O板的FIFO、时钟和中断,使数字I/O板开始工作。

图5 人机界面Fig.5 Operator interface.

4 结论

在EPICS和cPCI的软硬件架构下,作者通过中断服务和DMA传输,实现了将数字I/O板中的数据传到上位机显示,以及从上位机向数字I/O板发控制信息和波形数据的功能。通过传输固定数据的方式,对数据进行了校验,同时也对时间进行了测试,测试结果表明远控系统样机的功能和性能满足高频低电平系统的要求。

样机模拟了高频低电平远控系统的实际工作方式,这样为后面的带腔联调做好了铺垫。

1 中国散裂中子源(CSNS)初步设计[R]. 中国科学院高能物理研究所, 2011 Preliminary design of the China Spallation Neutron Source (CSNS)[R]. Institute of High Energy Physics,CAS. 2011

2 Martin R. Kraimer, Janet Anderson, Andrew Johnson,EPICS Application Developer’s Guide, Release 3.14.10,2009, http://www.aps.anl.gov/epics/base/R3-14/10-docs/AppDevGuide.pdf [OL]

3 季宇. VxWorks 操作系统下CompactPCI总线驱动程序设计[J]. 电子设计工程, 2009, 17(6): 99–101 JI Yu. Design of the CompactPCI bus driver program under VxWorks[J]. Electronic Design Engineering, 2009,17(6): 99–101

4 程敬原. VxWorks软件开发项目实例完全解析[M]. 北京:中国电力出版社, 2005 CHENG Jingyuan. VxWorks software development project instance fully resolved [M]. Beijing: China Electric Power Press, 2005

5 PCISIG, PCI Local Bus Specification, Revision 2.2, 1998,http://www.ece.mtu.edu/faculty/btdavis/courses/mtu_ee31 73_f04/papers/PCI_22.pdf [OL]