基于FPGA的直接数字频率合成器设计

王元华

(齐鲁师范学院物理系,山东济南 250200)

直接数字频率合成或DDS(Direct Digital Frequeney Synthesis)技术是近年发展起来的一种新的频率合成技术[1]。它具有频率分辨率高、频率转换速度快、输出频率范围宽、相位变化连续、输出波形灵活和易于集成等优点[2]。随着FPGA/CPLD技术的发展,DDS系统完全可以用可编程逻辑器件来实现,这样不仅降低了成本,而且设计者可以按照自己的需要来设计系统的功能。

1 整体设计方案

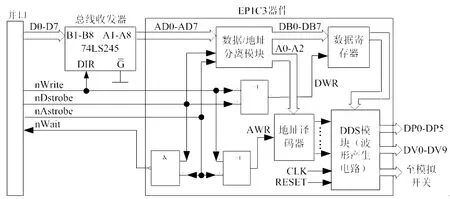

Cyclone系列FPGA是Altera公司推出的一款低成本、中等密度的现场可编程门阵列产品。它平衡了逻辑、存储器、锁相环和高级I/O接口,是对价格敏感应用时的最佳选择。本文采用Cyclone系列中的EP1C3T144C8芯片来设计DDS系统以及DDS系统与上位机的接口部分[3]。EP1C3的内部整体设计结构如图1所示。

图1 EP1C3的内部整体设计结构图

从整体上看,EP1C3实现的功能包括两部分:接口电路和波形产生电路(DDS模块)。其中接口电路部分包括数据/地址分离模块、地址译码器、逻辑控制模块和数据寄存器等。DDS模块主要实现的是相位累加器和波形存储器的功能。DDS模块主要是由相位累加器、波形存储器ROM、数/模转换器DAC和低通滤波器组成[4]。

2 接口电路的设计

接口电路的设计就是使用增强性并口(EPP)[5]所提供的 nWrite、nDstrobe 和 nAstrobe 控制信号线,进行一定的组合逻辑产生计算机所需要的应答信号nWait,以及按照系统设计的要求,组合出数据写信号 DWR和地址写信号 AWR。总线收发器74LS245的DIR信号线是由 nWrite来控制的,当nWrite为低电平时,74LS245的数据传输方向是从B到A的,此时进行EPP写操作。

由于EPP并口的地址线和数据线共用,所以利用nDstrobe和nAstrobe作为片选信号来分离地址和数据信号。并且使用 nWrite和 nDstrobe、nAstrobe分别进行“或”运算产生数据写 DWR和地址写AWR信号,以此来控制数据寄存器和地址译码器的工作。地址译码器采用3-8译码器,它的输入地址信号是数据/地址线经过数据/地址分离模块后得到的。数据/地址分离模块及地址译码器的功能仿真结果如图2所示。

图2 数据/地址分离模块及地址译码器的功能仿真图

3 DDS模块的设计

3.1 相位累加器的设计

相位累加器在时钟的作用下,对频率控制字进行累加,其输出作为ROM的寻址地址,然后进行相位-幅度转换得到离散的幅度数据,再经过DAC转换和滤波得到模拟信号。对频率控制字进行累加,其输出作为ROM的寻址地址,然后进行相位/幅度转换得到离散的幅度数据,再经过DAC转换和滤波得到模拟信号。

为了获得较高的频率分辨率,相位累加器的字长设计为32位,同时为了尽量减少由幅度量化误差引起的DDS杂散分量,本设计采用了分辨率为10位的DAC,即波形存储器的数据宽度是10位的。由于本设计使用的是8位数据传输,所以频率控制字必须分4次进行传输,波形数据必须分2次进行传输。

相位累加器由全加器和相位寄存器组成。全加器是相位累加器结构中的关键部分,为了提高相位累加器的工作速度,本文采用了4位超前进位加法器来设计全加器。

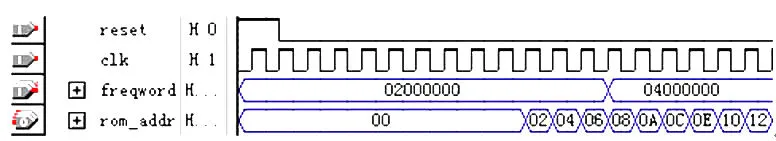

为了进一步提高相位累加器的工作速度,本设计采用流水线技术来设计相位累加器[6]。32位的相位累加器采用8级4位的流水线结构,其中每一级的加法器都采用4位超前进位加法器结构,寄存器采用带有异步复位的D触发器DFF来构成。由于采用了8级流水线,所以数据从输入到输出要经过8个4位D触发器才能得到运算结果,也就是说要经过8个时钟周期后才能得到累加结果。但由于在每个时钟中都有数据输入到各级流水线,各级同时进行累加,并将结果同时输出,因此从总体来看,完成一个32位的累加运算只需一个时钟周期,从而使得累加速度等于参考时钟频率。相位累加器的功能仿真图如图3所示。

图3 相位累加器的功能仿真图

由图可见,在输入与输出之间增加了8个寄存器,并且在高8位输出端又增加了一个8位的数据寄存器,所以在系统复位后,要经过9个时钟周期才有数据输出。并且当频率控制字进行切换时,输入数据需要保持9个时钟周期才能刷新频率控制字,这就降低了频率转换速率,这也是采用流水线设计相位累加器的缺点之一。

3.2 波形存储器的设计

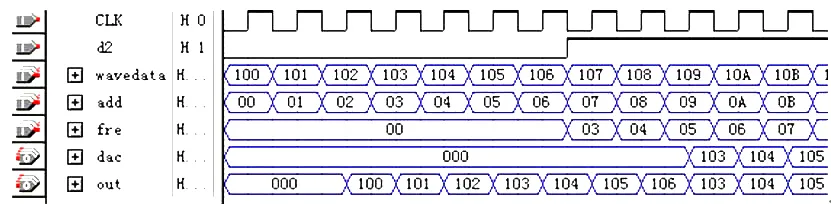

为了增加系统的灵活性,本设计采用EP1C3内嵌的RAM块来实现波形存储器的功能[7]。根据系统的需要,采用Quartus II软件提供的参数化RAM模块LPM_RAM_DQ,LPM_RAM_DQ的输入与输出端口分离,读写数据共用一个地址端口,并且由于LPM_RAM_DQ读写数据共用一个地址端口,所以需要增加一个2选1的地址选择器来选择LPM_RAM_DQ的地址来源。图4给出了波形存储器的电路原理图,其中 wavedata[9..0]是10位的波形数据,add[7..0]是地址信号,fre[31..24]是相位累加器输出的高8位。由于地址信号经过地址选择器时产生了一个时钟周期的延迟,因此为了保证波形数据写入正确的地址单元,将控制信号寄存器的D2位和波形数据 wavedata[9..0]用 D触发器也延迟一个时钟周期。同时为了保证系统的同步,所有的时钟信号与系统时钟相连。

图4 波形存储器的电路原理图

波形存储器的功能仿真图如图5所示,从图中可以看出,当wren为高电平(即D2为低电平)时,波形数据写入RAM,此时输出端一直为低电平,没有数据输出。只有wren为低电平时,输出端才有数据输出,并且由于波形数据从输入到输出需要经过三个时钟周期的延时,所以波形数据经过三个时钟周期后才能输出。

图5 波形存储器的功能仿真图

3.3 实验测试结果

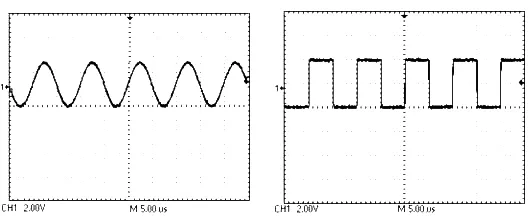

设计完成后,对设计的功能进行实验测量。图6给出了频率为100KHz,幅值为4V的正弦波、方波的输出波形,其中方波的占空比为50%(实验结果均由Tektronix公司的数字存储示波器TDS2012测量所得)。从图中可以看出,输出波形的频率和幅值准确度高,波形无明显失真。

当对不同频率的正弦波进行连续测量时,每次的测量值和预置值几乎相等,在此只取某次的测量值进行分析,测量数据及误差分析如表1所示。从表中可以看出,频率稳定度达到了10-5(即10ppm)数量级。

图6 频率为100KHz、幅值为4V的输出波形

表1 输出频率的数据分析

4 结语

本文介绍了利用FPGA器件设计DDS系统的设计思想、电路结构和改进优化方法,从实验结果可以看出,采用FPGA器件设计DDS系统是可行的。本设计尚存在一些问题,比如采用EPP并口进行数据传输,限制了波形频率的切换速度不会很高,在以后的研究工作中,可以考虑USB串行总线进行上位机和FPGA之间的数据通信。

[1] J.Tierney,C.M.Rader,and B.Gold.A Digital Frequency Synthesizer[J].IEEE Transactions on Audio and Electro acoustics,1971,19(1):48-57

[2] 罗柏明,张雷.一种有效的DDS相位截断杂散抑制方法[J].北京:电子技术应用,2008,34(11):97-99

[3] 王诚,吴继华.Altera FPGA/CPLD设计(基础篇)[M].北京:人民邮电出版社,2005

[4] 郑毅.一种高精度直接数字式频率源的设计[J].南京:电气电子教学学报,2003,25(4):45-47

[5] 谢庭军,刘少君,黄道平.EPP模式下的并口与FPGA的高速数据通信[J].沈阳:控制工程,2008,15(4):440-442

[6] G.W.Kent and N.H.Sheng,A High Purity,High Speed Direct Digital Synthesizer,IEEE International Frequency Control Symposium[J],1995:207-211

[7] 潘松,黄继业.EDA技术使用教程[M].北京:科技出版社,2005