基于FPGA乘法器的FIR滤波器系统设计

张婧霞,沈三民,翟成瑞

(中北大学仪器科学与动态测试教育部重点实验室,山西 太原 030051)

在通信系统、航空航天系统、雷达系统、遥感遥测系统等工程技术领域,无论是在信号的获取、传输,还是信号的处理和转换都离不开滤波技术。由于FIR滤波器具有严格的线性相位和在系统中具有稳定性,因此FIR滤波技术具有广泛的应用[1-4]。

随着微电子技术的发展,采用现场可编程门阵列FPGA进行数字信号处理得到了飞速发展。由于FPGA具有现场可编程的特点,具有高速传输和处理数字信号的能力,实现滤波算法速度高于传统的DSP的数字处理信号的能力,因此受到硬件电路设计工程师们的青睐[5]。传统的采用FPGA实现的FIR滤波器由于采用寄存器直接相乘模式占用了大量的乘法资源,因此在进行乘法运算时影响FPGA运行速度,并且由于资源上的限制导致FPGA其他功能受到限制。但基于FPGA乘法器的FIR滤波器具有节省FPGA 资源、提高运算速度、减少电路体积等优点[6-7]。

1 FIR低通滤波器整体设计

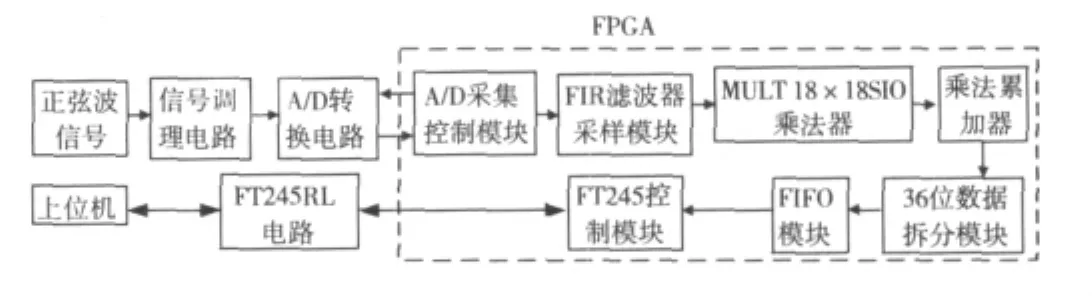

本文主要介绍的是FIR低通滤波器,该FIR低通滤波器主要由硬件电路和FPGA程序组成。FIR滤波器硬件电路主要由信号调理电路、AD转换电路、FPGA控制电路、FT245RL电路和上位机组成,其中FPGA内部程序模块包括AD采集控制模块、FIR滤波器采样模块、MULT 18×18SIO乘法器模块、累加模块、36位数据拆分模块、FIFO模块和FT245控制模块。该滤波器主要功能是利用信号发生器产生特定频率的正弦波,通过信号调理电路进行调理后经过12位的AD转换器进行转换输出数字信号,FIR滤波器采样模块工作在60 MHz的时钟内,并且以10 kHz的采样率对AD输出的数字信号进行采样,采样到的数字信号值连同FIR滤波系数输出到18位乘法器模块,经过乘法运算后进行累加,累加出来的是36位数据,最终通过FT245组成的USB接口传给上位机进行曲线显示,所得结果即为滤波后的数据,系统组成原理如图1所示。

图1 FIR低通滤波器整体设计框图

2 硬件电路设计

2.1 AD转换器电路

本系统中对于输入电压的采样率为10 kHz,因此采用了AD公司的高性能逐次逼近型A/D转换芯片AD7492BRU-5,最大转换速率为1.25×10次/s,具有12位的并行数据输出接口,并且具有三态功能,能够满足系统采样要求。

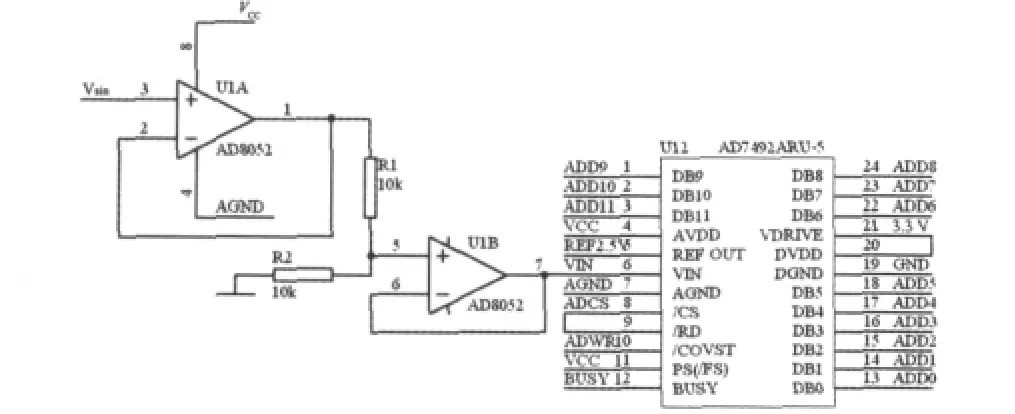

由于AD7492BRU-5的基准电压为2.5 V,而输入的模拟信号范围为0~5 V,因此在模拟信号进入AD转换器之前还需要对信号进行适当的调理,调理电路如图2所示。采用两个10 kΩ电阻对输出的模拟信号进行分压,使其范围满足A/D转换器的输入要求,并通过电压跟随器进行输出,信号不会失真。

图2 AD转换器连接电路

2.2 FT245接口电路

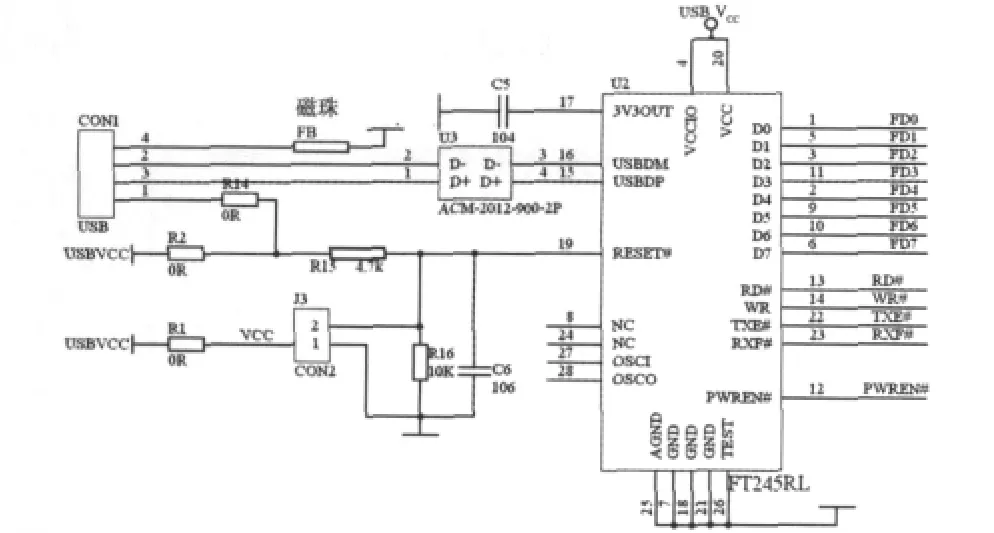

本系统中FPGA发送的滤波数据通过USB接口回传给上位机,上位机读取USB的数据,并对数据进行存盘。USB接口电路采用FTDI公司的FT245RL作为USB接口芯片实现上位机与FPGA的数据通信。FT245RL无需编写固件程序,可以使用FTDI公司提供的驱动程序,并且兼容USB1.1及USB2.0协议。USB连接电路如图3所示,该电路中数据传输线接一个共模电感ACM-2012-900,当传输差分信号USBDM和USBDP上有共模干扰时,由于共模信号产生磁场叠加,在共模电感上形成高阻抗,从而达到滤除共模干扰的目的。USB口接地端接一个磁珠,这样连接可以更好地防止电源不稳对数据传输的干扰。USB接口从FPGA读取数据,FPGA内部只要判断到FIFO中产生半满信号,就将数据传输到USB接口,最终利用上位机进行读取。

图3 FT245连接电路

3 FIR滤波器程序设计

本设计采用Xilinx公司XC3S400的FPGA进行程序验证,XC3S400是高密度的可编程逻辑器件。它的主要特点包括具有最小5 ns的引脚到引脚的逻辑时延,全局时钟最高引脚最高输入频率为66 MHz,内核用1.2 V供电,I/O口可设置在3.3 V工作。该器件具有丰富逻辑的资源,包括16个MULT18×18SIO,可以进行大量的乘法运算[8]。

FIR滤波器程序主要由采样模块、乘法器模块、累加和模块组成,采样模块功能是采集60个采样值、并把滤波系数输出到乘法器与采样值进行相乘。乘法器模块主要功能是对60个采样值和60个滤波系数进行相乘,所得的相乘结果输入累加器。累加器就是将输入的60个结果进行累加,得到36 位的滤波结果[9-10]。

3.1 采样模块

采样模块主要是对AD转换后输出的值进行采样,本设计中采样率为10 kHz,也就是AD的采样率为10 kHz,而滤波器对AD转换后输出的值的采样率也是10 kHz,它们的实现在程序上是同步的。在AD输出模块当中,每当数据转换完成输出时,会产生一个rdy上升沿信号,采样模块接收并辨别rdy上升沿信号后接收第一个数据,并把第一个滤波系数输出到MULT18×18SIO乘法器,同时给乘法器CLK端产生一个上升沿信号,启动乘法器进行相乘,相乘结果时间极短,所以可以实现高速相乘运算。

采样模块利用VHDL语言进行编写,利用状态机实现,在模块中采用4个状态来实现采样和滤波,第1个状态为采样,只要判断rdy上升沿信号就利用寄存器进行采样,并给寄存器赋值;第2个状态取出对应的滤波系数;第3个状态为产生乘法器时钟clk,且计数器counter加1;第4个状态判断计数器是否加到60,如果是则跳出采集,输出滤波结果,其采集和控制流程图如图4所示。

图4 采样模块工作流程图

采样模块当中还包括60个滤波系数,滤波器系数由Matlab产生,Matlab中FDATool(Filter Design& Analysis Tool)是Matlab信号处理工具箱专用的滤波器设计分析工具,操作简单、灵活,可以采用多种方法设计FIR滤波器。本文设计的FIR滤波器为60阶,采样率为10 kHz,截止频率为200 Hz的FIR低通滤波器,通带内纹波抖动为1 dB,阻带下降60 dB,并将其系数量化成16 bit后保存到COE文件中。本设计当中滤波系数扩大32767 倍,具体的量化过程如下:

设滤波系数浮点数h(n)为xn,最大系数为xmax,量化结果为zn,则

量化后的数据为10进制数,需转化为二进制数,并将十进制的负数转化为二进制补码形式才可以用于乘法器进行相乘。在采样模块当中,定义了一个可以存60个系数数组的寄存器,FIR滤波器系数就存在于60个数组当中,在运算中可以灵活取出滤波系数进行相乘。

3.2 乘法器

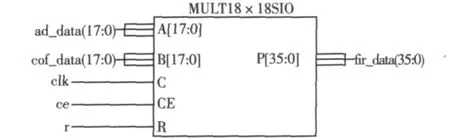

Xilinx FPGA开发环境软件自带的18位乘法器模块MULT18×18SIO如图5所示,该乘法累加器A(17:0)为AD转换后的数据输入端口,B(17:0)为滤波系数输入端口,C端口为乘法器时钟clk输入端,上升沿有效,CE为使能端高电平有效,R端为复位端低电平有效,P(35:0)为滤波器数据输出端。因为MULT18×18SIO乘法器为FPGA内部自带的硬核资源,可以直接调用,因此几乎不占用任何FPGA资源,并且可以提高乘法速度,只要在clk端给予一个上升沿就可以对其操作,使用起来方便、快捷。

图5 MULT18×18SIO乘法器

3.3 累加和模块

累加和模块主要对乘法结果进行累加,在累加模块中定义一个36位的寄存器,在累加上升沿脉冲到来时对乘法器输出的结果进行累加,一共进行59次累加,累加后的结果送入36位数据拆分模块,拆分成5 byte的数据压入FIFO进行发送,上位机通过FT245读取到滤波数据。

4 试验验证

针对FIR滤波器电路系统,设计了一个专门与配套USB接口FT245通信的软件,该软件能读取USB数据,并把USB数据保存在以DAT为后缀名的文件中。用该软件对该数据进行还原转化,即可得到其电压值,并能通过软件把结果显示出来。

用信号发生器同时给滤波器系统发送频率为100 Hz(小于200 Hz)和250 Hz,幅值为0~+5 V正弦波输入信号,正弦波信号经过信号调理及AD转换后由FPGA进行FIR低通滤波,最终通过USB接口将数据传输到计算机的上位机当中。读取到的滤波数据如图6所示,图中阴影部分为一个滤波数据值007F00A59F,转化为电压值过程如下:007F00A59F转化为十进制数,得到 N=2130 748831 ,由量化过程得到传递值f=524062 (32767 除以最大系数得到),则AD输出值x=N/f=4065 ,那么电压值V=(4065 /4095 ×2.5)V=2.48 V,则输入电压值Vin=(2.48×2)V=4.96 V。

图6 DAT文件的FIR滤波原始数据(截图)

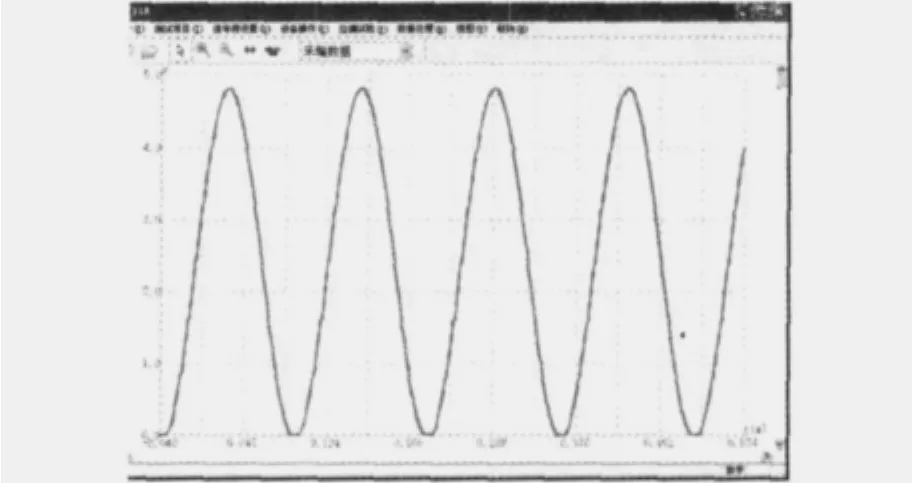

根据以上转换关系,利用上位机软件对读取到的数据进行曲线绘制,所得到的曲线为0~+5 V正弦波,如图7所示。由试验数据可知,频率大于200 Hz的信号幅值经过滤波器后受到衰减,不能通过FIR低通滤波器,低于200 Hz的信号却能顺利通过滤波器,可见所设计的滤波器满足要求。

图7 上位机软件显示的滤波后的波形(截图)

5 小结

试验结果表明,基于FPGA乘法器的FIR滤波器在采样控制、数字信号处理等方向,相比传统FPGA的FIR滤波器设计具有简单、快捷且有更高的执行效率和速度的特点。在该设计当中,FPGA的资源占用率只有10%,留有足够的资源以设计其他逻辑电路功能。基于FPGA乘法器的FIR滤波器高速、高灵活性的优点,使其可广泛应用于高速数字信号处理领域。

[1]李受明.FIR数字滤波器在雷达信号处理中的应用[D].西安:西安电子科技大学,2007.

[2]朱义胜,董辉.信号处理滤波器设计[M].北京:电子工业出版社,2004.

[3]王金明,张雄伟.FIR滤波器的优化设计与硬件实现[J].电视技术,2003,27(3):19-21.

[4]陆宇鹏,邱宏安,田多华,等.基于FPGA的数字滤波器的设计与实现[J]. 电声技术,2008,32(5):23-25.

[5]虞露,李儆,冯兴光.大规模可编程逻辑器件(FPGA)开发系统电源设计研究[M].西安:西安电子科技大学出版社,2007.

[6]从玉良,王宏志,赵晓明.数字信号处理原理[M].2版.北京:电子工业出版社,2009.

[7]蒋垒,王昌林,许冲.基于FPGA的FIR数字滤波器算法实现[J].船舶电子工程,2006,26(1):151-156.

[8]李云松,宋锐,雷杰,等.Xilinx FPGA设计基础[M].西安:西安电子科技大学出版社,2008.

[9]徐以涛,王呈贵,王金龙.基于DA算法的FIR滤波器硬件实现[J].解放军理工大学学报:自然科学版,2003,4(3):22-25.

[10]胡广书.数字信号处理:理论、算法与实现[M].2版.北京:清华大学出版社,2003.