简单用户电路话路测试电路的设计

王宝霆

摘 要:本文针对交换机工作特点,设计了一个简单的用户电路话路测试电路。该电路主要采用三个芯片:微处理器AT89S51、单路编译码滤波器MC145503和锁相环音频译码器LM567。文中着重介绍了各个芯片的应用引脚功能及其具体连接。这个话路测试器通过AT89S51的控制,可以完成对交换机用户电路的检测。

关键词:用户电路AT89S51LM567MC145503

中图分类号:TN97 文献标识码:A 文章编号:1674-098X(2012)07(c)-0034-03

1硬件电路的选取

1.1 微处理器AT89S51

AT89S51是美国Atmel公司生产的一种带4K字节闪烁可编程可擦除只读存储器的低电压、高性能CMOS 8位微处理器,具有体积小、重量轻、抗干扰能力强、可靠性高、开发较容易等特点。

在本设计中,采用AT89S51芯片来实现电路中的测试和控制功能。89S51与89C51相比在工艺上进行了改进,采用0.35新工艺,成本降低,而且将功能提升,增加了市场竞争力。

1.2 AT89S51在设计中所用到的引脚功能及连接

Vcc(40脚):接+5V电源;

Vss(20脚):接地。

RST/VPD(9脚):RST是复位信号输入端,高电平有效。

XTAL1(19脚):接外部晶体的一个引脚。在单片机内部,它是一个反相放大器的输入端。这个放大器构成了片内振荡器,当采用外接晶体振荡器时,此引脚应接地。

XTAL2(18脚):接外部晶体的另一端,在单片机内部接至内部反相放大器的输出端。若采用外部振荡器时,该引脚接收振荡器的信号,即把此信号直接接到内部时钟发生器的输入端。

P3口可作为一般的I/O口线,但更重要的用途是它的第二功能为:

P3.0 RXD串行输入口,(这里与LM567的8脚输出口相连,用来检验电路是否正常工作)

P3.1 TXD串行输出口,(电路中与继电器一端相连)

/VPP(31脚):功能为内外程序存储器选择控制端。当保持低电平时,只访问外部程序存储器。

2 集成锁相环音频译码器LM567

集成锁相环音频译码器LM567是美国国家半导体公司生产的56系列集成锁相环路中的一种,它设计精巧,电路简洁,良好的噪声抑制能力和中心频率稳定性,在各种译码电路中得到了广泛的应用。

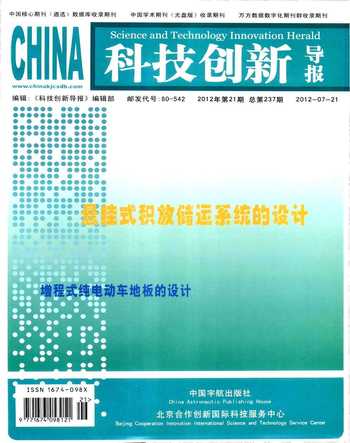

LM567的工作原理及引脚连接(图1)

工作原理:当音频译码器LM567工作时,由电压控制振荡器(VCO)驱动振荡器确定译码器中心频率,其锁相环内部电压控制振荡器产生一定频率的振荡信号,此信号连同引脚3输入的信号频率一起送入正交相位探测器进行比较,若连续输入的信号频率落在给定的通频带时,锁相环即将这个信号锁定,同时LM567的内部晶体管受控导通,引脚8输出端输出低电平。 LM567的引脚5输出内部振荡器的矩形信号,引脚6输出锯齿波脉冲,二者的频率都与内部振荡器的中心频率相同。

引脚连接:LM567的工作电压为4.75~9V,工作频率可达500KHz,静态工作电流仅8mA,推荐使用8V。故设计中为第4脚提供8V电源。第3脚是信号输入端,要求输入信号大于25mV。第8脚是逻辑输出端,它是一个集电极开路的晶体管输出,具有最大为100mA的电流吸收能力。第5、6脚外接的电阻、电容决定了IC内部的压控振荡器中心频率,fT≈1/1.1RC。第1、2脚通常是分别对地接电容,形成输出滤波网络和环路低通滤波网络,其中第2脚所接电容决定了锁相环路的捕捉带宽,电容数值越大,环路带宽越窄。

3 单路编译码滤波器MC145503

编译码滤波器是一种用于将语音数字化或还原的设备。它最初用于促进电话网中语音的交换和传输。MC145503是Motorola公司生产的PCM单路编译码滤波器。它采用CMOS技术,有可靠的低功耗性能,适合于复杂的超大规模集成电路设计,是用在数字程控交换机模拟用户接口电路及模拟中继电路中的主要芯片。

MC145503的芯片引脚及连接

VLS:在TTL应用中,VLS接数字地,与VAG一同接地。

VAG:模拟地输入输出。在双电源系统中(±5,±6等)VAG可外接到系统模拟地上。所有这部分的模拟信号包括噪声都是以VAG为参考,因此从VDD到VAG,从VSS到VAG都必须用分离电容(0.1μF)

TDC:发送数字时钟输入,RDC:接收数据时钟输入,它与TDC引脚相连,为传输与接收数据寄存器提供时钟。

TDE:发送数据使能输入,RCE:接受时钟使能输入。二者相连,作为使能控制

TDD:发送数字数据输出。与用户电路的RDD引脚相连,作为检验接收电路是否正常工作的通道之一

RDD:接收数字数据输入。与用户电路的TDD引脚相连,作为检验发送电路是否正常工作的通道之一

Mμ/A选择:μ/A律选择。将该引脚与VDD相连,即Mμ/A=VDD ,表示用零码抑制Mμ-255压扩D3数据格式

:省电输入,将该引脚与VDD相连,即=VDD,电路正常操作。

RxO:接收模拟输出。与LM567的3脚相连,作为其输入

Txl:发送模拟输入,+TX:正TX放大器输入,-TX:负TX放大器输入。这些引脚通过外接电阻来调节进入放大器端口信号的输入增益。其电阻阻值应该在10K范围内,这里设置+TX无效,它内接到VAG。

在该±5V的双电源供电系统,其显著电源供应分布是:VDD=+5V,VSS=-5V,VLS=0V(关于TTL逻辑电平的数字地),VAG=0V作为系统模拟

4 系统设计

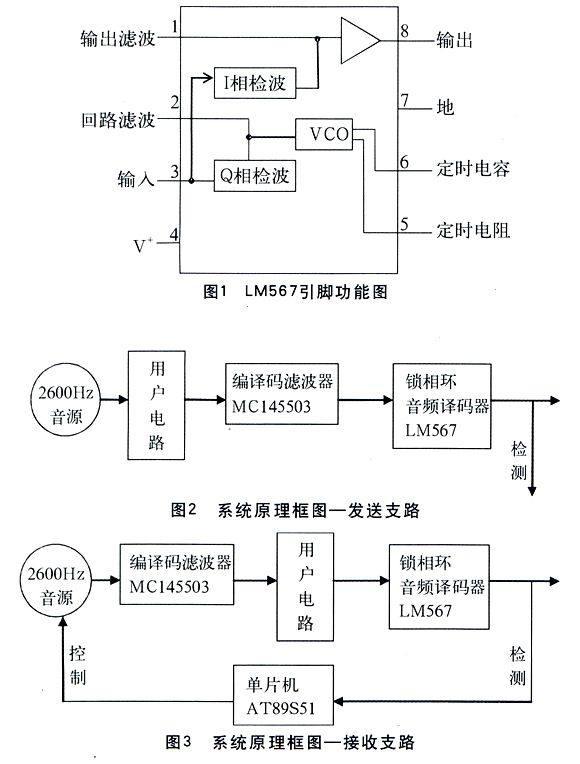

考虑到为了能够在测试时比较容易地检出是发送支路还是接收支路出现了故障,要分别对这两条支路进行测试。同时,为了简化电路设计,合理利用所选芯片,在硬件设计中采用单片机控制两个继电器K1,K2(单刀双掷),使测试电路能够顺序完成对发送和接收两路的检测。

系统原理框图(图2,3)

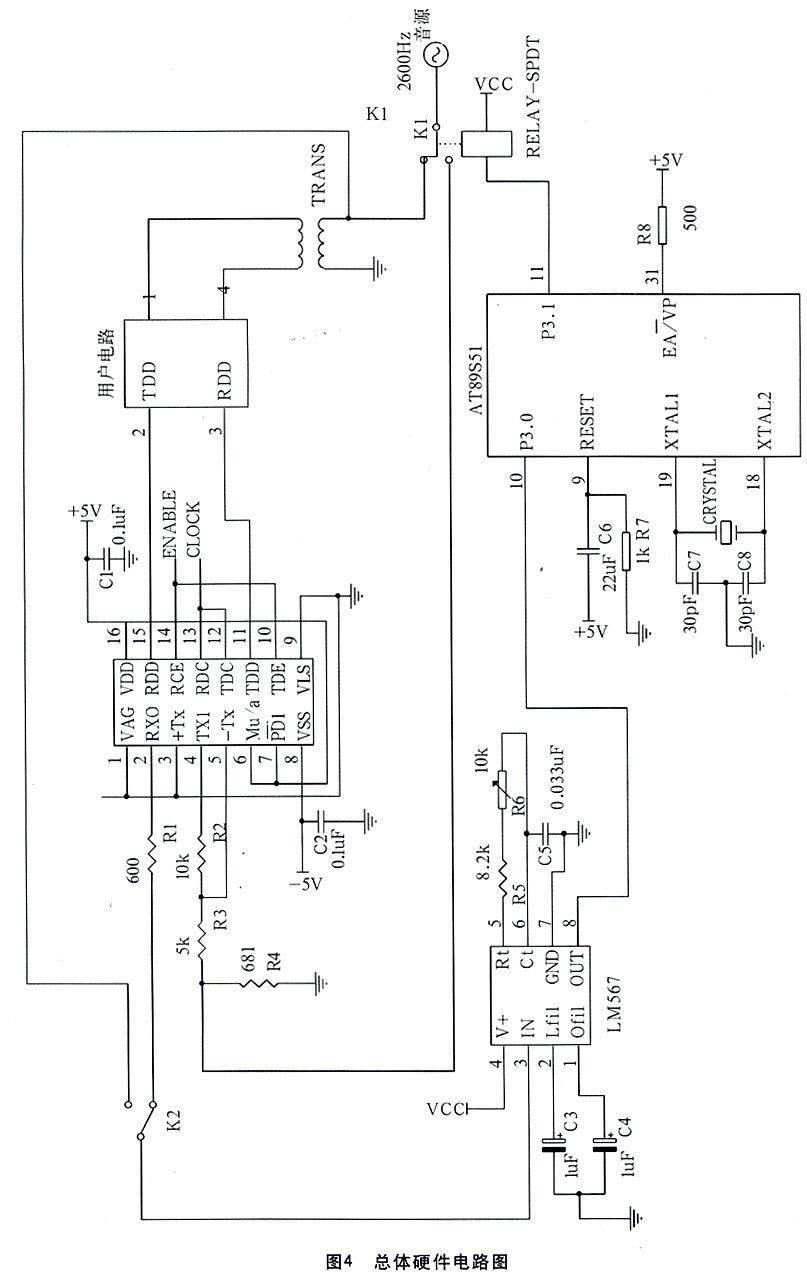

硬件电路设计

系统总体硬件电路设计如图4所示:

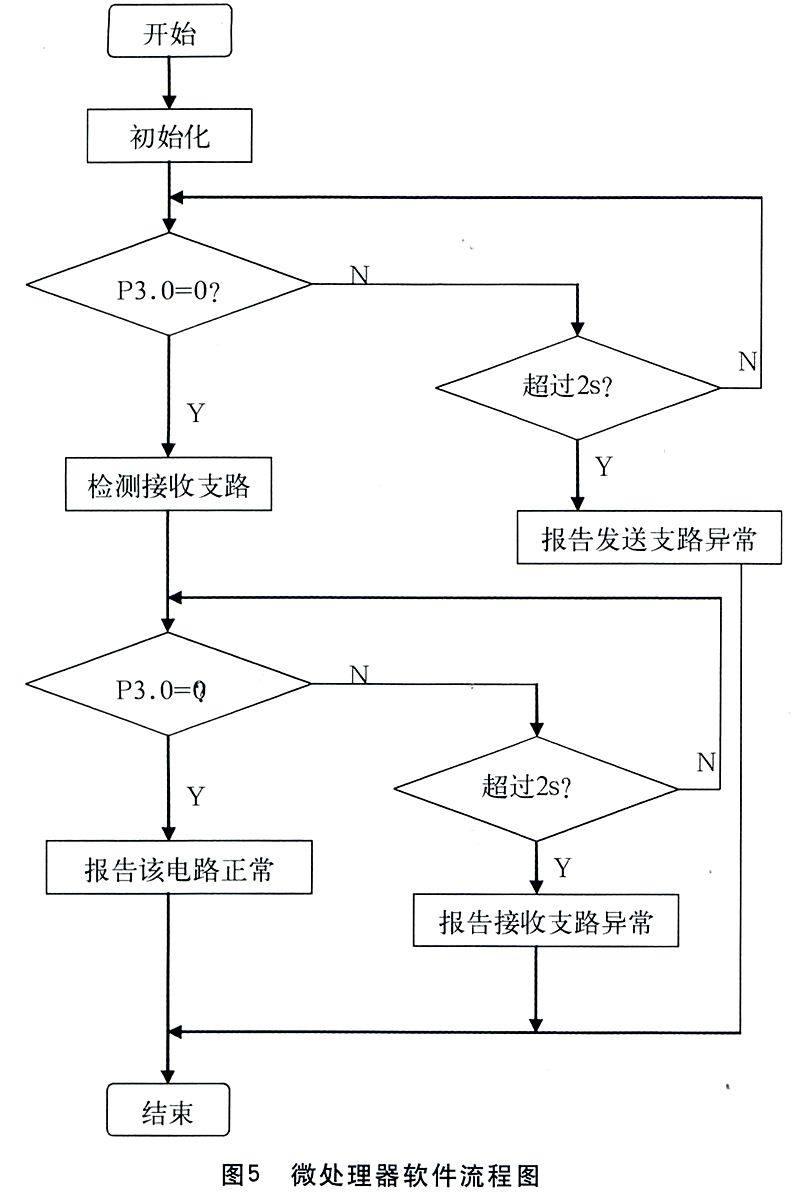

控制和检测功能的实现

对继电器的控制和对电平信号的检测功能是由单片机AT89S51来实现的。在设计中采用了89S51芯片的最小应用系统,即使用内部时钟方式和上电自动复位方式。开始测试发送支路后,芯片AT89S51首先要检测音频译码器LM567第8引脚输出的是高电平还是低电平,据此判断发送支路是否工作正常。若发送支路工作正常(即检测到低电平)则89S51向继电器发送一个控制信号,此时,接收支路的测试回路接通,然后89S51将继续执行检测功能,以确认接收支路是否正常工作。

单路编译码滤波器电路

上文已经比较详细地介绍了单路编译码滤波器MC145503,它可以完成话音的数字化、还原以及限制带宽等功能,可以满足本设计的功能要求。

音调译码锁相环电路

测试电路在工作前,要先将LM567的中心频率fT调到与音源的频率f0相同,即使fT=f0。在电路工作中,当接收(或发送)支路工作异常,LM567的3脚输入信号频率f将不在捕捉带宽范围内,8脚内部三极管截止,此时为集电极开路输出;当接收(或发送)支路正常工作,LM567的3脚输入信号频率f便进入了捕捉范围内,这时8脚内部三集管导通,输出变为低电平。即:

当f≠fT时,V8=“1”(代表悬空输出);

当f=fT时,V8=“0”。

在进行电路调试时,先调节RP1使LM567的5脚信号频率fT=f0,这时8脚应为低电平,在输入信号频率为其他值时,8脚应为高电平,证明电路可以正常工作。

软件流程图(图5)

5结语

综上所述,该电路针对交换机用户电路的工作特点和工作环境,充分利用了AT89S51、MC145503和LM567这三个主要芯片,尽量使用较简洁的电路完成了对交换机用户电路的发送和接收两条线路的测试,具备一定的实用性、灵活性和可靠性。

参考文献

[1] 叶敏.程控数字交换与交换网(第二版).北京:北京邮电大学出版社,2003.2-3,13-14,24-28.

[2] 张中荃.程控交换与宽带交换.北京:人民邮电出版社,2002.13-15.

[3] 郝建国,赵英志.通信集成电路大全.北京:人民邮电出版社,1996.280.

[4] 杨志忠.数字电子技术.高等教育出版社,2000.156.

[5] Communication Systems(Version 3),September,1999.32-3.