基于FPGA的DDS波形信号发生器的设计

郑黄婷,赖万昌,毛 伟

(成都理工大学 核技术与自动化工程学院,四川 成都 610059)

随着数字技术的飞速发展,使频率合成技术也跃上了一个新的台阶。传统的频率合成器,通常从一排晶体振荡器产生的各种频率通过开关进行频率混合,或者采用锁相(PLL)技术实现频率合成。与传统的频率合成器相比,DDS(Direct Digital Synthesizer)直接数字频率合成器具有低成本、低功耗、高分辨率和快速转换时间等优点,广泛使用在电信与电子仪器领域[1]。

DDS是一种可以将固定频率的时钟合成任意波形的频率合成器。其最基本的组成部分为:参考时钟源、数控振荡器与数模转换器[2]。DDS工作原理结构图如图1所示。参考时钟为整个系统提供稳定的时钟基准,且决定了DDS的频率精度。NCO(Numerically controlled oscillator)数控振荡器在时钟的控制下输出待生成波形的离散时间量化值。频率控制器通过改变频率字来改变波形周期。NCO生成的数字波形通过DAC后转化为模拟波形输出。最后将在数模转换过程中因零阶保持带来的频谱分量通过低通滤波器滤除,得到连续模拟波形。

NCO是DDS的核心部分,它是一个可以以离散值形式产生同步离散时间波形的数字信号发生器。相比其他振荡器来说,它具有准确度高、灵敏度高、稳定性好和可靠性高等特点。NCO由两部分组成:PA(phase accumulator)相位累加器与

1 DDS功能模块实现

图1 系统功能框图Fig.1 Function structure diagram of DDS

PAC(phase-to-amplitude converter)相幅转换器组成。PA在每个时钟采样点增加一定的频率控制值输出相位控制字。PAC使用PA输出的相位控制字索引波形查找表,输出对应采样点的幅度值。根据DDS的组成及工作原理,通过FPGA实现的DDS功能框图如图2所示。

其中K为频率控制字、P为相位控制字、fc为时钟频率,N为相位累加器的字长。相位累加器在时钟fc的控制下以步长K作累加,输出N位二进制码与相位控制字相加后作为波形ROM的地址,对波形ROM进行寻址,模式选择模块决定ROM输出的波形幅度码,波形幅度码再通过D/A和低通滤波即输出模拟的波形[3-4]。

相位累加器产生K点步长的相位增量。DDS方程为:Fout=K·fc/2N(0≤K≤2N-1),Fout为输出频率,fc为时钟频率。 当 K=1时,DDS输出最低频率(也即为频率分辨率)为:F0min=fc/2N,而DDS的最大输出频率由奈奎斯特采样定理决定,即F0max=fc/2;在实际运用中,为了保证信号的输出质量,输出频率不要高于时钟频率的33%,以避免混叠或谐波落入有用输出频带内[5-6]。因此,只要N足够大,DDS可得到很细的频率间隔。要改变DDS的输出频率,只要改变频率累加器产生的步长K即可。为了保证频率分辨率足够高,通常N的取值在24到64之间。

图2 系统功能框图Fig.2 Structure diagram of the system function

累加器由N位加法器与N位寄存器构成fc。每来一个时钟脉冲,加法器将频率累加器产生的K点步长与相位偏移量数据相加,作为波形ROM的寻址地址。相位累加器在时钟的作用下,进行累加。当相位累加器加满量时,就会产生一次溢出,完成一个周期性的动作。改变相位控制字P可以控制输出信号的相位参数。

以正弦波发生模块为例。首先将正弦波形一个周期的一定采样点的数据信息存于ROM表中,正弦查找表包含一个周期正弦波的数字幅度信息,每个地址对应正弦波形中0~360°范围的一个相位点。查找表把输入的地址相位信息映射成正弦波幅度的数字量信号,驱动DAC,输出模拟量。设相位累加器的位宽为N,时钟频率为fc,K是频率控制字,那么相位寄存器每经过2N/K个fc时钟后回到初始状态,相应地正弦查询表经过一个循环回到初始位置,整个系统输出一个正弦波。正弦波逻辑功能仿真图如图3所示。三角波、锯齿波发生模块原理和正弦波发生模块发生原理类似[7-8]。

DDS产生占空比可调的方波的方法,一种是利用上述产生正弦波的原理,在ROM表中存入方波对应占空比一个周期的方波采样数据,再根据相位累加器与相位控制字共同产生的地址对ROM表进行寻址,输出相应的波形的幅度值,这种方法需在ROM中存入大量的方波数据表,占用ROM资源,不可取;另一种是对应占空比的波形从控制器单片机或DSP写入RAM中,DAC在时钟的控制下,同时由计数器不断地改变地址,将数字信号转换为模拟信号输出。控制器中需存放伪随机数产生器,再由软件对输出波形进行控制,这种方法比原来电路较为复杂,体积大。

图3 仿真波形Fig.3 Diagram of waveform simulation

在本设计中,采用了一种节省资源的简便方法,即利用正弦数据查找表,采用基于比较器实现方波占空比可调的功能。

2 波形输出模块

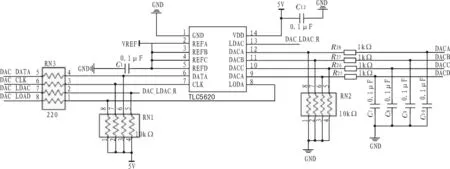

设计选用德州仪器的TLC5620。其中11位的命令字包括8位数据位,2位DAC选择位和1位范围位,后者用来选择输出范围是1倍还是2倍。DAC寄存器采用双缓存,允许一整套新值被写入设备中。通过LDAC实现DAC输出值的同时更新。数字量的输入采用史密斯触发器,从而避免了高噪声。D/A电路连接如图4所示。

图4 TLC5620电路连接图Fig.4 Diagram of TLC5620 hardware system

3 参数选取

设计中ROM查找表的地址位宽选择D=9,寻址范围可达29=512个点;设计采用fc=50 MHz的系统时钟,累加器的位宽N=32,由此计算当时K=1,DDS输出最低频率F0minN=fc/2N=50 M/232=0.011 6 Hz;最大频率 F0max=fc/2=50 M/2=25 MHz,然而此时每周只采样2点,难以保证输出精度,为保证输出精度可以通过增加采样点来实现。

4 结 论

本设计实现了正弦波、三角波、方波等基本波形的输出,并实现了一定的调制功能。设计比用集成芯片控制DDS直接合成信号的发生器电路更简单,信号更稳定,成本也较低,且灵活性好,提高了设计效率。

[1]潘松,黄继业.EDA技术实用教程[M].北京:科学出版社,2006:28-32.

[2]姜威.实用电子系统设计基础[M].北京:北京理工大学出版社,2008:70-210.

[3]唐建东.基于FPGA的任意波形发生器设计与实现[J].电子技术,2010(5):37-38.TANG Jian-dong.Design and implementation of arbitrary waveformgenerator based on FPGA[J].Electronic Technology,2010(5):37-38.

[4]Leary P,Malobertj F.A direct digital synthesizer with improved spectral performance[J].IEEETransactions on Communications,2009,39(7):1046-1048.

[5]SHU Yun-shan,SONG B S.A 15-bit linear 20-MS/s pipelined ADC digitally calibrated with signaldependent dithering[J].IEEE Journal of Solid-state Circuits,2008,43(2):342-350.

[6]Joukov.A direct digital synthesizer with a tunable error feedback structure[J].IEEE Transactionson Communications,2007,45(4):274-278.

[7]吴庆天,赵国庆.基于FPAG的可配置内容查找表的设计与实现[J].新特器件应用,2009,11(1):17-19.WU Qing-tian,ZHAO Guo-qing.Design and implementation of configurable content look-up table base on FPGA[J].Elect-ronic Component&Device Applications,2009,11(1):17-19.

[8]夏文宇.Verilog数字系统设计教程[M].北京:北京航空航天大学出版社,2003:48-121.