大容量数据存储器设计与实现

柴若楠,张景芝,和志强

(河北经贸大学信息技术学院,河北石家庄 050061)

大容量数据存储器设计与实现

柴若楠,张景芝,和志强

(河北经贸大学信息技术学院,河北石家庄 050061)

介绍了一种大容量数据存储器的设计方法,该存储器以高集成度FPGA为控制核心、以大容量SDRAM为存储介质,利用网络传输接口,实现了大容量数据的快速、实时、高效存储。

存储器;SDRAM控制器;FPGA;Verilog

随着科学技术的发展,通讯、航天等领域对数据采集系统的要求越来越高,不仅要求较高的采集精度和采集速率,还要求采集设备网络化及大容量数据存储。为此,笔者设计了大容量数据存储器,具有简单、可移植及灵活的特性。可广泛应用到多种嵌入式系统中,大大缩短开发周期,具有很强的市场竞争力[1]。

1 存储器设计

整个存储器设计采用64Mbit的SDRAM(同步动态随机存储器)作为存储介质,与传统的SRAM、FIFO等相比,其存储容量大、价格便宜、读写速度快。但是,SDRAM的接口复杂,需要相应的控制器支持。笔者通过使用Verilog语言对FPGA芯片进行设计,实现SDRAM控制器。

1.1 存储器设计总体思路

存储器总体结构框图如图1所示。存储器设计采用了ALTERA公司的CYCLONEII系列的EP2C5Q208芯片,SDRAM使用三星公司的K4S641632芯片,SDRAM控制器使用硬件描述语言Verilog实现。在网络环境下的数据采集系统中,数据量非常大,数据通过网络传输接口,经过前端处理及A/D转换后需要在SDRAM中缓存,通过设计SDRAM控制器实现对SDRAM初始化、SDRAM刷新控制以及数据读写控制。

1.2 存储器设计

存储器设计中SDRAM存储有复杂的时序要求,需要设计SDRAM控制器对其进行控制。

1.2.1 SDRAM常用命令

三星K4S641632芯片存储容量为64Mbit,数据宽度为32位,工作时钟为133MHz,所有输入都以系统时钟的上升沿为基准[2]。SDRAM命令控制信息见表2,各命令功能如下。

(1)无操作:当SDRAM被片选,且处于空闲或者等待状态时,这个命令阻止意外的命令被寄存。

(2)模式寄存器设置:初始化时通过装载A0~A11进行模式寄存器设置。其中A11~A10是用户保留位;A9用来配置写突发模式;A8~A7是操作模式,通常为“00”,代表标准操作模式;A6~A4设置CAS延迟时间;A3决定突发操作模式是顺序还是交替;最后的三位A2~A0用来配置突发长度。如表1所示。

图1 数据存储器总体结构

表1 工作模式寄存器

(3)激活:以三星公司的这款K4S641632芯片为例,其内部分为4个Bank,该命令用于选择某一空闲Bank中的一行。该操作经过t RCD个周期后进行读或写操作。

(4)预充电:即L-Bank关闭现有工作行,准备打开新行的操作。由于SDRAM的寻址具有独占性,同一时刻每个Bank内只能有一行被激活,如果需要访问某一Bank内的另外一行,就必须使用预充电命令将当前打开的行关闭[3]。在发出预充电命令之后,要经过一段时间才能允许发送行有效命令打开新的工作行。

(5)自动刷新:动态RAM的本质决定了必须定时对SDRAM进行刷新[3],刷新有固定的周期,刷新过程中,所有L-Bank都停止工作,依次对所有行进行操作。目前公认的标准认为,64ms是存储体中电容的数据有效保存期的上限,每次刷新所占用的时间为9个时钟周期。64ms之后则再次对同一行进行刷新,如此周而复始进行循环刷新。

(6)读/写操作:某行被激活后,通过此命令来开始一段读操作或写操作。

表2 SDRAM命令控制信号

1.2.2 SDRAM工作流程

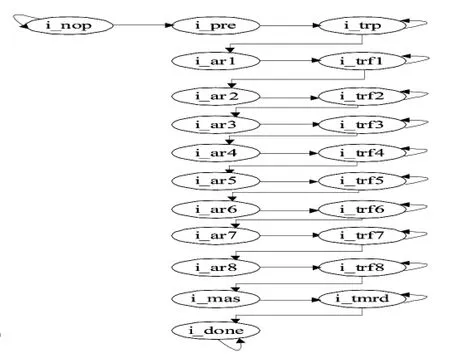

(1)SDRAM初始化时的操作。系统上电,将cke置高并给出Nop命令,此时处于i_nop状态。保持上述状态200μs后,跳转到i_pre状态,发出预充电命令,接着跳转到i_tRP等待状态,经过t RP时间后,即完成对所有L-Bank预充电。然后状态跳转到i_AR1,发第一次刷新命令,再在i_t RF1等待t RF时间后发第二次刷新命令。依次执行8次刷新。接下来转到状态i_MRS,进行模式寄存器设置。等待t_MRD时间后初始化完成。初始化完成后,SDRAM处于i_done状态,读、写和刷新操作准备就绪。初始化状态转移如图2。

(2)SDRAM正常工作时的操作。SDRAM初始化完成后,即进入w_idle状态。等待访问请求。控制器接到刷新请求信号后,即进入刷新w_AR状态,经过t RFC时间后,刷新完成,进入w_idle状态,等待读写请求。当读写请求到来时,进入w_ACTIVE激活状态,经过t RCD时间后,进入w_READ或者w_WRITE状态。当进入w_READ后,需要经过tCL时间后才进行读操作。w_ WRITE则直接进入写操作,命令发出同时数据线上输出待写的第一个数据。

需要说明的是(1)在SDRAM中只有一条指令在执行,先到的指令先执行。其他指令到来时等待前一条指令执行完;(2)读写指令与刷新请求同时到来时,刷新操作先执行,这是防止没有及时刷新而丢失SDRAM内容。SDRAM工作流程图如图3所示。

图2 SDRAM初始化状态转移图

图3 SDRAM工作流程图

2 存储器的实现

根据SDRAM的指令操作特点将SDRAM控制器划分为状态控制模块、命令模块和数据读写模块[4]三个主要模块。

2.1 SDRAM状态控制模块的实现

sdram_ctrl是SDRAM状态控制模块,该模块主要完成SDRAM的上电初始化以及刷新控制、读写控制等状态的变化[4]。

2.2 SDRAM命令模块的实现

sdram_cmd是SDRAM命令模块,该模块根据sdram_ctrl模块的不同状态指示输出相应的SDRAM控制命令和地址。

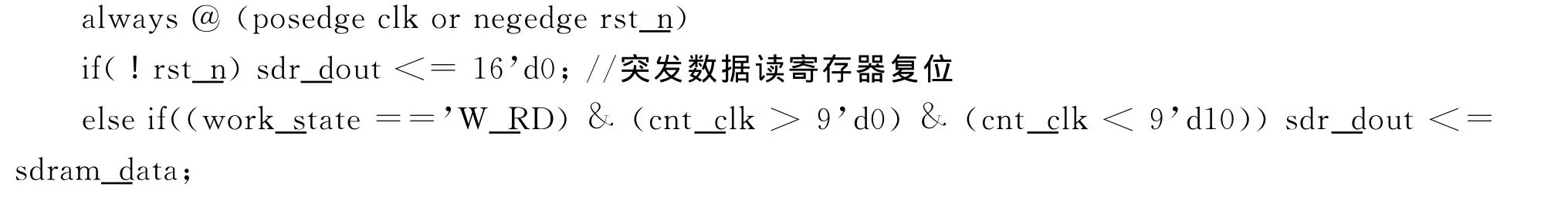

2.3 SDRAM数据读写模块的实现

sdram_wr是SDRAM数据读写模块,该模块同样是根据sdram_ctrl模块的状态指示完成SDRAM数据总线的控制,SDRAM的数据读写都在该模块完成。

3 结束语

本文中的存储器设计采用了FPGA芯片、Verilog编程语言和QuartusII开发及Modesim仿真工具,已应用到数字存储示波器上。仅仅通过改变存储器的个别参数就可以将其移植到不同的嵌入式系统中,大大缩短开发周期,具有广泛的应用价值及强大的市场竞争力。

[1]李燕萍.基于FPGA的连续存储系统实现[D].北京:首都师范大学,2007:1-4.

[2]SAMSUNG corporation.K4S641632E DATASHEET.2003.

[3]段然,樊晓桠,张盛兵,沈戈,梁婕.基于状态机的SDRAM控制器的设计与实现[J].计算机工程与应用.2005,17:111-112.

[4]吴厚航.深入浅出玩转FPGA[M].北京航空航天大学出版社.2010.

[5]ddhttp://www.sumsung.com/products/Semiconductor/Sync_AsyncDRAM/SDRSDRAM/Component//64Mbit/K4S641632E.htm.

The design and implementation of large-capacity data storage

CHAI Ruo-nan,ZHANG Jing-zhi,HE Zhi-qiang

(CollegeofInformationTechnology,HebeiUniversityofEconomicsandBusiness,ShijiazhuangHebei050061,China)

In this paper,design method of the large-capacity data storage is discussed.It uses FPGA as the kernel controller and SDRAM as the storage media.Through the network interfaces,the fast,realtime and efficient storage of the large-capacity data is achieved.

Storage;SDRAM controller;FPGA;Verilog

TP333

:A

1001-9383(2011)03-0061-05

2011-06-30

河北省应用基础研究计划项目(10963529D)、河北省高等学校科学技术研究项目(ZD2010213)

柴若楠(1987-),女,硕士研究生,主要研究方向:高速数据采集技术.