基于FPGA的伺服驱动器分数分周比设计与实现

刘继磊,孙 静,王 冰,祝恒洋,俞 帅

(1.西北工业大学,陕西西安710129;2.西安微电机研究所,陕西西安710077;3.中船重工第704研究所,上海200031)

0 引 言

交流伺服电动机在各种数控系统中承担着重要的执行任务。为了实现对伺服电机的精确位置控制,要求转子的位置必须能够被精确的检测出来。增量式光电编码器作为角位移或角速率测量传感器,以其构造简单、机械寿命长、易实现高分辨率等优点,在现代交流伺服系统中已被广泛采用。在实际的工作中,增量式光电编码器往往与电机同轴安装,它输出有A、B、Z三相信号,其中A相和B相相位相差90°,Z相为每转只输出一个脉冲,用于基准点的定位。在实际应用中,经常需要对A相、B相正交脉冲按照一定的比例,即分周比进行分频。分频的难点在于:无论设定分周比是整数还是分数,分频后输出的Div_A相和Div_B相脉冲仍然要保持正交或近似正交。本文以对1 024线分频得到360线为例,提出一种基于FPGA的分数分周比实现方法。该方法采用硬件描述语言VHDL来实现,逻辑结构简单,程序的可移植性强,易于扩展,具有很高的实用价值。

1 正交脉冲

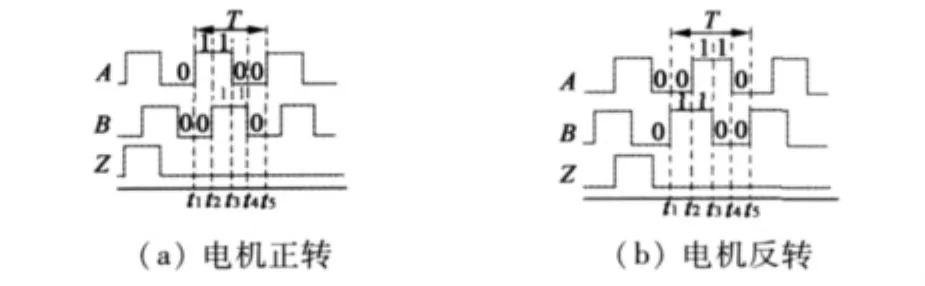

增量式光电编码器(又称光电码盘)发出的两路脉冲是正交的,即两路脉冲为相位相差90°的方波(A和B),如图1所示。其中,A、B两相信号的脉冲数标志电机轴所转过的角度,A、B之间的相位关系标志电机的转向,即当A相超前B相90°时,标志电机正转(图1a);当B相超前A相90°时,标志电机反转(图1b)。

图1 两路脉冲为相位相差90°的方波

2 分数分频原理

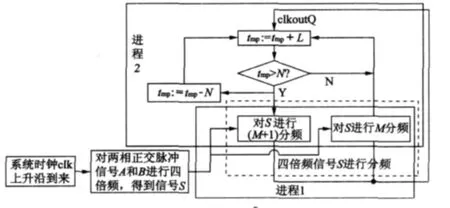

图2 四倍频信号S进行M的分数分频流程图

图2中:S是两相正交脉冲信号A和B的四倍频以后的信号;clkoutQ是上一次对增量式光电编码器的两路正交脉冲A和B的四倍频信号S进行分频所得到的信号,tmp是分数分子部分的累加值,其取值范围为0~2N的整数;进程1(下文中出现的process(s))是对两相正交脉冲的四倍频信号S进行M分频和 (M+1)分频;进程2(下文中出现的process(clkoutQ))是用来对具体何时进行哪种分频进行判断和控制;在硬件描述语言VHDL中,进程之间是并行执行的,即此处的进程1和进程2是并行执行的。

具体执行过程如下:(1)当系统时钟信号clk的上升沿到来时,对两相正交脉冲信号A和B的四倍频信号S进行M分频和 (M+1)分频;与此同时,(2)当clkoutQ的上升沿到来时,tmp的值增加L(分子),然后根据当前tmp值与N(分母)大小关系来判断和控制信号S下一次是进行M分频还是(M+1)分频:(a)当tmp的取值大于N(分母)时,S进行(M+1)分频,同时将tmp值减少N(分母),然后再增加L(分子),接着进行判断和循环;(b)当tmp的取值小于N(分母)时,S进行M分频,同时将tmp值增加L(分子),接着进行判断和循环。上述(1)和(2)两过程是同时进行的。本文要采用此方法,实现两相正交脉冲的的分频。

3 分周比的原理及框图

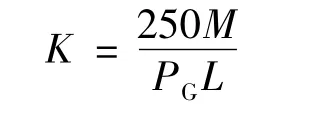

分周比是数控系统中一个很重要的概念,它是指伺服驱动器接收到来自伺服电动机轴上光电编码器的脉冲量与实际反馈到上位计算机数字控制(CNC)系统上脉冲量的比,可以按照如下公式进行计算:

式中:K为分周比;M为丝杠螺距;L为脉冲当量;PG为光电编码器线。国外的大部分伺服驱动装置一般都具有分周比的功能。具有分周比功能的伺服系统结构图如图3所示。

图3 带有分周比功能的伺服系统结构图

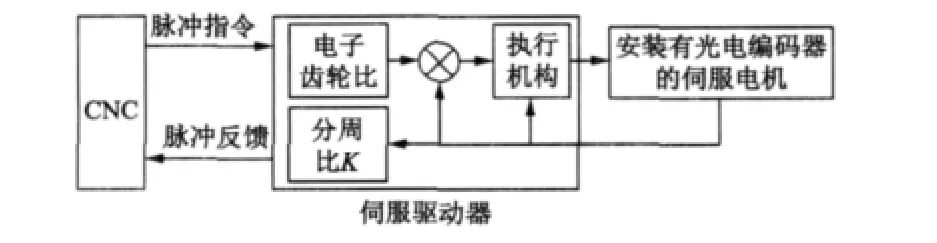

由于伺服驱动器反馈到计算机数字控制(CNC)系统的脉冲量一般采用正交脉冲序列,故分周比的实现比较困难,本文采用FPGA,通过硬件描述语言VHDL进行实现。分周比功能的具体实现结构如图4所示。

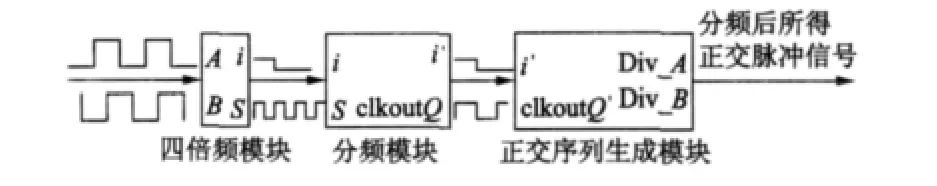

图4 分周比功能原理框图

由图4可以看出:分周比的实现需要3个功能模块:四倍频模块、分频模块和正交序列生成模块三部分。四倍频模块的输入为两路正交脉冲A和B,输出为方向信号i(通常也被称为鉴相信号)和四倍频后的脉冲信号S。分频模块可实现对脉冲信号S的分频(包括2分频和3分频等),它内部是一个增减计数器,根据输入的方向信号i进行增、减计数,正向计至设定的正阈值后输出一个脉冲和正方向信号,负向计至设定的负阈值后输出一个脉冲和负方向信号。当计数值在正负阈值之间时,即使电机方向发生变化,甚至抖动,输出方向信号i都保持不变。正交序列生成模块用输入脉冲沿触发内部状态机进行状态转换,根据输入的方向信号i判断要跳转的状态,从而产生正交信号和方向信号。

4 分周比的FPGA实现及仿真

本文采用硬件描述语言VHDL进行模块化程序设计。主要包括:四倍频模块,分频模块,正交序列生成模块三部分。这里重点介绍分频模块和正交序列生成模块。

四倍频模块:正交信号的四倍频方法有多种,本文主要采用:当系统时钟信号到来时,将两路正交脉冲A和B分别与其相差一个时钟周期的正交脉冲信号PA和PB进行异或,之后再相或,就可以得到四倍频脉冲信号S。方向信号i可以通过改变A和B的状态进行设置。

以上两进程是并行执行的。

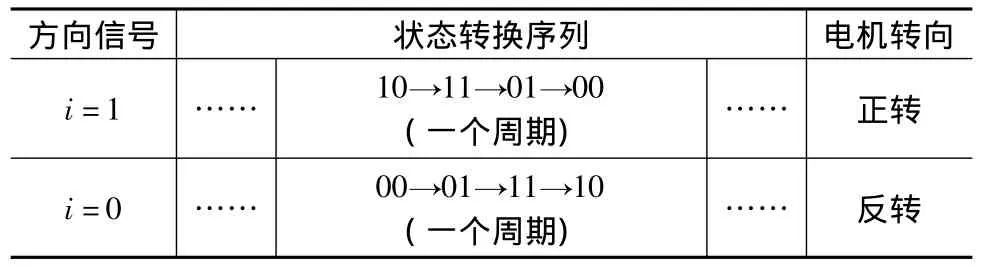

正交序列生成模块:用输入脉冲clkoutQ的上升沿触发内部的状态机进行状态转换,根据当前状态和方向信号i,跳到下一个状态。正交序列生成模块状态转换如表1所示。

表1 正交序列生成模块状态转换表

由表1可知:当方向信号i为正(i=1)时,按照10→11→01→00(一个周期)切换状态,产生Div_A相超前Div_B相90°的正交脉冲序列,此时伺服电机正转;当方向信号i为负(i=0)时,按照00→01→11→10(一个周期)切换状态,产生Div_B相超前Div_A相90°的正交脉冲序列,此时伺服电机反转。

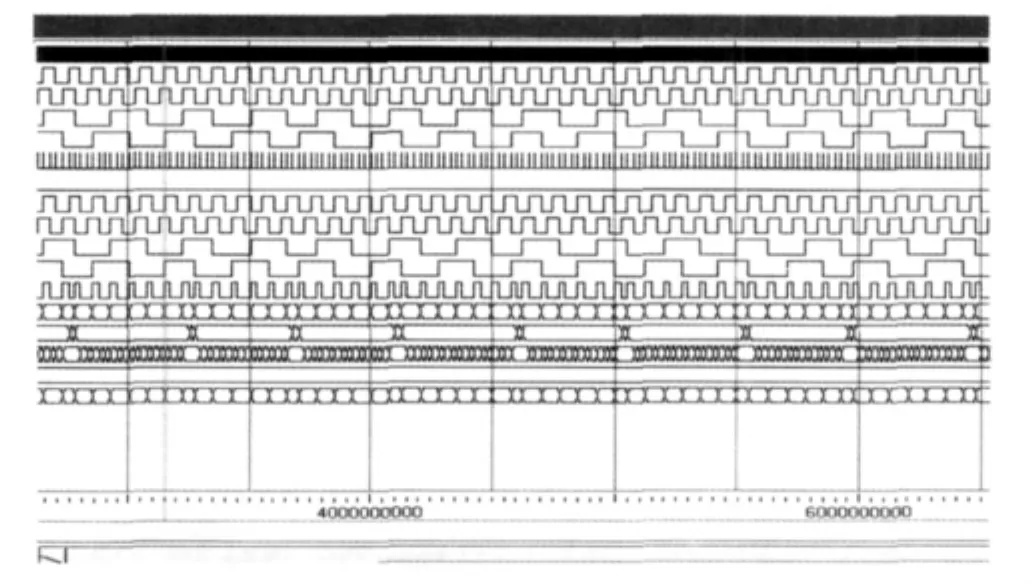

在Xilinx的开发环境ISE9.1i下进行VHDL程序设计,经过编译和分析综合,完全正确之后,利用专业软件ModelSim XE III 6.2c进行仿真,可以得到如图5所示的实验波形。

图5 分周比整体仿真实验波形

由图5可以看出:两相正交脉冲A和B经过四倍频后产生信号S和方向信号i;对S信号进行分频,即分频,产生clkoutQ信号;用clkoutQ信号的上升沿触发内部状态机进行状态转换,最终产生比较理想的两相正交脉冲序列Div_A和Div_B,并且其占空比仍为50%,完全能够满足全数字交流伺服系统的性能要求。

5 结 语

本文利用FPGA实现了伺服系统中分数分周比的功能,尤其是利用分周比的原理,通过编制VHDL程序,成功实现了两相正交脉冲的1 024/360分频,分频后产生的两相脉冲序列Div_A和Div_B完全正交,并且其占空比均为50%。在实际工作中,只要对程序进行修改,完全可以实现正交脉冲任意比例的分周比,具有较高的实际意义。

[1]张士雄,皮佑国.基于FPGA的伺服驱动器分周比设计与实现[J].现代电子技术,2009,32(13):121-123.

[2]李海春.FPGA/CPLD在交流伺服系统中的应用[D].武汉:华中科技大学,2008.

[3]蒋晶,蒋东方,高航.高可靠性增量式光电编码器接口电路设计[J].测控技术,2009(2):5-8.

[4]Galván E,Torralba A.ASIC implementation of a digital tachometer with high precision in a wide speed range[J].IEEE Trans.Ind.Electron,1996,43(6):655-660.

[5]容文杰.一种基于EPROM的时序电路设计方法应用[J].石家庄铁道学院学报,1998,11(4):39-44.

[6]胡超,方刚,王耀.增量式位移传感器信号的计算机检测[J].计量学报,1997,18(04):50-54.